数字逻辑综合工具-DC-05 ——环境约束

数字逻辑综合工具-DC-05

——环境约束

环境设置通常包含以下几个方面:

1、 Input drivers和transition times(设置驱动能力、转换时间,而不是一个理想信号)

2、 Capacitive output loads(设置要驱动的电容负载)

3、 PVT(一般选worst case)

4、 内部寄生RC(线负载模型)

输入驱动:

为什么要加输入驱动?

一般来说要从工艺库里面挑一个合适的单元去激励输入端口。如果不加驱动单元,DC就会认为输入的跳变是理想的,如果指定了驱动单元,输入就会有一个斜率,从而内部逻辑的延时会更准确(传播延时跟输入信号的transition time是有关系的)。

为了保证芯片能正常工作,一般会选择最坏情况的SS去做综合。

为输出的管脚建模:

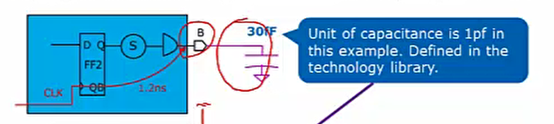

set_load [expr 30.0/1000] [get_ports B]

单位是在工艺库里给出的,通过list_lib看用的哪个工艺库, report_lib把lib的信息打出来

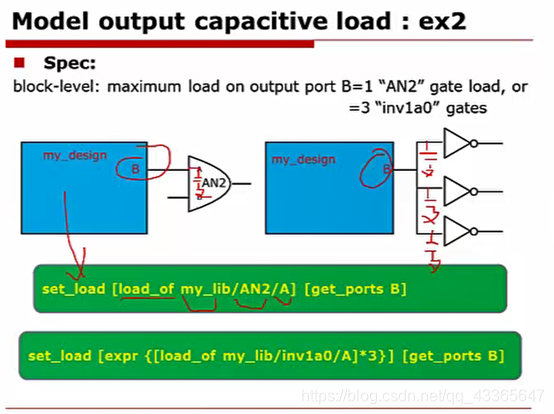

set_load [load_of my_lib/AN2/A] [get_ports B]

这边的my_lib是库,AN2是库单元,A是pin脚(是pin脚而不是port,port是跟design对应的,而pin是跟cell对应的)

含义就是:把这个库单元的这个引脚的电容拿出来,加载到B输出端口上

set_load [expr {[load_of my_lib/inv1a0/A]*3}] [get_ports B]

如果有多个fanout,可以用expr计算

【transition time 的影响:】

【设置input_port的转换时间】

set_input_trasition [get_ports ]

那么,如何知道transition time呢?

问他们搞模电的。

【driving】

set_driving_cell命令采用某个单元的输出,单元名用-lib_cell指定,如果有多个输出管脚,用-pin指定管脚名

【在不太清楚外部特点的情况下,如何处理load和drive?】

1、 选一个稍微弱一点的driver,但是不要过于保守,不要太弱

2、 对输入端口加限制,design内部,从输入端口到内部组合逻辑这一段,限制其fanout,即限制自身的输入电容,即使driver不那么强,也能驱动

3、 对输出端口来说,要估计电路需要驱动哪几个模块

Example:

1、记得要把clock端口干掉

2、注意第二段set_max_capacitance:要再约束一遍最大负载电容,Design Rule Check不能放松,因为这个是厂商的规定(最大电容、最大转换时间、最大扇出负载)

【PVT】

=>选择什么样的工作条件

list_library 查看当前所用的工艺库的名字(.db文件)

report_lib 给出工艺库的详细信息

(给出的信息里包含了PVT的信息和相应的condition的名字)

set_operating_conditions -max “WCCOM” (选择工作环境)

工艺库供应商一般会提供三个文件:

typical.db------>典型

wccom.db------>worst case

bccom.db------->best case

如果在你的工艺库中,只有一个工作条件,那就不用设置了。

【Parasitic RC】

WLM:线负载模型。需要选择一个合适的线负载模型。

比如说要生产比较小的,几万门的一个IC,就不用选择一个很悲观的模型。

模型的选择需要foundry厂的经验。

resistance、capacitance、area 都是单位长度的参数

WLM还提供了fanout 和length的关系

驱动一个负载的平均长度是14.15,因为不可能把所有的fanout都列出来,所以用slope计算(数值分析里的外推法)

【选择线负载模型】

set_auto_wire_load_selection false ;#把自动选择线负载模型给关掉

set_wire_load_model -name 8000000 ;#

【实操:】

上次没说完的:

40行:DC把设计读进来的时候转换成GTECH格式,把这个GTECH格式的东西给保存一下,下次就不用再转换了

设置驱动单元

最好设定一些变量,单元库名、线负载模型名、驱动单元、工作条件等等

注意观察添加负载的代码风格

set_isolate_ports后面会说

【设置工作条件】

设定工作条件、取消自动选择线负载模型、设置线负载mode、设置线负载模型

【list_libs】

【report_lib】

还有很长很长……

Tips:

写一个调用约束脚本的脚本

做重定向

把执行{source -echo -verbose fsm_moore.tcl}的执行信息放到log文件里面去

WORK_PATH是在dc_setup脚本里定义的

然后执行compile

(没有compile_ultra的license,只好用这个替代)

Tips:

通过remove_design -hierarchy可以把所有analyze都进来的文件给挪掉

【上节课剩的一些内容】

一般来说,将constraints放在一个单独的文件夹里面,后缀可以自己命名,比如.con/.tcl

【一步将dc启动且读入Tcl】

(-i选项让tee命令忽略中断事件)

看看约束加的对不对

【check_timing】防止某些路径没加约束

这些check和report可以通过重定向放到文件里面

【重定向命令】(synopsys官方文档解释:)

-echo -verbose 将tcl脚本里语句的过程信息打印出来

如果既要显示出来,又要写入到log文件里面,使用redirect命令,synopsys说明文档如下:

- 点赞

- 收藏

- 分享

- 文章举报

万里独行田伯光大侠

发布了18 篇原创文章 · 获赞 4 · 访问量 656

私信

关注

万里独行田伯光大侠

发布了18 篇原创文章 · 获赞 4 · 访问量 656

私信

关注

- 数字逻辑综合工具实践-DC-10——CDC约束

- 数字逻辑综合工具-DC-11——一些其它命令和综合之后的文件

- 数字逻辑综合工具-DC-09——关于timing的一些补充

- 数字逻辑综合工具实践-DC-08——静态时序分析(STA)

- 数字逻辑综合工具实践-DC-07 ——综合优化(二)和RTL coding 和DFT

- 数字逻辑综合工具-DC-06——综合优化过程

- 【转】dc综合工具启动文件 .synopsys_dc.setup

- 如何编写Xilinx ISE环境下的综合约束文件ucf

- DC时序_面积_环境变量约束

- DC综合环境的一些概念

- 微服务综合案例-05-业务逻辑实现

- mini6410基于linux2.6.36内核通过NFS启动根文件系统总结(一搭建开发环境——安装交叉工具连)

- (五)ubuntu环境搭建-工具

- 在windows下使用Cygwin模拟unix环境,并安装apt-cyg,repo等工具

- Linux 开发环境工具[zt]

- Python开发环境Wing IDE使用手册之搜索工具

- Android开发工具升级(Android Studio的环境搭建和项目构建)

- python环境搭建和开发工具的配置

- 【Linux开发技术之工具使用】配置VIM下编程和代码阅读环境 - gnuhpc - 博客园

- Linux开发环境必备十大开发工具