数字逻辑综合工具实践-DC-07 ——综合优化(二)和RTL coding 和DFT

数字逻辑综合工具实践-DC-07

——综合优化(二)和RTL coding 和DFT

主要内容:

1、 Pipeline优化

2、 RTL设计时的一些注意事项

3、 DFT简介

(DFT是后端里很重要的一步)

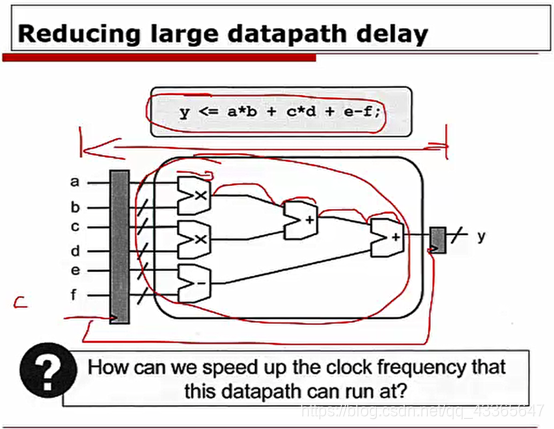

【流水线寄存器】

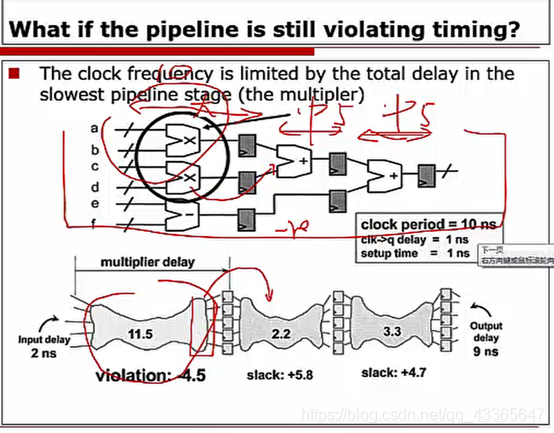

组合路径过长,timing不满足,可根据经验插入寄存器。

(三级流水线)

并不是拆的越散越好。

代价:DFF的面积和初始化的延迟。

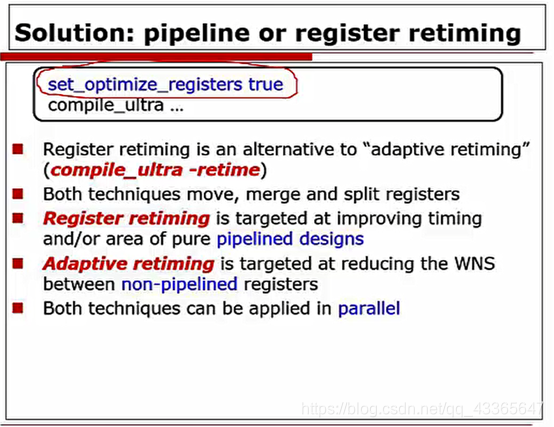

【set_optimize_registers true】

专门对流水线寄存器做优化的选项(必须要用Compile_Ultra)

(跟Retime很像)

把前一级的violation很后面的slack匀一下

set_optimize_registers 和 -retime 可以同时设置,set_optimize_registers 对流水线寄存器更专一。

!](https://img-blog.csdnimg.cn/20191023164954233.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzQzMzY1NjQ3,size_16,color_FFFFFF,t_70)

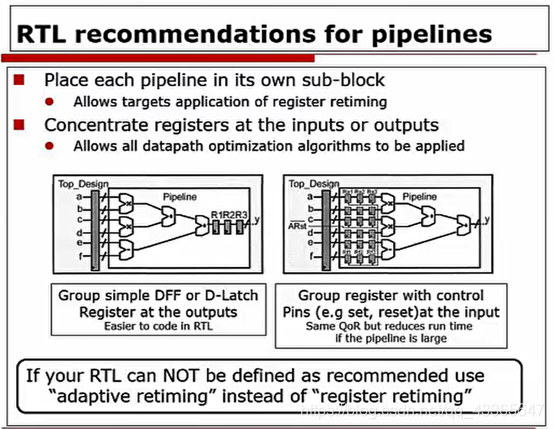

【pipeline怎么写?】**

左:组合逻辑堆一起,输出再堆一坨寄存器

右:输入堆一坨寄存器,组合逻辑堆一起

(比较省事儿的做法,也可以人为地插进去。)

(这种结构要用set_optimize_registers去调整,如果忘了加那个命令就完了(有可能写代码的人和做综合的人不是同一个))

另外:针对这些纯粹的Pipeline结构,只要控制信号做的好,reset端可以不要。

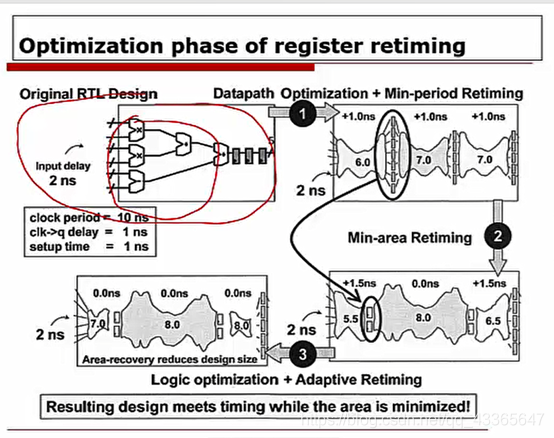

1、 插进去,做最小时序的优化

2、 做最小面积的优化

3、 逻辑优化(时序均衡)

v

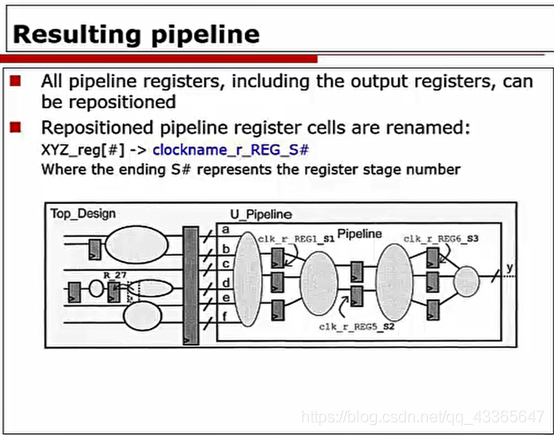

可以针对某一个设计去指定流水线寄存器的优化。

调整了之后,寄存器会重新命名,S#表示是流水线的第多少级

这些调整信息都会放入default.svf文件,交给后端的Formality,做形式验证。

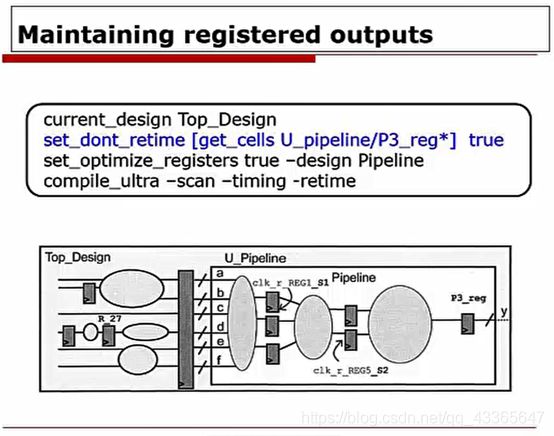

【set_dont_retime】

希望保持寄存器输出,timing budget会比较好算。

如果是组合逻辑输出,会引入毛刺。

要指定:哪一个寄存器不允许做retime的变动。

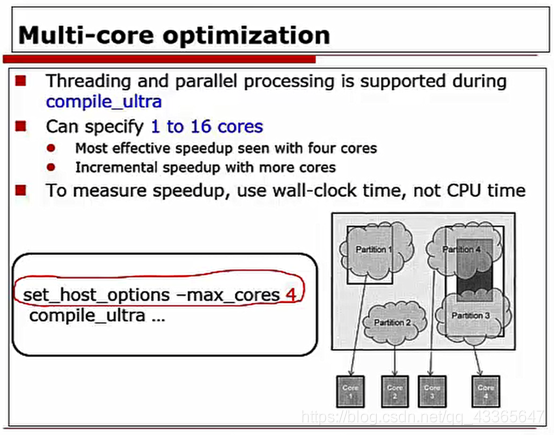

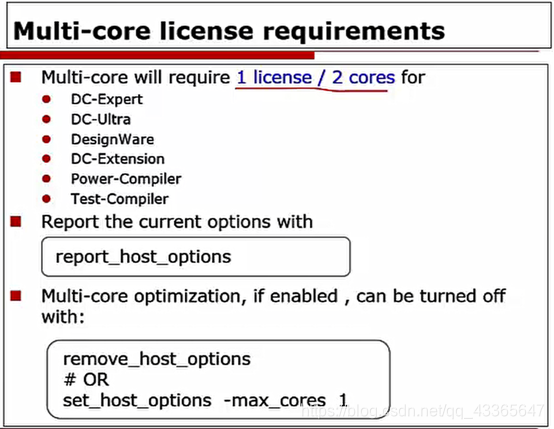

【多核】

服务器上可能由很多的核,为了做并行的工作,减少运行的时间,可以使用命令set_host_options -max_cores # 申请多核工作。

(只是申请,不一定能给到。)

report_host_options可以查看主机的核的个数。

更多的核需要更多的license,也就是说要付更多的钱……

多核工作也可以取消掉,设为1即可。

!](https://img-blog.csdnimg.cn/20191023165042776.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzQzMzY1NjQ3,size_16,color_FFFFFF,t_70)

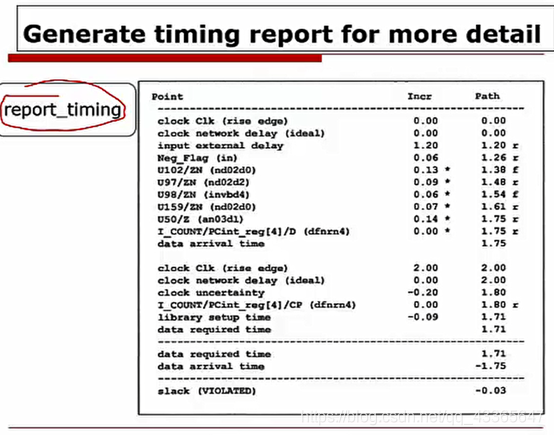

【综合后报告】

违规要关注几点:

1、 Timing违规:如果是后端的hold time violation,不是什么大问题,很容易被优化掉。如果是setup violation,如果优化不掉,需要人为手动地去解决。

2、 DRC的违规一定不能有

3、 面积违规的问题不大。

【report_timing】

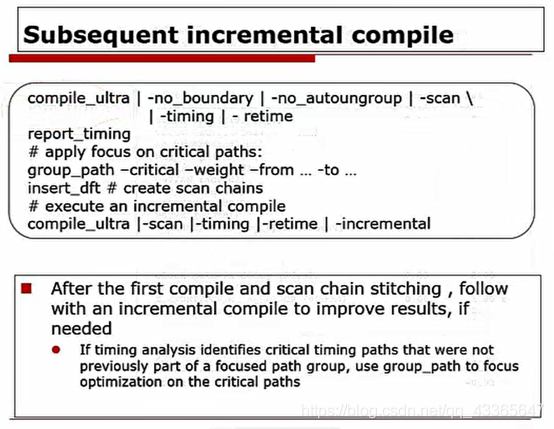

【增量综合】

1、第一次做综合:不要边界优化、不要打散模块、加入扫描链寄存器……

2、综合之后,查看一下timing有没有问题,查看一下violation是不是很大。

3、把最差的那条路经拿出来,权重设高一点。

4、-incremental做增量编译(在逻辑优化和gate level之间做循环优化,不会做结构级优化)。

【如果还是有violation怎么办】

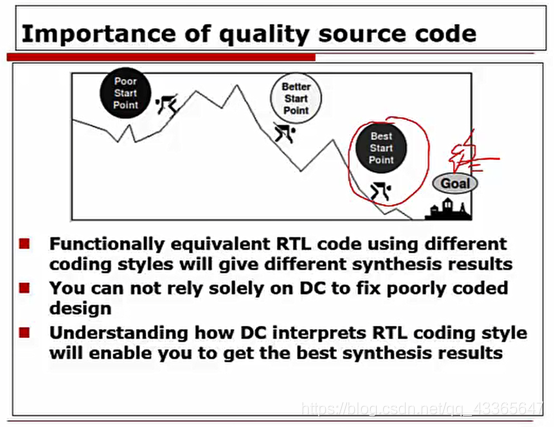

【Coding Style】

DC能做的其实没有多少,要想做好的电路,需要好的RTL设计。

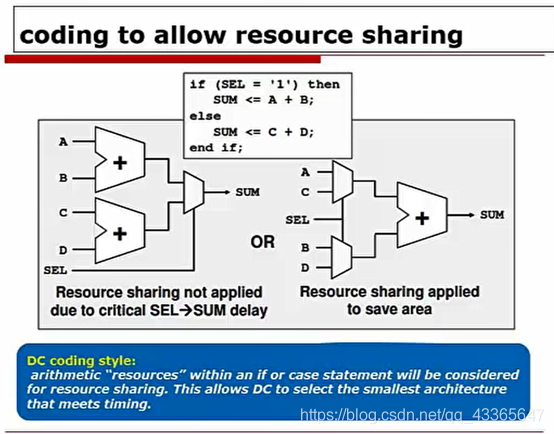

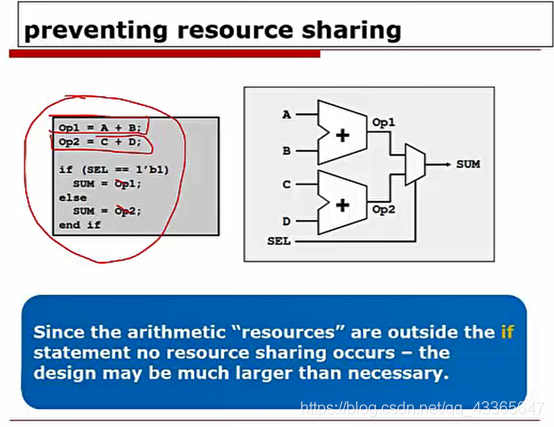

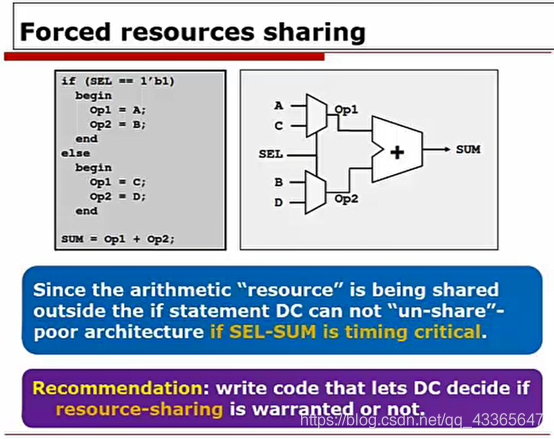

【资源共享】

节省面积。

但是DC不一定能帮你做这些优化。

比如SEL前面接了一堆逻辑,DC分析出来SEL的时序很差,从SEL到SUM是一条关键路径,这个时候DC不会把左边变到右边。

这么写,compile DC不会做优化,但是compile_ultra会!

(强制资源共享:先做选择、再做加法)

写代码的时候很容易想不起来…

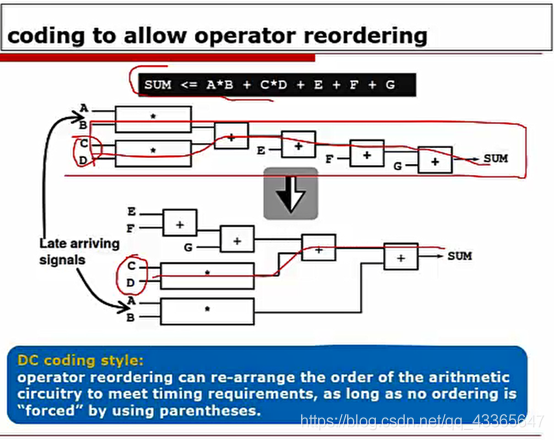

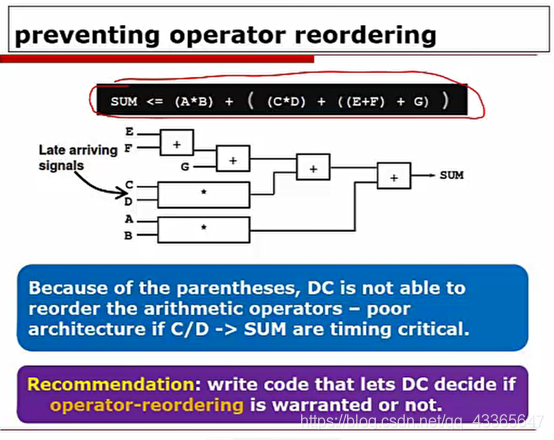

顺序重排,路径差的安排得离输出端口近一些。

通过加一些括号,compile不会帮你做调整了。

但是compile_ultra还是会……(可牛逼了(插腰))

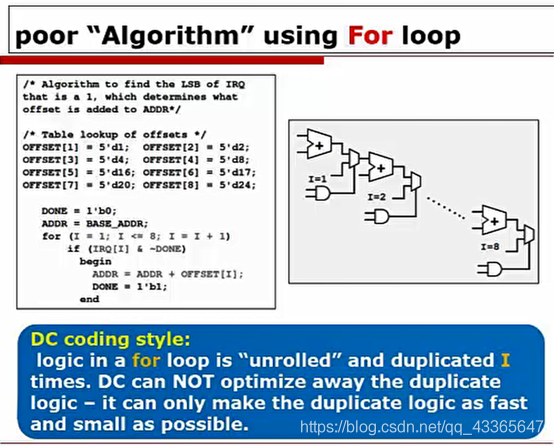

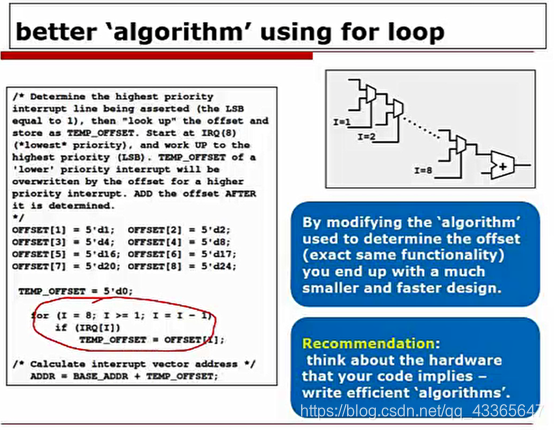

【for循环】

(8个加法器和一个选择器)

(8个选择器和一个加法器)

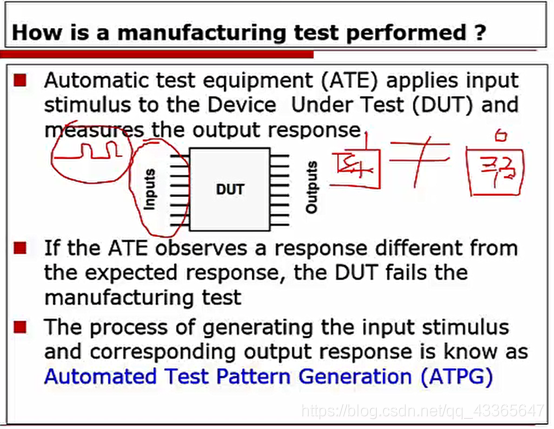

【Design for Test】

芯片是交给代工厂去生产的,但是不能保证完全没有灰尘。有灰尘就坏掉了,如何检测出来故障(短路开路)?

(一定是由机器去做的。)

在同样的激励条件下,结果不一样——有问题。

这样的测试设备叫ATE(自动测试设备)。

生成输入激励和检测信号的设备叫ATPG(这个设备只负责生成模拟,不负责物理上的测试)。

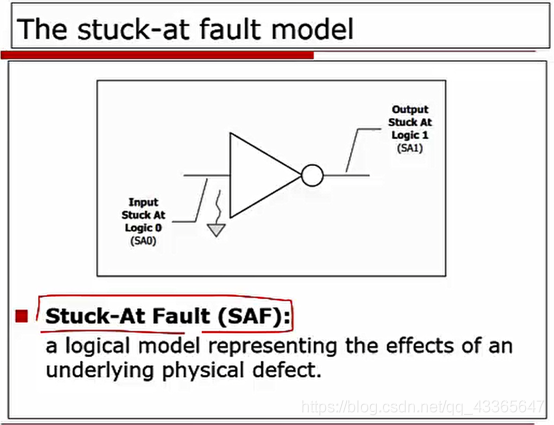

【Stuck-at fault(SAF)】

比如这是一个反相器,假如在生产的过程中,掉入了一个灰尘,把输入端和地短路了——停滞在某一个状态。

不管B怎么变化,U1的输出都是0。

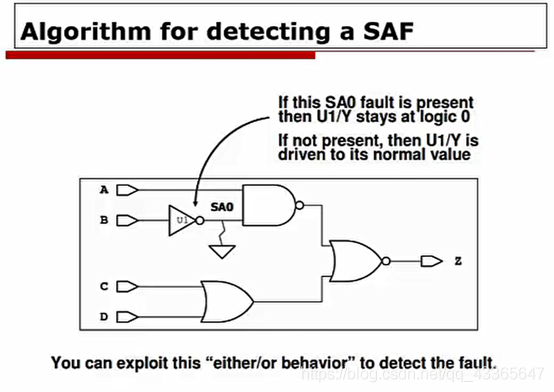

如何检测出这样的错误?

A接1,C、D接0,那么在正常情况下Z=~B

如果出现了图中的故障,B输入0,那么Z=0。

加上这个激励的目的是——让这个故障的影响能够传递到输出端口去!

discrepancy算法(差异算法)。

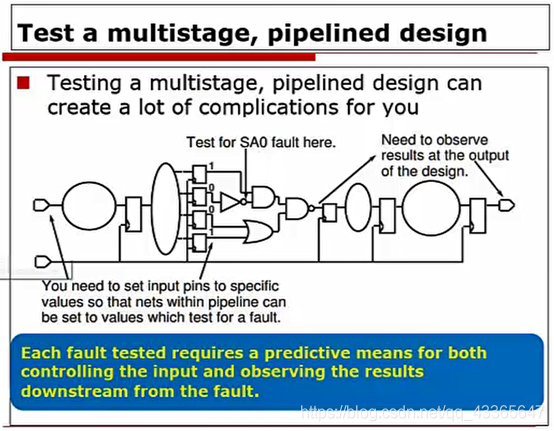

如果有一堆寄存器在里面,想办法把寄存器串成一个链,做成移位寄存器!组合路径中的错误就能测出来了。

=>用mux做成扫描链

(在做综合的时候要考虑做DFT插入扫描链会不会有问题——-scan选项的用处)

要真正形成一个链,需要用DFT Compiler工具去做。

参考大规模芯片测试。

- 点赞

- 收藏

- 分享

- 文章举报

万里独行田伯光大侠

发布了18 篇原创文章 · 获赞 4 · 访问量 654

私信

关注

万里独行田伯光大侠

发布了18 篇原创文章 · 获赞 4 · 访问量 654

私信

关注

- 数字逻辑综合工具实践-DC-10——CDC约束

- 数字逻辑综合工具实践-DC-08——静态时序分析(STA)

- 数字逻辑综合工具-DC-11——一些其它命令和综合之后的文件

- 数字逻辑综合工具-DC-09——关于timing的一些补充

- Web前端优化最佳实践及工具集锦

- 一个Web报表项目的性能分析和优化实践(七):性能监测工具JavaMelody

- Web前端优化最佳实践及工具集锦

- 一个Web报表项目的性能分析和优化实践(七):性能监测工具JavaMelody

- Web前端优化最佳实践及工具集锦

- Web前端优化最佳实践及工具集锦----转载来之于csdn,觉得挺好的,很全面,学习了。

- Web前端优化最佳实践及工具集锦

- Web前端优化最佳实践及工具集锦

- 并发逻辑备份工具mydumper实践

- Web前端优化最佳实践及工具集锦

- Web前端优化最佳实践及工具集锦

- Web前端优化最佳实践及工具集锦

- 【转】dc综合工具启动文件 .synopsys_dc.setup

- 从RTL到逻辑门的逻辑综合过程

- 一个Web报表项目的性能分析和优化实践(七):性能监测工具JavaMelody

- Web前端优化最佳实践及工具集锦