数字逻辑综合工具-DC-11——一些其它命令和综合之后的文件

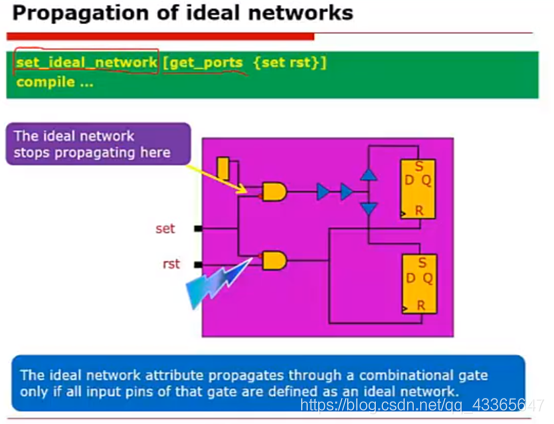

对于reset 和clock这种大扇出的信号来说,必须要人为设置为ideal network,不要让DC动它,因为线负载模型对于这些大扇出的情况估算不准。

如果不添加don’t touch属性的话,DC会在很长的一根线上插入很多负载。

一般set_ideal_network 的对象是port或者pin,net也有,比较少见。

全是ideal network的信号经过一些逻辑还是ideal的,如果有一个不是ideal的,那输出就不是ideal的。

下面这条语句的意思是驱动这个net的所有的pin或者port是理想的。

针对net设置的有另外一条命令:set_ideal_net

设置为ideal network之后,可以选择设置latency 和transition ,像set_clock_latency之类

.ddc:交给后端工具ICC

.def:交给做DFT的

.v:交给做后仿的

.sdc:约束(standard design constraint)

sdc:约束,其它公司的EDA工具做后端的时候会用到这个文件,只有synopsys的后端工具才能读入自家的ddc文件。

SCAN-DEF.def存放了一些关于扫描链的信息。做DFT的会用到。

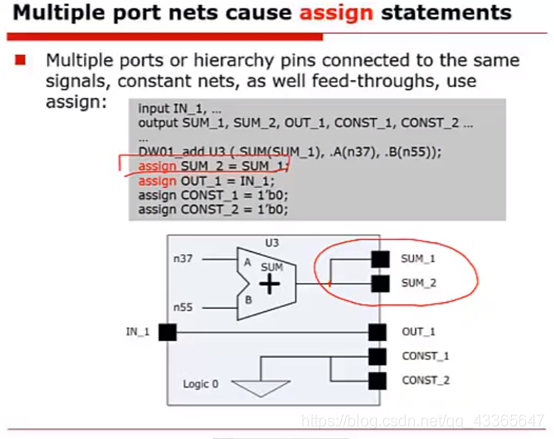

.v网表文件可能会综合出assign语句,这是不正常的。应该都是用单元例化的形式。

(tri类型的不要用,很可能生成这种assign语句。)

怎么让DC把它弄掉:

【多端口连线】

同一个输出写了两个端口会导致网表里出现assign语句。

端口输入直接连到了输出。

内部固定接到0或者1的(常数)。

增加这样一个命令:set_fix_multiple_port_nets -all -buffer_constants

插入一些buffer,不用net直连。

针对tri产生的问题:

(强制把代码中的tri转成wire。)

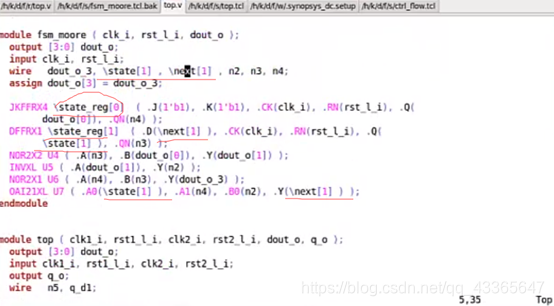

【特殊字符】

打开看网表的时候,经常在总线的前面加入一些反斜杠表示,对其他的工具而言,可能不认识。在保存的时候要把网表给拿掉。

compile之后、保存网表之前加入change_names命令

-rules verilog表示按照verilog的命名规则去命名

【【实操】】

这里有条命令,在设置输出的外部延时的时候:

set_isolate_ports设置隔离单元

在输出的时候插入buffer让输出端口和内部隔离开。

不加这个选项:当电路出现反馈结构的时候,输出端会影响电路的结果。

Step12:

第一条:不要用tri,如果用了,转换为wire类型的

第二条:如果某一个端口,没有用到,在报告的时候也显示出来

sdf文件长这样:

(把端口(all_outputs)展开成最基本的信息)

sdf文件:

时序信息

如果不用change_names,综合一些总线就会出现这样反斜杠的东西:

- 点赞

- 收藏

- 分享

- 文章举报

万里独行田伯光大侠

发布了18 篇原创文章 · 获赞 4 · 访问量 649

私信

关注

万里独行田伯光大侠

发布了18 篇原创文章 · 获赞 4 · 访问量 649

私信

关注

- 【转】dc综合工具启动文件 .synopsys_dc.setup

- mac 10.09之后文件的显示隐藏终端命令

- 批处理文件工具(java+shell命令实现)

- 关于Linu型的一些基础常见操作命令(三)——文件属性操作

- 上传文件到服务器的Linux下的命令和在Windows系统中的Xshell工具中的命令

- Linux 查看磁盘分区、文件系统、磁盘的使用情况相关的命令和工具介绍

- 一、Git的一些命令操作----创建版本库、增加文件到Git库、时光机穿梭、远程仓库

- 【收集的资料】linux 文件操作的一些命令

- linux tail 命令详解!Linux 文件内容查看工具介绍

- Linux 查看磁盘分区、文件系统、使用情况的命令和相关工具介绍

- Linux命令-下载文件的工具:wget

- 一些linux工具在windows版本下的文件放置位置

- Regsvr 32命令详解(DLL、OCX、CPL文件的注册和反注册工具)

- 文件查找工具之find命令详解

- 打开管理工具的一些小命令

- 附录四 sx工具下一些的命令

- Windows Vista的一些工具命令!!!!!

- Linux操作系统基础学习笔记(2)——文件/目录管理、常用的符号命令和工具命令

- Linux学习之CentOS(十七)--与Linux文件和目录管理相关的一些重要命令①

- IC Design综合工具--Synplify Pro的常用选项及命令