PULPino datasheet中文翻译并结合部分论文给出注释(前四章:Overview、Memory Map、CPU Core、Advanced Debug Unit)

2021-09-13 23:34

323 查看

参考:

(1)、PULPino datasheet:https://github.com/pulp-platform/pulpino/blob/master/doc/datasheet/datasheet.pdf

(2)、论文《基于RISC-V的PULPino+SoC的FPGA原型设计和物理实现》

1、OVERVIEW

PULPino是为RISC-V RI5CY和zero-riscy core 构建的单核芯片系统。PULPino重用了其bigger brother PULP的大部分组件。它使用单独的单端口数据和指令ram。它包括一个引导ROM,其中包含一个引导加载程序,可以通过SPI从外部闪存设备加载程序。 Figure 1.1 展示了SOC的框图。SoC使用AXI作为其与简单外设的APB桥的主接口。AXI和APB总线都具有32位宽的数据通道。 为了调试目的,SoC包括一个高级调试单元,它允许通过JTAG访问核心寄存器(core register)、两个RAMs和内存映射的IO。这两个ram都通过总线适配器连接到AXI总线。 图1.1 PULPino Overview.

PULPino主要针对RTL 仿真和ASICs,尽管也有一个FPGA版本。FPGA版本在性能方面并不是特别优的,因为我们主要使用它作为一个仿真平台,而不是一个standalone platform。

图1.1 PULPino Overview.

PULPino主要针对RTL 仿真和ASICs,尽管也有一个FPGA版本。FPGA版本在性能方面并不是特别优的,因为我们主要使用它作为一个仿真平台,而不是一个standalone platform。

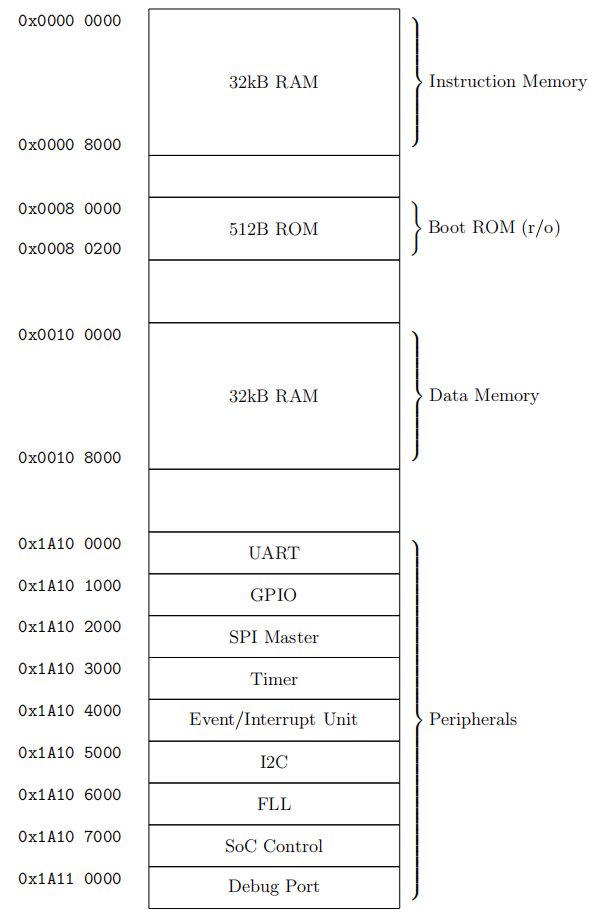

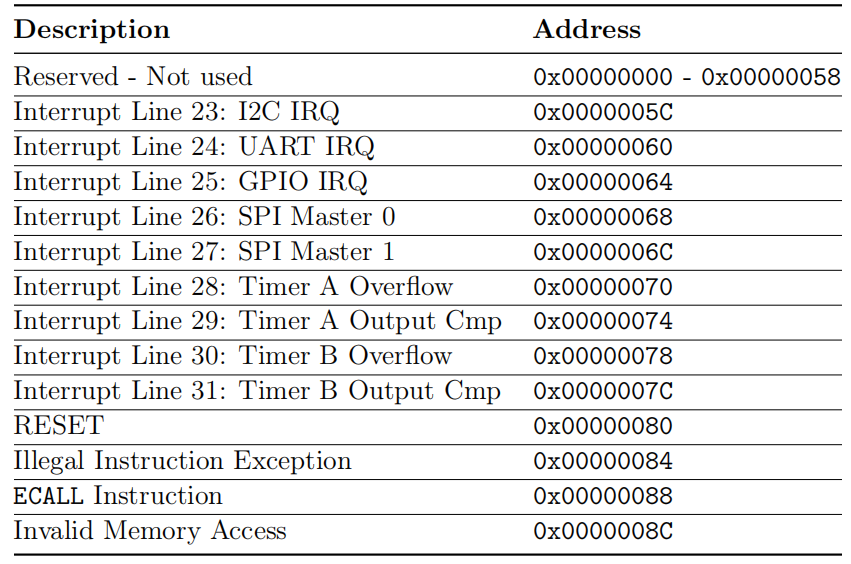

2、Memory Map

图2.1显示了PULPino的默认内存映射,假设有32kB的数据和指令内存。这可以在PULPino顶级系统版本文件中进行更改。 Figure 2.1: PULPino memory map.

Figure 2.1: PULPino memory map.

2.1、Interrupt Vector Table

PULPino的IVT遵循了对RI5CY核心的定义。 表2.1:中断/异常(exception)偏移向量表

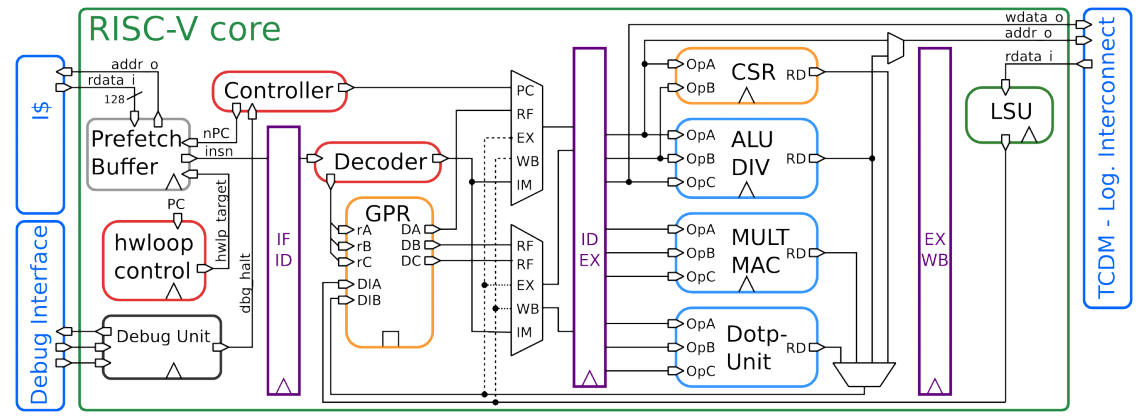

3、CPU Core

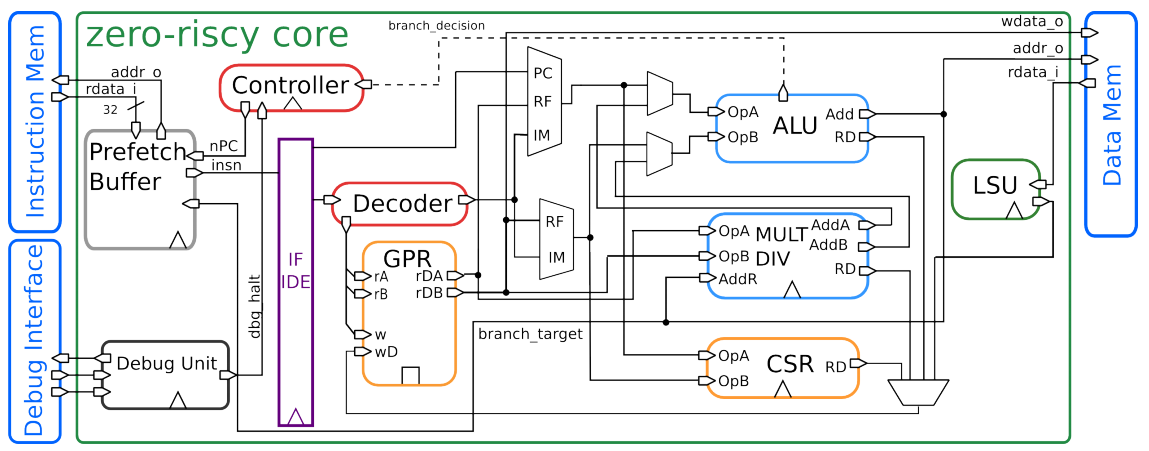

PULPino同时支持RISC-V RI5CY和RISC-V ZERO-RISCY。这两个core 具有相同的外部接口,因此与插头兼容(plug-compatible)。图3.1和3.2显示了两个core体系结构 The core使用一个非常简单的数据和指令接口来与数据和指令内存进行交互(talk)。为了与AXI接口,在PULPino中实例化了一个 core2axi 协议转换器。 为了调试,所有core register都被内存映射,允许通过AXI总线访问它们。core内部的调试单元通过此总线处理请求,并读取/设置 core register and/or halts the core。 The core支持 performance counters。这些主要用于 counting core internal events,如 stalls,但也有可能 count core-external events。为此,有ext_perf_c ad8 ounters_i端口,可以附加任意事件。然后,每当在该端口上看到 a logic high,the core 就会为该事件类型增加其 internal performance counter。 RISCY 核是一个有序的单发射核心,具有 4 级流水线,每个时钟周期能执行接近 1 条指令。该核心完全支持基本整数指令集、压缩指令集、乘法指令集扩展和单精度浮点指令集扩展,并且实现了多个 ISA 扩展,例如位操作指令、MAC 操作、支持定点操作、打包 SIMD 指令和点积。 它旨在提高超低功耗信号处理应用的能效。(见论文:基于RISC-V的PULPino+SoC的FPGA原型设计和物理实现) Figure 3.1: RISCY core overview

ZERO RISCY 核是一个有序的单发射核心,有 2 级流水线,完全支持基本整数指令集和压缩指令集。它还可以配置为具有乘法指令集扩展和为嵌入式系

统而设计的,减少整数寄存器数目的基本整数指令集。 它旨在实现超低功耗和超低面积。(见论文:基于RISC-V的PULPino+SoC的FPGA原型设计和物理实现)

Figure 3.1: RISCY core overview

ZERO RISCY 核是一个有序的单发射核心,有 2 级流水线,完全支持基本整数指令集和压缩指令集。它还可以配置为具有乘法指令集扩展和为嵌入式系

统而设计的,减少整数寄存器数目的基本整数指令集。 它旨在实现超低功耗和超低面积。(见论文:基于RISC-V的PULPino+SoC的FPGA原型设计和物理实现)

Figure 3.2: zero-riscy core overview

Figure 3.2: zero-riscy core overview

4、Advanced Debug Unit

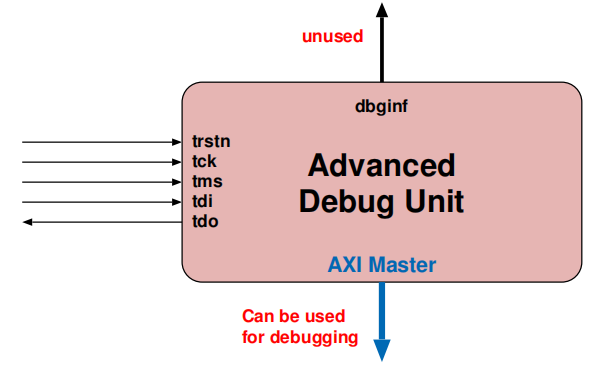

高级调试单元有一个AXI主接口来访问外围设和内存。与PulpinoV1 the adv.相比,调试单元不再具有专门的调试接口来读出所有的core register。 所有的核心寄存器(core registers)现在都是内存映射的,这意味着它们可以通过AXI接口读取。因此,调试不仅可以通过JTAG进行,而且还可以通过SPI或任何其他接口进行。 JTAG信号被连接到SoC的引脚上。(信号:trstn、tck、tms、tdl、tdo、dbginf) Figure 4.1: Advanced Debug Unit.

Figure 4.1: Advanced Debug Unit.

相关文章推荐

- unit测试时,coreData部分报错:This NSPersistentStoreCoordinator has no persistent stores.

- google论文--mapred中文翻译

- FreeBSD系统优化部分内核参数调整中文注释

- FreeBSD系统优化部分内核参数调整中文注释

- freebsd developers-handbook部分中文翻译1---freebsd代码结构

- OPENCV之CV部分参考手册的中文翻译

- GFS论文中文翻译

- JAVA程序员模拟考试题tk310-035V12.0(部分)中文翻译和解题分析

- Backbone.js 0.9.2 源码注释中文翻译版

- RAFT 论文中文翻译(1)

- BWA-MEM原始论文算法部分翻译

- You Only Look Once论文中文翻译

- Raft算法官方论文中文翻译

- DDS (Data Distribution Service) 数据分发服务-规范中文翻译-1

- 阿里AAAI2018论文解读:轻量网络训练框架、GAN中文命名实体识别、英俄翻译等

- (翻译)Django 1.0 中文文档-----指导 第二部分

- GFS论文-Google File System(中文翻译)

- OPENCV之CV部分参考手册的中文翻译

- Underscore.js 1.3.3 中文注释翻译说明

- Programming .Net component 2nd (部分中文翻译)