DMA与cache一致性的问题

Cache和DMA本身似乎是两个毫不相关的事物。Cache被用作CPU针对内存的缓存利用程序的空间局部性和时间局部性原理,达到较高的命中率,从而避免CPU每次都必须要与相对慢速的内存交互数据来提高数据的访问速率。DMA可以作为内存与外设之间传输数据的方式,在这种传输方式之下,数据并不需要经过CPU中转。

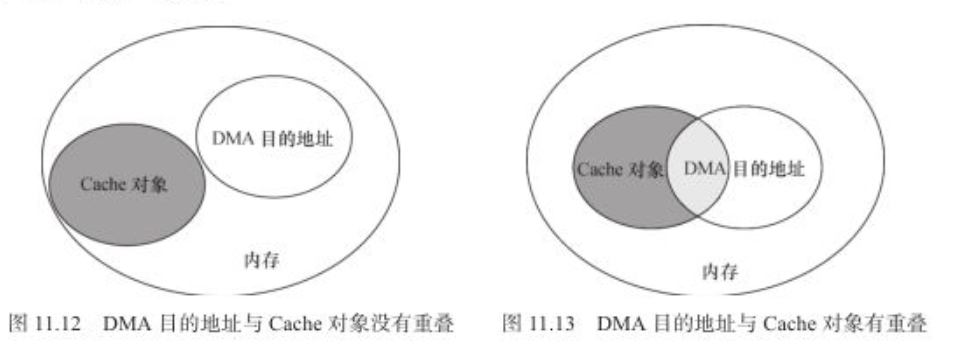

假设DMA针对内存的目的地址与 Cache缓存的对象没有重叠区域(如图11.12所示)DMA和 Cache之间将相安无事。但是,如果DMA的目的地址与 Cache所缓存的内存地址访问有重叠(如图11.13所示),经过DMA操作,与 Cache缓存对应的内存中的数据已经被修改,而CPU本身并不知道,它仍然认为 Cache中的数据就是内存中的数据,那在以后访问 Cache映射的内存时f,它仍然使用陈旧的 Cache数据。这样就会发生 Cache与内存之间数据“不一致性”的错误。

所谓 Cache数据与内存数据的不一致性,是指在采用 Cache的系统中,同样一个数据可能既存在于 Cache中,也存在于主存中, Cache与主存中的数据一样则具有一致性,数据若不一样则具有不一致性。需要特别注意的是, Cache与内存的一致性问题经常被初学者遗忘。在发生 Cache与内存不一致性错误后,驱动将无法正常运行。如果没有相关的背景知识,工程师几乎无法定位错误的原因,因为这时所有的程序看起来都是完全正确的。 Cache的不一致性问题并不是只发生在DMA的情况下,实际上,它还存在于 Cache使能和关闭的时刻。例如,对于带MMU功能的ARM处理器,在开启MMU之前,需要先置 Cache无效,对于TLB,也是如此,代码清单11.12给出的这段汇编可用来完成此任务。

/* 使cache无效 */ mov r0, #0 mcr p15, 0, r0, c7, c7, 0 mcr p15, 0, r0, c7, c10, 4 mcr p15, 0, r0, c8, c7, 0

因此申请DMA内存而避免Cache不一致的问题的话,就需要使用

dma_alloc_coherent()等方法申请;

- DMA和cache一致性问题

- DMA导致的CACHE一致性问题解决方案

- DMA和cache一致性问题解读

- DMA和cache一致性问题

- DMA和cache一致性问题

- DMA和cache一致性问题

- chche与DMA的一致性问题

- DMA和cache的一致性

- DMA及cache一致性的学习心得 --dma_alloc_writecombine

- DMA及cache一致性的学习心得

- C64x+DSP CACHE 一致性问题分析

- cache一致性问题

- cache一致性问题

- DMA及cache一致性的学习心得

- cache一致性问题

- (转)Cache的一致性问题

- 嵌入式系统中Cache一致性问题分析

- cache一致性的问题

- DMA及cache一致性的学习心得

- cache一致性问题