FPGA设计——图像处理(均值滤波)

2017-10-28 10:06

351 查看

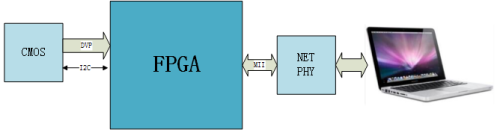

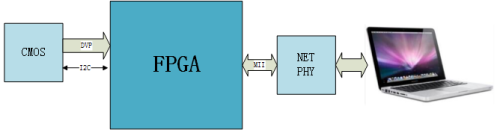

1. 概述本设计采用FPGA技术,实现CMOS视频图像的均值滤波,并通过以太网传输(UDP方式)给PC实时显示。2. 硬件系统框图CMOS采用MT9V011(30万像素),FPGA采用ALTERA公司的CYCLONE IV,以太网卡采用REALTK公司的100M网卡芯片,硬件框图如下:

硬件平台采用ETree的FPGA开发板,如下图所示:

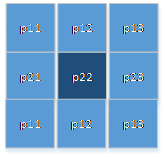

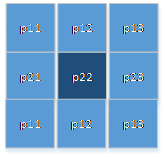

3. 算法原理均值滤波算法采用3×3矩阵累加求平均,其中中间元素(P22)为原始处理像素,如下图所示,这里不考虑边界的特殊情况。

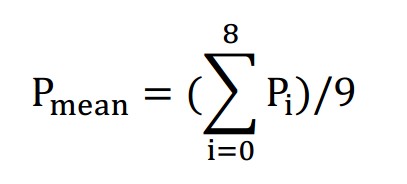

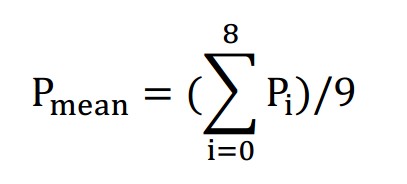

计算公式如下:

4. 算法实现

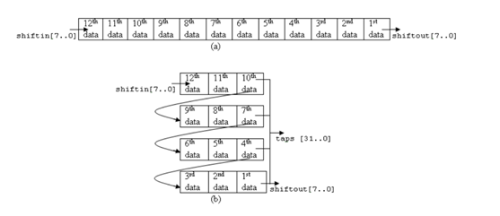

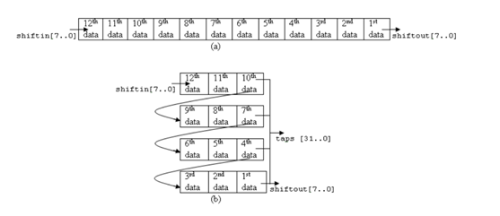

均值算法需要缓存2行或3行数据,然后利用寄存器打拍延时实现3×3的矩阵窗。数据缓存可采用dpram实现,不过Quartus II为我们提供了shift_ram组件,方便我们实现均值算法,时序如下图所示,具体的shift_ram工作原理可参考官方手册,这里不做详细介绍。

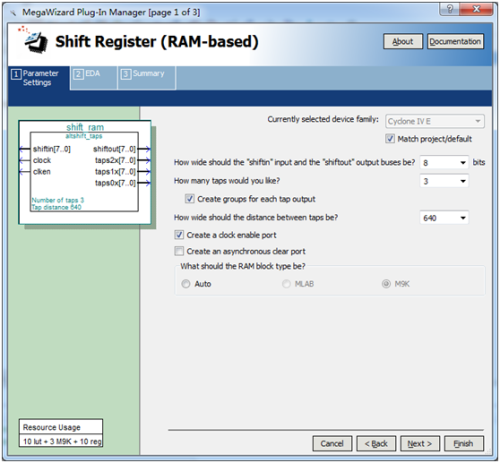

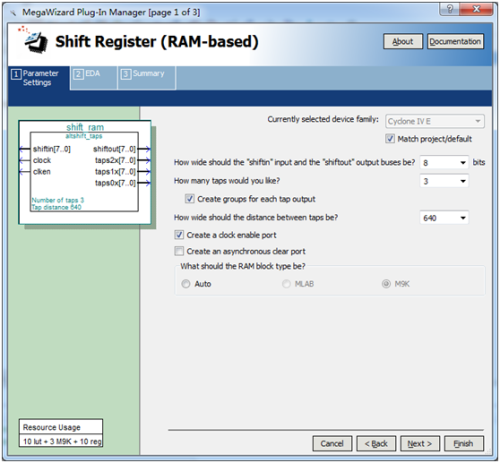

shift_ram参数设置如下图所示。

均值=累加和×(64+32+16+1)÷10245[b].[/b] 最终效果

下图为原始图片效果。

下图为经过均值滤波后的图像效果,图像得到了平滑。

硬件平台采用ETree的FPGA开发板,如下图所示:

3. 算法原理均值滤波算法采用3×3矩阵累加求平均,其中中间元素(P22)为原始处理像素,如下图所示,这里不考虑边界的特殊情况。

计算公式如下:

4. 算法实现

均值算法需要缓存2行或3行数据,然后利用寄存器打拍延时实现3×3的矩阵窗。数据缓存可采用dpram实现,不过Quartus II为我们提供了shift_ram组件,方便我们实现均值算法,时序如下图所示,具体的shift_ram工作原理可参考官方手册,这里不做详细介绍。

shift_ram参数设置如下图所示。

wire [7:0] shiftout; wire [7:0] taps0x; wire [7:0] taps1x; wire [7:0] taps2x; shift_ram shift_ram_inst ( .clock(cmos_pclk) , // input clock_sig .clken(cmos_href), .shiftin(cmos_data) , // input [7:0] shiftin_sig .shiftout(shiftout) , // output [7:0] shiftout_sig .taps0x(taps0x) , // output [7:0] taps0x_sig .taps1x(taps1x) , // output [7:0] taps1x_sig .taps2x(taps2x) ); reg [7:0] cmos_data_r0; reg [7:0] cmos_data_r1; reg [11:0] cmos_data_result; reg [7:0] taps0x_r0; reg [7:0] taps0x_r1; reg [7:0] taps1x_r0; reg [7:0] taps1x_r1; reg [7:0] taps2x_r0; reg [7:0] taps2x_r1; always @(posedge cmos_pclk) if(cmos_vsync) begin taps0x_r0 <= 0; taps0x_r1 <= 0; end else begin taps0x_r0 <= taps0x; taps0x_r1 <= taps0x_r0; end always @(posedge cmos_pclk) if(cmos_vsync) begin taps1x_r0 <= 0; taps1x_r1 <= 0; end else begin taps1x_r0 <= taps1x; taps1x_r1 <= taps1x_r0; end always @(posedge cmos_pclk) if(cmos_vsync) begin taps2x_r0 <= 0; taps2x_r1 <= 0; end else begin taps2x_r0 <= taps2x; taps2x_r1 <= taps2x_r0; end always @(posedge cmos_pclk) if(cmos_vsync) cmos_data_result <= 0; else cmos_data_result <= (((taps0x + taps0x_r0) + taps0x_r1) + ((taps1x + taps1x_r0) + taps1x_r1)) + ((taps2x + taps2x_r0) + taps2x_r1);上面代码中的‘cmos_data_result’只是累加的结果,还需要求均值。在FPGA中实现移位操作实现除法比较好实现,所以需要将除数做一下处理,具体处理方法:将累加的和乘以1024再除以1024,这样可以先人为求的1024/9的值,然后和累加和相乘,最后除以1024得到最终的值。1024/9=113.777,取113=64+32+16+1,具体计算公式如下:

均值=累加和×(64+32+16+1)÷10245[b].[/b] 最终效果

下图为原始图片效果。

下图为经过均值滤波后的图像效果,图像得到了平滑。

相关文章推荐

- FPGA设计——图像处理(Tophat形态学滤波)

- 基于FPGA的图像处理(七)--Verilog实现均值滤波

- FPGA设计——图像处理(阈值分割)

- 图像处理--不同噪声的分布直方图&&&均值滤波实例

- 图像降噪处理——(中值、均值、最大值、最小值滤波)

- 题目:opencv下对图像进行图像模糊(均值滤波)处理和边缘检测

- 基础图像处理之混合空间增强——(Java:拉普拉斯锐化、Sobel边缘检测、均值滤波、伽马变换)

- 基于FPGA视频图像处理系统设计

- 【图像处理】图像滤波去噪声——均值滤波、中值滤波、对称均值滤波 低通滤波 高通滤波(opencv)

- 利用FPGA和USB总线的视频图像的采集与处理系统设计

- 【图像处理】图像滤波5种:方框、均值、高斯、中值、双边

- 发个MatLab 自编的 均值滤波、中值滤波、高斯滤波 图像处理函数

- Win8Metro(C#)数字图像处理--2.9图像均值滤波

- MatLab 自编的 均值滤波、中值滤波、高斯滤波 图像处理函数(转)

- FPGA设计——图像处理(Sobel边缘检测)

- 图像增强之模板处理——(加权均值、加权中值、拉普拉斯滤波,FFT、DCT变换)

- 转载:发个MatLab 自编的 均值滤波、中值滤波、高斯滤波 图像处理函数

- 【图像处理】快速均值滤波

- FPGA设计——图像处理(锐化增强)

- Matlab图像处理之均值滤波