FPGA设计——图像处理(高斯滤波)

2017-10-28 10:16

344 查看

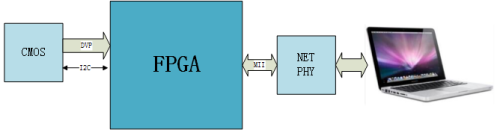

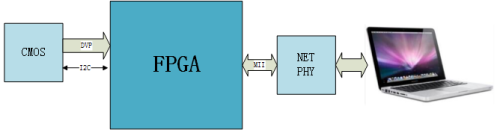

1. 概述本设计采用FPGA技术,实现CMOS视频图像的高斯滤波,并通过以太网传输(UDP方式)给PC实时显示。2. 硬件系统框图CMOS采用MT9V011(30万像素),FPGA采用ALTERA公司的CYCLONE IV,以太网卡采用REALTK公司的100M网卡芯片,硬件框图如下:

硬件平台采用ETree的FPGA开发板,如下图所示:

3. 算法原理均值滤波开的3×3矩阵加权系数为全1,而高斯滤波开的3×3矩阵加权系数是中间大两边小,如下图所示。

计算公式如下:其中C为高斯加权系数。

4. 算法实现

高斯加权系数为定点小数,这里需要乘以1024实现整数运算,最后得到加权累加和后再除以1024即可,这样高斯加权系数如下图所示。

上面代码中的‘cmos_data_result’只是累加的结果,还需要求均值。在FPGA中实现移位操作实现除法比较好实现,所以需要将除数做一下处理,具体处理方法:将累加的和乘以1024再除以1024,这样可以先人为求的1024/9的值,然后和累加和相乘,最后除以1024得到最终的值。1024/9=113.777,取113=64+32+16+1,具体计算公式如下:

结果=累加和×(64+32+16+1)÷1024

5. 最终效果下图为原始图片效果。

高斯滤波后的效果图如下,实现了完成了图像细节与噪声滤除之间的平衡。

硬件平台采用ETree的FPGA开发板,如下图所示:

3. 算法原理均值滤波开的3×3矩阵加权系数为全1,而高斯滤波开的3×3矩阵加权系数是中间大两边小,如下图所示。

计算公式如下:其中C为高斯加权系数。

4. 算法实现

高斯加权系数为定点小数,这里需要乘以1024实现整数运算,最后得到加权累加和后再除以1024即可,这样高斯加权系数如下图所示。

always @(posedge cmos_pclk) if(cmos_vsync) cmos_data_result <= 0; else cmos_data_result <= (((taps0x*104+taps0x_r0*772)+taps0x_r1*104)+ ((taps1x*772 + taps1x_r0*5707) +taps1x_r1*772))+ ((taps2x*104 + taps2x_r0*772) + taps2x_r1*104);

上面代码中的‘cmos_data_result’只是累加的结果,还需要求均值。在FPGA中实现移位操作实现除法比较好实现,所以需要将除数做一下处理,具体处理方法:将累加的和乘以1024再除以1024,这样可以先人为求的1024/9的值,然后和累加和相乘,最后除以1024得到最终的值。1024/9=113.777,取113=64+32+16+1,具体计算公式如下:

结果=累加和×(64+32+16+1)÷1024

5. 最终效果下图为原始图片效果。

高斯滤波后的效果图如下,实现了完成了图像细节与噪声滤除之间的平衡。

相关文章推荐

- 基于FPGA+DSP的实时图像处理平台的设计与实现

- FPGA设计——图像处理(Sobel边缘检测)

- FPGA设计——图像处理(锐化增强)

- FPGA设计——图像处理(Tophat形态学滤波)

- 基于FPGA视频图像处理系统设计

- 基于DSP和FPGA的通用图像处理平台设计

- 利用FPGA和USB总线的视频图像的采集与处理系统设计

- FPGA设计——图像处理(均值滤波)

- FPGA设计——图像处理(中值滤波)

- FPGA设计——图像处理(阈值分割)

- 深度学习FPGA实现基础知识16(图像处理中任意核卷积(matlab中conv2函数)的快速实现)

- Camera Link协议和FPGA的数字图像信号源设计

- FPGA设计——全局曝光CMOS图像采集与USB2.0显示

- 基于FPGA的图像处理(三)--图像融合

- ARM,DSP和FPGA(xilinx spartan6系列)在图像处理中应用与比较,他们之间应该怎样分工协作

- 基于FPGA的跨时钟域信号处理——同步设计的重要

- “共轭变换”图像处理算法在FPGA 上实现的研究

- FPGA图像处理项目(二)--FIFO FFT RAM

- FPGA图像处理之画中画(pip)

- DICOM医学图像处理:Dcmtk与fo-dicom保存文件的不同设计模式之“同步VS异步”+“单线程VS多线程”