Veriog_Notes_Chapter 7

2015-07-26 19:17

501 查看

系统任务monitor,监控和输出参数列表中的表达式或变量值。控制格式输出规则和display一样。montioronmonitorof;打开或关闭监控标志。多模块使用monitor时任意时刻都只能执行一个monitor,所以需要mornitoron与mornitoroff配合使用。monitor($time,”rxd=%btxd=%b”,rxd,txd).

时间度量系统函数time和realtime。time 显示时刻收时间尺度比例的影响。而且输出总是输出整数。Realtime返回时间数字为实型数据。

$finish (n) 0:不输出信息1:输出当前仿真时刻和位置2:时刻、位置和所用的memory和cpu时间统计。

$stop (n) 越大输出的信息越多。

readmenb/readmenh(“<数据文件名>”,<存储器名>,<起始地址>,<结束地址>);或者(“<数据文件名>”,<存储器名>,<起始地址>);(“<数据文件名>”,<存储器名>);

系统任务randomrandom%b数据范围[-b,b]例:rand={$random}%60;即通过位拼接操作产生一个0到59的数。可以产生随机脉冲序列或宽度随机的脉冲序列。用于电路检测。

编译预处理常用的预编译命令’define wordsize 8 、‘define 标志符 字符 ‘define signal string。已经定义过的宏名可以层层置换。

’include,可以将常用的宏定义命令或task组成一个文件。

‘ timescale <时间单位>/<时间精度> fs(飞秒) 10-15s

条件编译命令(‘ifdef,’else,’endif)

‘Ifdef (标识符) 程序段1;‘esle 程序段2;’endif

‘ifdef(标识符) 程序段1;‘endif

条件执行 (testplusargs) (仅适用于行为语句)

使用实例:利用自带的门逻辑搭建d触发器

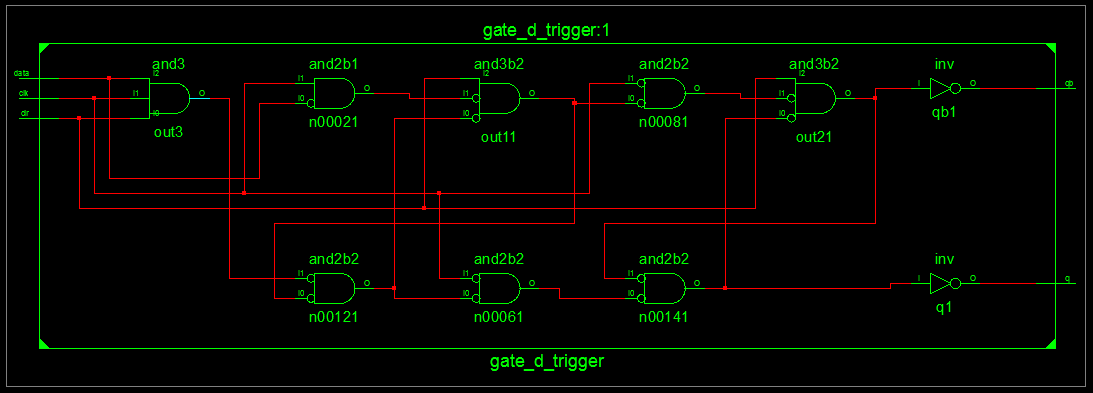

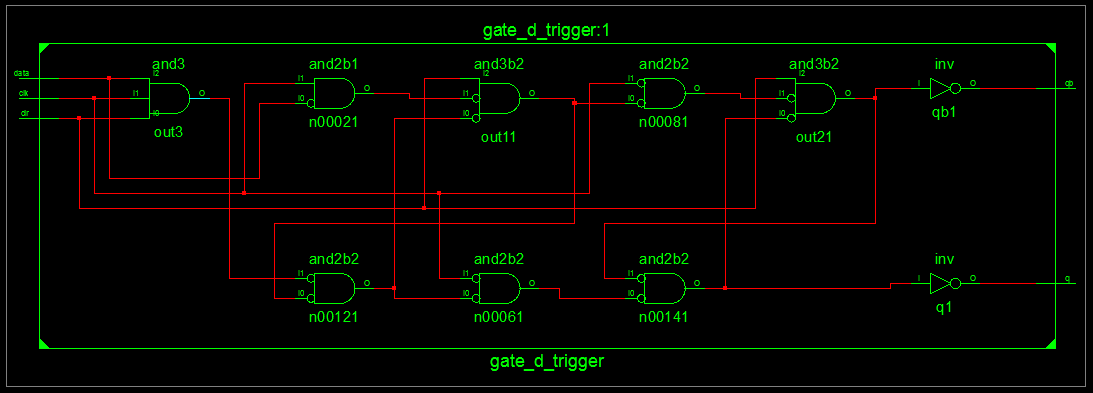

RTL传输级电路图

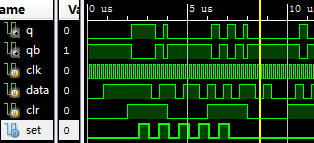

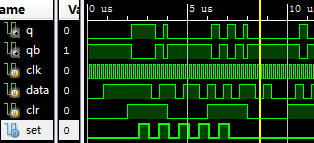

Modlesim 仿真结果

时间度量系统函数time和realtime。time 显示时刻收时间尺度比例的影响。而且输出总是输出整数。Realtime返回时间数字为实型数据。

$finish (n) 0:不输出信息1:输出当前仿真时刻和位置2:时刻、位置和所用的memory和cpu时间统计。

$stop (n) 越大输出的信息越多。

readmenb/readmenh(“<数据文件名>”,<存储器名>,<起始地址>,<结束地址>);或者(“<数据文件名>”,<存储器名>,<起始地址>);(“<数据文件名>”,<存储器名>);

系统任务randomrandom%b数据范围[-b,b]例:rand={$random}%60;即通过位拼接操作产生一个0到59的数。可以产生随机脉冲序列或宽度随机的脉冲序列。用于电路检测。

编译预处理常用的预编译命令’define wordsize 8 、‘define 标志符 字符 ‘define signal string。已经定义过的宏名可以层层置换。

’include,可以将常用的宏定义命令或task组成一个文件。

‘ timescale <时间单位>/<时间精度> fs(飞秒) 10-15s

条件编译命令(‘ifdef,’else,’endif)

‘Ifdef (标识符) 程序段1;‘esle 程序段2;’endif

‘ifdef(标识符) 程序段1;‘endif

条件执行 (testplusargs) (仅适用于行为语句)

使用实例:利用自带的门逻辑搭建d触发器

module gate_d_trigger( clk, data, q,qb, clr); input clk,data,clr; output q,qb; nand #10 nd1(a,clr,clk,data), nd2(b,clk,ndata), nd4(d,c,b,clr), nd5(e,c,nclk), nd6(f,d,nclk), nd8(qb,f,clr,q); nand #9 nd3(c,d,a), nd7(q,e,qb); not #10 inv1(ndata,data), inv2(nclk,clk); endmodule

`timescale 1ns / 1psmodule gate_d_trigger_tb;

reg clk;reg data;reg clr;wire q;wireqb;regset;

gate_d_trigger uut (

.clk(clk), .data(data), .q(q), .qb(qb), .clr(clr));

initial begin

clk = 0;data = 0;clr = 0;set=0;#100;

end

initial begin

#100;$display("data=%bbin",data);

#2000;$monitor($time,"set=",set);

repeat(10) #500 set=~set;end

always #100 clk=~clk;

always #400 data = $random%50;

always #2000 clr=~clr;

//$stop(7);

endmoduleRTL传输级电路图

Modlesim 仿真结果

相关文章推荐

- 《FPGA嵌入式项目开发实战》

- 关于FPGA中的Logic Cells, Logic Slices, Configurable Logic Blocks and Gates

- Verilog文件格式范例

- DSP多网口开发板

- ARM+FPGA核心板

- DSP+ARM+FPGA核心板

- 基于VHDL的按键扫描程序

- Xilinx FPFA中LUT4_L 元件的使用

- ISE 综合面积报告分析

- 深圳嵌入式培训 修练软硬件之功 高薪一路相伴

- FPGA点灯

- 深圳视晶无线技术有限公司 狗血经历

- Verilog $Scannf 使用小结

- 如何解决NO EPCS LAYOUT DATA --- LOOKING FOR SECTION [EPCS-XXXXXX]

- FPGA基于CORDIC算法的求平方实现

- 应用matlab&modelsim设计FPGA算法(1)

- 《Xilinx可编程逻辑器件设计与开发(基础篇)》连载21:Spartan-6的时钟资源

- 阻塞与非阻塞(blocking and non-blocking)

- FPGA里怎么做小数乘法

- 关于FPGA逻辑设计的21个小贴士