[FPGA]基于FPGA的数字跑表

基于FPGA的数字跑表的设计与实现

一、设计要求

用FPGA设计并实现一个数字跑表,范围为0~59分59.99秒。可以实现数字跑表进行启动、停止计时和显示读数三个操作,可以在数码管上显示读数。

二、设计任务

2.1基本部分

(1)了解FPGA开发板,了解数字跑表的功能。

(2)VHDL语言编程实现数字跑表系统的功能模块,数字跑表进行启动、停止、显示读数操作,并具有计时清零功能;

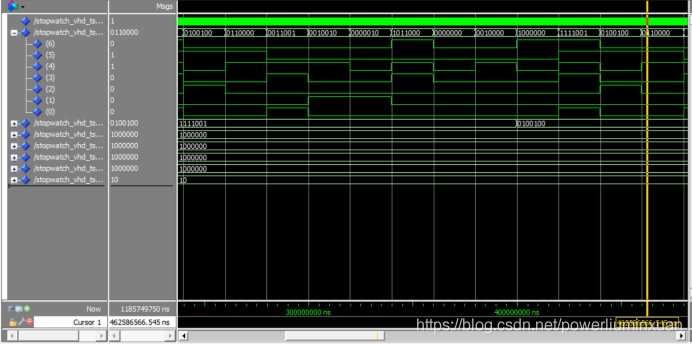

(3)程序编译正确,在Modelsim中仿真正确;

(4)采用FPGA开发板作为开发平台,能够下载验证。

2.2提高部分

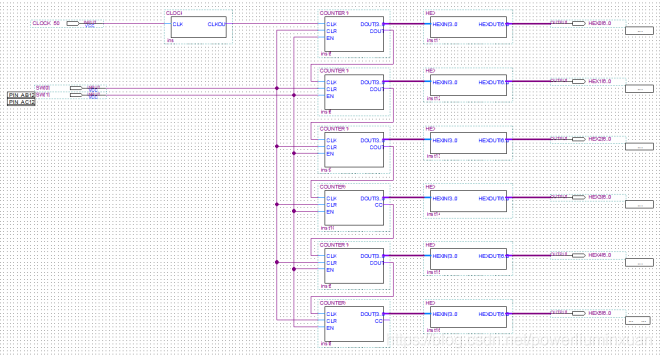

能够采用原理图设计法设计。

三、设计原理

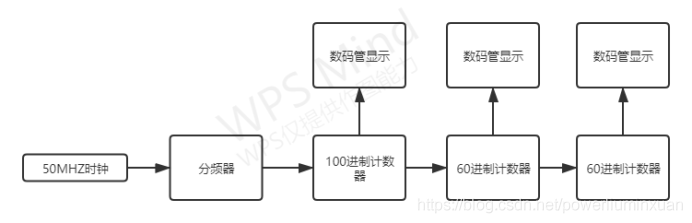

图3.1系统框图

如图,如果要实现计时范围为0~59分59.99秒的数字跑表并在数码管上显示读数,那么需要设计时钟电路、分频电路、计数器电路、译码显示1电路。将DE1-SOC开发套件中提供的50MHZ时钟进行分频至100HZ后送入100进制计数器,计数器计满100后发出进位信号送入计秒模块的60进制计数器,计数器满60后发出进位信号送入计分模块的60进制计数器,每个计数器分别连接不同的数码管显示电路,实时显示计时效果。因此使用原理图输入设计法,使用QuartusII软件编写元件代码和绘制原理图,而后进行综合仿真。

四、设计方案

4.1 硬件设计

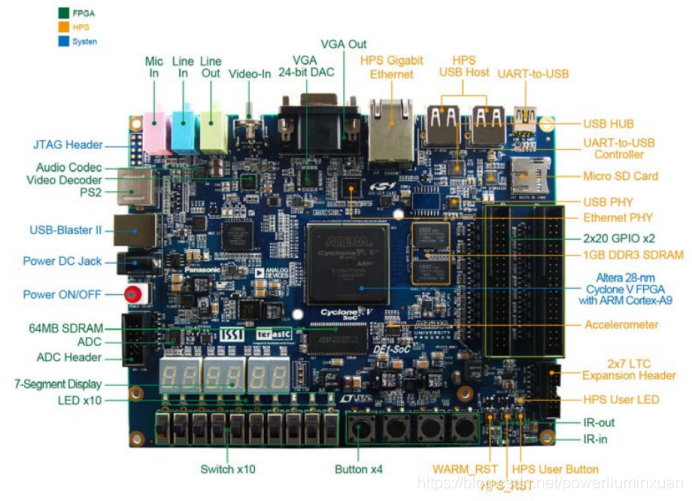

本设计需要用到一个稳定的50MHZ的时钟,一个500000分频的分频器,一个100进制计数器,两个60进制计数器,两个拨码开关,六个7段数码管。综上所述,DE1-SOC开发套件提供的FPGA芯片可满足对分频器和计数器的设计需求,丰富的外部设备可满足对数码管和拨码开关的需求。

图4.1 DE1-SOC开发板实物图

4.2 软件设计

一百进制计数器采用两个十进制计数器级联的方式实现,六十进制计数器采用十进制和六进制计数器级联的方式实现。

4.2.1 分频器

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY CLOCK IS PORT(CLK:IN STD_LOGIC; CLKOUT:OUT STD_LOGIC); END CLOCK; ARCHITECTURE RTL OF CLOCK IS SIGNAL CLK_1_REG: STD_LOGIC := '1'; BEGIN CLKOUT<=CLK_1_REG; PROCESS(CLK) VARIABLE COUNT :INTEGER RANGE 0 TO 500000; BEGIN IF(CLK'EVENT AND CLK='1')THEN IF COUNT = 500000 THEN COUNT:=0; CLK_1_REG<=NOT CLK_1_REG; ELSE COUNT:=COUNT+1; END IF; END IF; END PROCESS; END RTL;

4.2.2 数码管显示电路

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY HEX IS PORT( HEXIN:IN STD_LOGIC_VECTOR(3 DOWNTO 0); HEXOUT:OUT STD_LOGIC_VECTOR(6 DOWNTO 0)); END HEX; ARCHITECTURE RTL OF HEX IS BEGIN PROCESS(HEXIN) BEGIN CASE HEXIN IS WHEN "0000" => HEXOUT <="1000000"; WHEN "0001" => HEXOUT <="1111001"; WHEN "0010" => HEXOUT <="0100100"; WHEN "0011" => HEXOUT <="0110000"; WHEN "0100" => HEXOUT <="0011001"; WHEN "0101" => HEXOUT <="0010010"; WHEN "0110" => HEXOUT <="0000010"; WHEN "0111" => HEXOUT <="1011000"; WHEN "1000" => HEXOUT <="0000000"; WHEN "1001" => HEXOUT <="0010000"; WHEN "1010" => HEXOUT <="0001000"; WHEN "1011" => HEXOUT <="0000011"; WHEN "1100&# 17d2c 34; => HEXOUT <="1000110"; WHEN "1101" => HEXOUT <="0100001"; WHEN "1110" => HEXOUT <="0000110"; WHEN OTHERS => HEXOUT <="1000000"; END CASE; END PROCESS; END RTL;

4.2.3 十进制计数器

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY COUNTER10 IS PORT(CLK,CLR,EN: IN STD_LOGIC; DOUT : OUT STD_LOGIC_VECTOR (3 DOWNTO 0); COUT : OUT STD_LOGIC); END COUNTER10; ARCHITECTURE RTL OF COUNTER10 IS BEGIN PROCESS(CLK,CLR,EN) VARIABLE Q : STD_LOGIC_VECTOR (3 DOWNTO 0); BEGIN IF CLR = '1' THEN Q := (OTHERS => '0'); ELSIF CLK'EVENT AND CLK = '1' THEN IF EN = '1' THEN IF Q < 9 THEN Q := Q + 1; ELSE Q := (OTHERS => '0'); END IF; END IF;END IF; IF Q = "0000" THEN COUT <= '1'; ELSE COUT <= '0'; END IF; DOUT <= Q; END PROCESS; END RTL;

4.2.4 六进制计数器

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY COUNTER6 IS PORT(CLK,CLR,EN: IN STD_LOGIC; DOUT : OUT STD_LOGIC_VECTOR (3 DOWNTO 0); CO : OUT STD_LOGIC); END COUNTER6; ARCHITECTURE RTL OF COUNTER6 IS BEGIN PROCESS(CLK,CLR,EN) VARIABLE Q : STD_LOGIC_VECTOR (3 DOWNTO 0); BEGIN IF(CLR='1')THEN Q:="0000"; CO<='0'; ELSIF(CLK'EVENT AND CLK = '1') THEN IF(EN='1')THEN IF(Q <5)THEN Q := Q + 1; ELSE Q := (OTHERS => '0'); END IF; END IF; END IF; IF Q = "0000" THEN CO <= '1'; ELSE CO <= '0'; END IF; DOUT <= Q; END PROCESS; END RTL;

QQ:1187060103

- 2020 年你读了哪些觉得比较好的计算机书籍?

- 设计模式之初体验

- Docker 网络解读

- 今年30了,做了5年的软件测试,只会功能测试的怎么办?【乐搏TestPro】

- Java中List的五种去重方法及效率对比,你都用对了吗?

- C#调用pyd

- 那个小白还没搞懂内存溢出,只能用案例说给他听了

- 华为忍痛别荣耀:一个好策略!

- 瞄准车辆虚拟显示领域,「锐思华创」打造超大视角空间车载AR-HUD

- 透视行业前景,促进产创融合——2020世界物联网博览会创新成果发布会暨中国企业战略投资峰会召开在即

- 为什么滴滴、顺丰、钉钉、闲鱼并不是一个好名字?

- SpringBoot入门到精通(十):国际化与Webjars的应用(2021最新最易懂)

- 【Chrome必备插件,一键提升10倍效率】新用户永久免广告,好用!

- Mybatis初始化过程

- Mybatis架构原理

- pgsql pldebugger插件

- 单步调试海康ClientDemo工程未解决

- TargetFrameworks输出多版本类库,SDK 样式项目中的目标框架

- Protobuffer编译安装和文件编写

- php环境下nginx超时问题解决