1.11.ARM的37个寄存器详解

2017-08-03 15:41

501 查看

ARM处理器含有37个寄存器,这些寄存器包含以下两类:

1. 31个通用寄存器:包括程序计数器PC等,都是32位的寄存器。

2. 6个状态寄存器

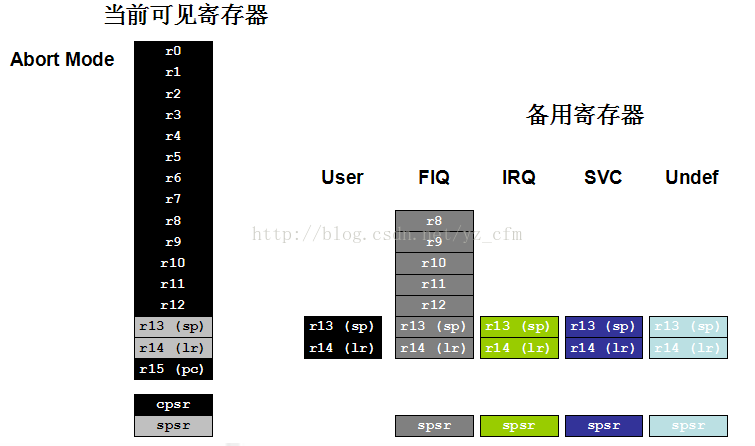

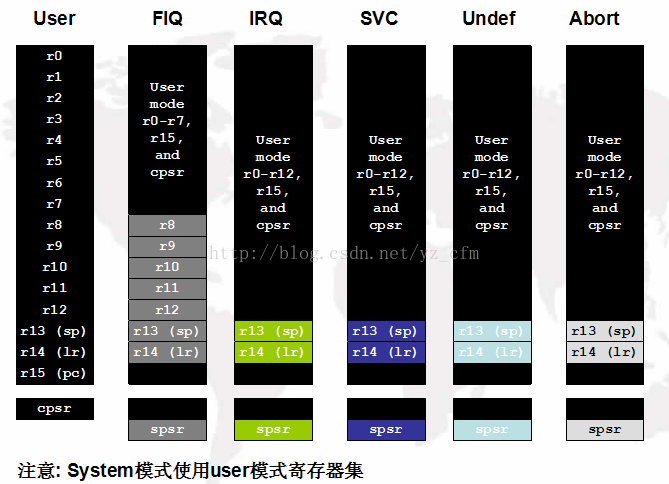

下面这幅图就是ARM中的 37 个寄存器:

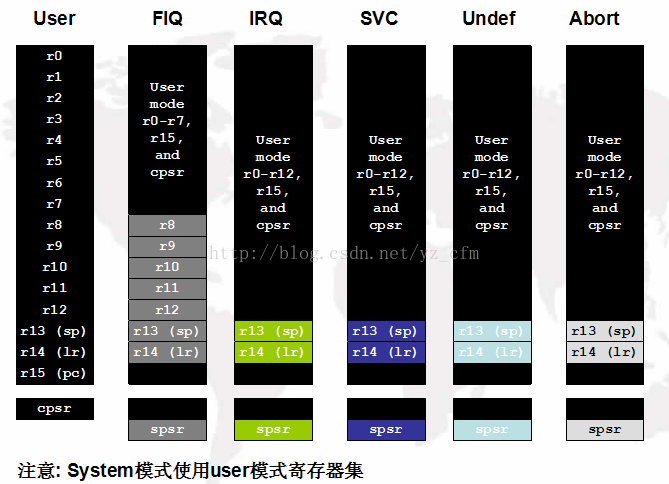

下面这幅图是 7种工作模式下每个模式下的寄存器列表:

综上:

* ARM共有37个寄存器,每个寄存器都是32位的长度。

* 37个寄存器中30个为“通用型”,1个固定用作PC,一个固定用作CPSR,5个固定用作5种异常模式下的SPSR。

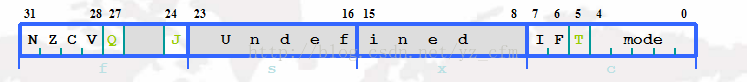

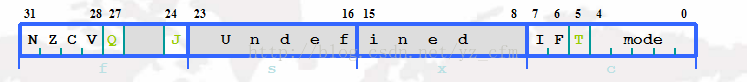

下面说一下CPSR程序状态寄存器:

这里我主要记住高四位:

1.条件标志位

-N: Negative result from ALU

-Z: Zero result from ALU

-C: ALU operation Carried out (进位/借位)

-V: ALU operation overflowed (溢出)

* N=1时,说明运算的结果为负数,N=0时,说明运算的结果为正数或零。

* Z=1时,说明运算的结果为0,Z=0时,说明运算的结果为非0。

* C:

- 加法运算(包括CMP):当运算结果产生了进位时(无符号数溢出),C=1,否则为0。

- 减法运算(包括CMP):当运算结果产生了借位时(无符号数溢出),C=0,否则C=1。

- 对于包含移位操作的非加减指令操作时,C为移除值的最后一位。

- 对于其它的非加减指令,C的值通常不变。

* V:

- 对于加减法运算指令,当操作数和运算结果为二进制的补码表示的带符号数时,V=1表示符号位溢出

- 对于其它的非加减法指令,V的值通常不变。

2.Q位:

* 在ARM V5及以上的版本的E系列处理器中,Q标识位指示增强的DSP运算指令是否发生了溢出,在其它版本的处理器中,Q未定义。

3.J位:

* 仅ARM 5TE/J 架构支持

* J=1时,处理器处于Jazelle状态

4.中断禁止位:

* I=1,禁止IRQ

* F=1,禁止FIQ

5.T位:

* 仅ARM xT架构支持

* T=0,处理器处于ARM状态

* T=1,处理器处于Thumb状态

6.Mode位:

* 处理器工作模式选择位

注意:

* CPSR中的各个位表明了CPU的某个状态信息,这些信息和后面我们用的汇编指令息息相关。

* CPSR的I、F位和开中断、关中断有关。

* CPSR的Mode位决定了CPU的工作模式,在uBoot代码中会使用汇编代码进行设置。

PC(R15)程序控制寄存器:

* PC(Program Control Register)为程序指针,PC指向哪里,CPU就会指向哪条指令(所以程序跳转时就是把目标地址代码放到PC中)。

* 整个CPU中只有一个PC(CPSR也只有一个,但SPSR有5个)。

1. 31个通用寄存器:包括程序计数器PC等,都是32位的寄存器。

2. 6个状态寄存器

下面这幅图就是ARM中的 37 个寄存器:

下面这幅图是 7种工作模式下每个模式下的寄存器列表:

综上:

* ARM共有37个寄存器,每个寄存器都是32位的长度。

* 37个寄存器中30个为“通用型”,1个固定用作PC,一个固定用作CPSR,5个固定用作5种异常模式下的SPSR。

下面说一下CPSR程序状态寄存器:

这里我主要记住高四位:

1.条件标志位

-N: Negative result from ALU

-Z: Zero result from ALU

-C: ALU operation Carried out (进位/借位)

-V: ALU operation overflowed (溢出)

* N=1时,说明运算的结果为负数,N=0时,说明运算的结果为正数或零。

* Z=1时,说明运算的结果为0,Z=0时,说明运算的结果为非0。

* C:

- 加法运算(包括CMP):当运算结果产生了进位时(无符号数溢出),C=1,否则为0。

- 减法运算(包括CMP):当运算结果产生了借位时(无符号数溢出),C=0,否则C=1。

- 对于包含移位操作的非加减指令操作时,C为移除值的最后一位。

- 对于其它的非加减指令,C的值通常不变。

* V:

- 对于加减法运算指令,当操作数和运算结果为二进制的补码表示的带符号数时,V=1表示符号位溢出

- 对于其它的非加减法指令,V的值通常不变。

2.Q位:

* 在ARM V5及以上的版本的E系列处理器中,Q标识位指示增强的DSP运算指令是否发生了溢出,在其它版本的处理器中,Q未定义。

3.J位:

* 仅ARM 5TE/J 架构支持

* J=1时,处理器处于Jazelle状态

4.中断禁止位:

* I=1,禁止IRQ

* F=1,禁止FIQ

5.T位:

* 仅ARM xT架构支持

* T=0,处理器处于ARM状态

* T=1,处理器处于Thumb状态

6.Mode位:

* 处理器工作模式选择位

注意:

* CPSR中的各个位表明了CPU的某个状态信息,这些信息和后面我们用的汇编指令息息相关。

* CPSR的I、F位和开中断、关中断有关。

* CPSR的Mode位决定了CPU的工作模式,在uBoot代码中会使用汇编代码进行设置。

PC(R15)程序控制寄存器:

* PC(Program Control Register)为程序指针,PC指向哪里,CPU就会指向哪条指令(所以程序跳转时就是把目标地址代码放到PC中)。

* 整个CPU中只有一个PC(CPSR也只有一个,但SPSR有5个)。

相关文章推荐

- 1.2.13、ARM的37个寄存器详解

- ARM第一部分-ARM的37个寄存器详解

- ARM的37个寄存器详解

- ARM-----寄存器操作*(volatile uint32 *)含义详解

- ARM 中断寄存器详解(转)

- ARM寄存器与汇编指令详解

- ARM寄存器与汇编指令详解

- S5PV210系列(裸机二) ARM的编程模式、7种模式和37个寄存器

- arm中断控制寄存器详解

- ARM的37个寄存器

- ARM 寄存器详解

- ARM中断寄存器详解

- ARM特殊寄存器定义详解——#define A (* (volatile unsigned long *) 0x48000000(zz)

- 13.ARM的37个寄存器详解

- ARM的7种工作模式、37个通用寄存器、CPSR程序状态寄存器

- ARM特殊寄存器定义详解——#define A (* (volatile unsigned long *) 0x48000000

- arm中断控制寄存器详解

- Arm汇编学习笔记(四)——Arm的37个寄存器和异常处理

- ARM的37个寄存器介绍

- ARM中断寄存器详解