【STM32F103攻城笔记】内部晶振HSI倍频设置系统时钟

2017-06-02 17:47

866 查看

首先说明,因为STM32芯片的型号不同,所以对于不同芯片有不同频率的限制,比如某些时钟频率不能大于多少,这是根据手册来设置的!但改变频率的寄存器都一样,只是我们设置频率大小要受芯片的限制!下面我用的芯片型号是STM32F103VBT6!它就限制了内部晶振的倍频不能大于64MHz(但其实我实验出来是52MHz)!

本文是利用内部晶振(HSI)来倍频,与外部晶振倍频区分开!

第一步:打开system_STM32f10x.c,找到函数void SystemInit (void){},把原有的都注释掉,将下面的代码复制进去:

/* 开启HSI 即内部晶振时钟 */

RCC->CR |= (uint32_t)0x00000001;

/*选择HSI为PLL的时钟源HSI必须2分频给PLL*/

RCC->CFGR |= (uint32_t)RCC_CFGR_PLLSRC_HSI_Div2;

/*PLLCLK=8/2*13=52MHz 设置倍频得到时钟源PLL的频率*/

RCC->CFGR |= (uint32_t)RCC_CFGR_PLLMULL13;

/* PLL不分频输出 */

RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1;

/* 使能 PLL时钟 */

RCC->CR |= RCC_CR_PLLON;

/* 等待PLL时钟就绪*/

while((RCC->CR & RCC_CR_PLLRDY) == 0)

{

}

/* 选择PLL为系统时钟的时钟源 */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));

RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL;

/* 等到PLL成为系统时钟的时钟源*/

while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)0x08)

{

}

这段代码其实就是是HSI倍频成为PLL的时钟源,又使PLL成为系统时钟的时钟源,这样就相当于HSI倍频后给系统时钟了!

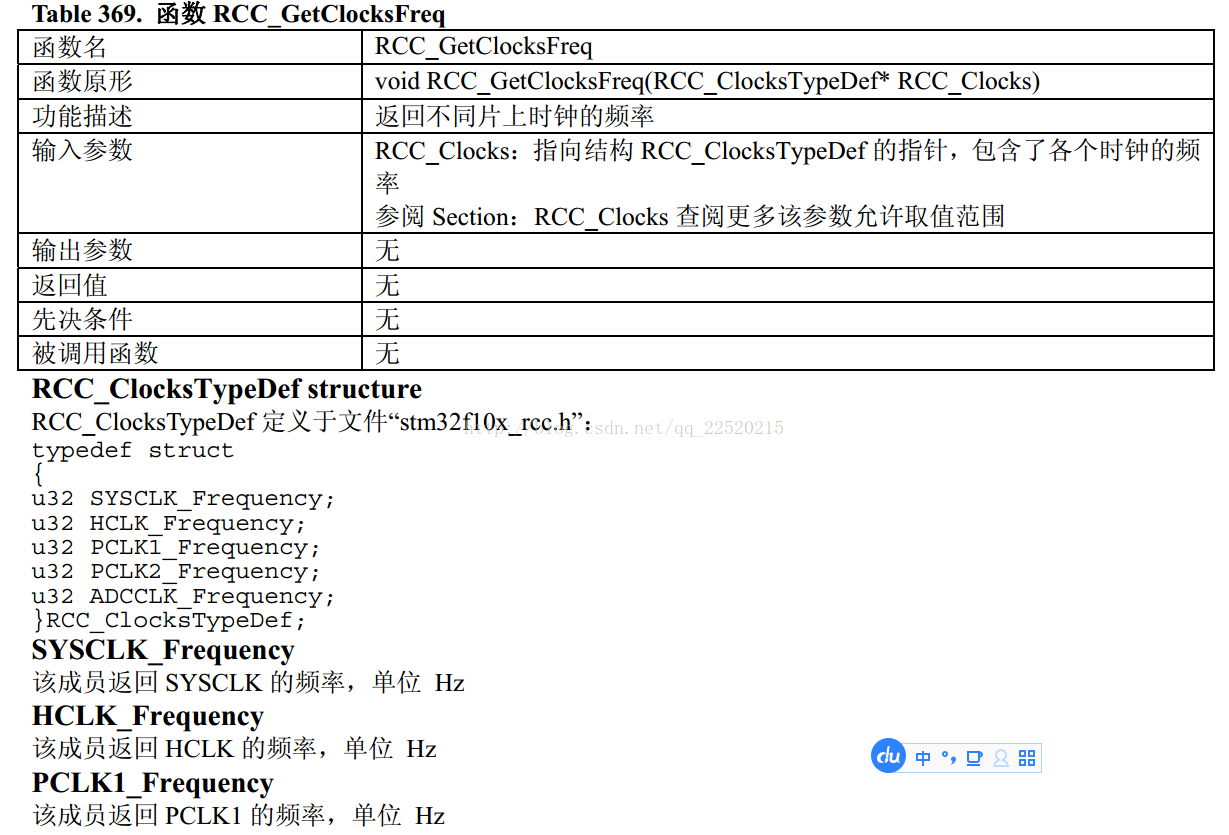

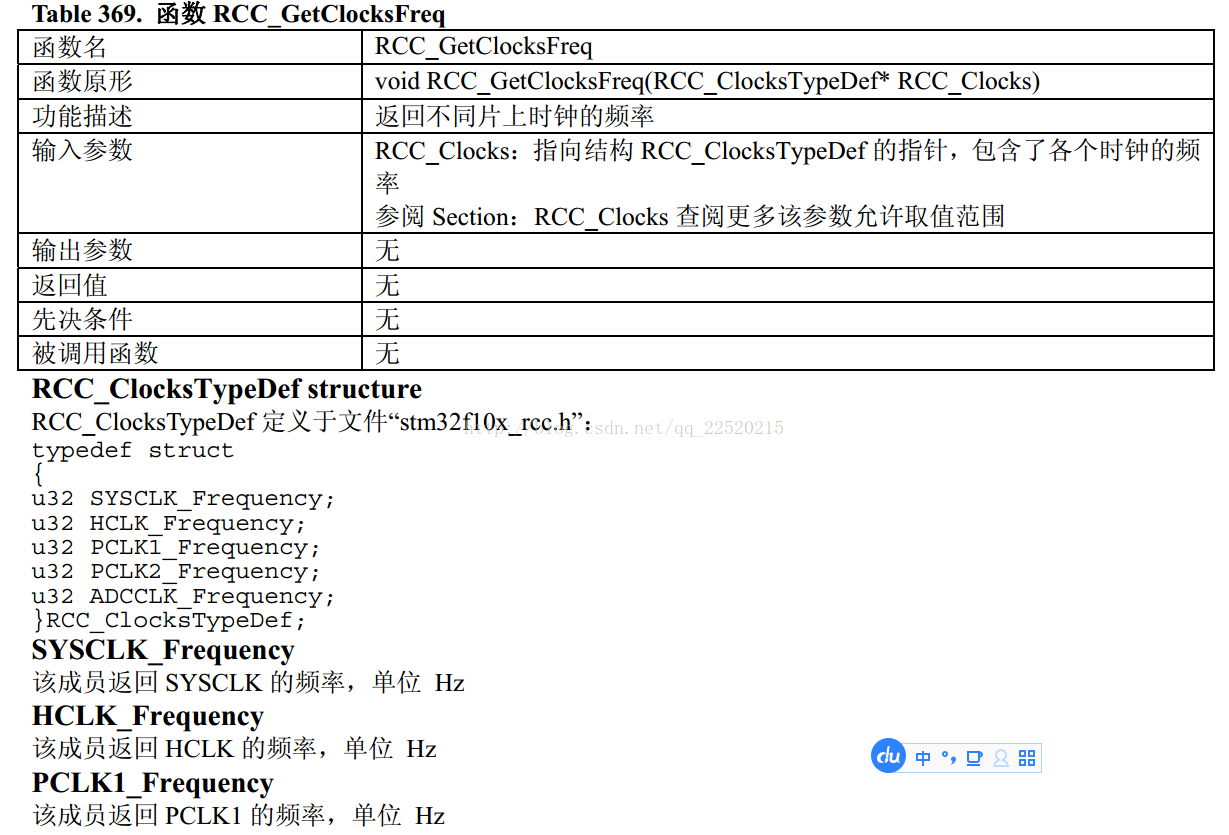

最后我用一个库函数RCC_GetClocksFreq() 它是用来获取各个时钟的频率的!他要先初始化,就在开始前利用RCC_ClocksTypeDef 来使他初始化,我们代码是RCC_ClocksTypeDef RCC_Clocks,这样RCC_Clocks.SYSCLK_Frequency就是系统时钟的频率了!我们串口输出就可以了!

主函数代码:

int main (void)

{

RCC_ClocksTypeDef RCC_Clocks; //初始化

SystemInit(); //调用刚才改过的函数

NVIC_PriorityGroupConfig(NVIC_PriorityGroup_2);

Usart_Init(115200); //串口为了看数据而已

RCC_GetClocksFreq(&RCC_Clocks); //获取各个时钟频率

while(1)

{

printf("SYSCLK_Frequency %d \r\n",RCC_Clocks.SYSCLK_Frequency);

//printf("SYSCLK_Frequency %d \r\n",RCC_Clocks.SYSCLK_Frequency);

}

}

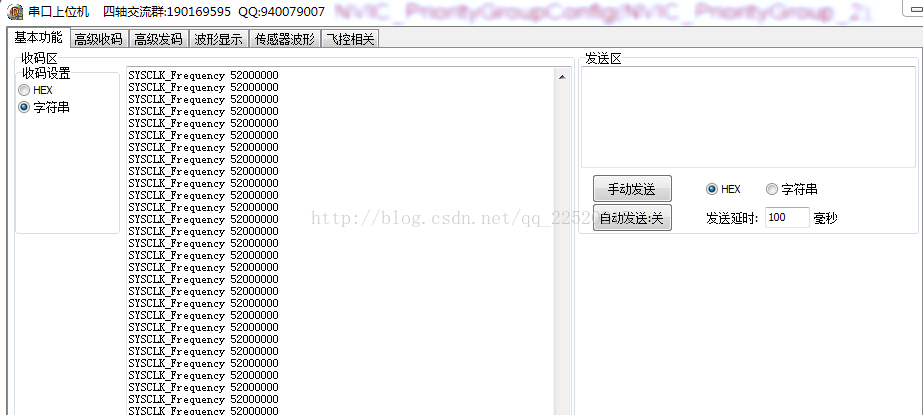

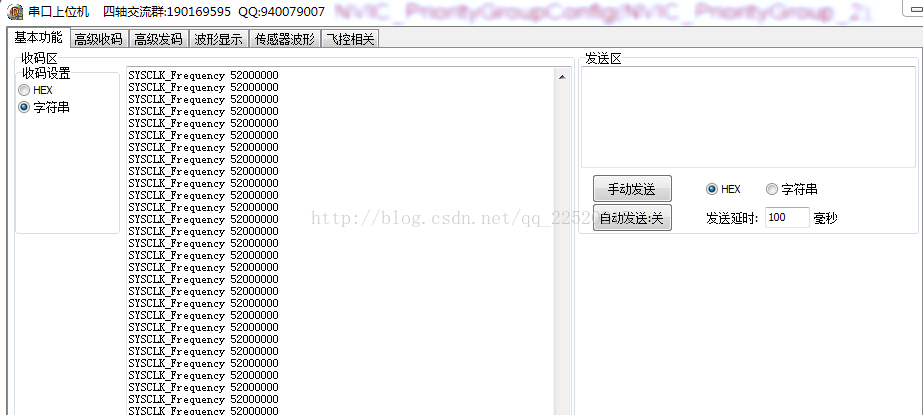

串口显示:(我的实验利用内部晶振最高只能倍频到52MHz)

本文是利用内部晶振(HSI)来倍频,与外部晶振倍频区分开!

第一步:打开system_STM32f10x.c,找到函数void SystemInit (void){},把原有的都注释掉,将下面的代码复制进去:

/* 开启HSI 即内部晶振时钟 */

RCC->CR |= (uint32_t)0x00000001;

/*选择HSI为PLL的时钟源HSI必须2分频给PLL*/

RCC->CFGR |= (uint32_t)RCC_CFGR_PLLSRC_HSI_Div2;

/*PLLCLK=8/2*13=52MHz 设置倍频得到时钟源PLL的频率*/

RCC->CFGR |= (uint32_t)RCC_CFGR_PLLMULL13;

/* PLL不分频输出 */

RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1;

/* 使能 PLL时钟 */

RCC->CR |= RCC_CR_PLLON;

/* 等待PLL时钟就绪*/

while((RCC->CR & RCC_CR_PLLRDY) == 0)

{

}

/* 选择PLL为系统时钟的时钟源 */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));

RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL;

/* 等到PLL成为系统时钟的时钟源*/

while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)0x08)

{

}

这段代码其实就是是HSI倍频成为PLL的时钟源,又使PLL成为系统时钟的时钟源,这样就相当于HSI倍频后给系统时钟了!

最后我用一个库函数RCC_GetClocksFreq() 它是用来获取各个时钟的频率的!他要先初始化,就在开始前利用RCC_ClocksTypeDef 来使他初始化,我们代码是RCC_ClocksTypeDef RCC_Clocks,这样RCC_Clocks.SYSCLK_Frequency就是系统时钟的频率了!我们串口输出就可以了!

主函数代码:

int main (void)

{

RCC_ClocksTypeDef RCC_Clocks; //初始化

SystemInit(); //调用刚才改过的函数

NVIC_PriorityGroupConfig(NVIC_PriorityGroup_2);

Usart_Init(115200); //串口为了看数据而已

RCC_GetClocksFreq(&RCC_Clocks); //获取各个时钟频率

while(1)

{

printf("SYSCLK_Frequency %d \r\n",RCC_Clocks.SYSCLK_Frequency);

//printf("SYSCLK_Frequency %d \r\n",RCC_Clocks.SYSCLK_Frequency);

}

}

串口显示:(我的实验利用内部晶振最高只能倍频到52MHz)

相关文章推荐

- 【STM32F103攻城笔记】外部晶振HSE倍频设置系统时钟

- 不用晶振,STM32内部HSI时钟的倍频使用

- 【裸机开发笔记】6410的系统时钟设置(上)---6410时钟控制逻辑框架分

- stm32 时钟配置——外部时钟倍频、内部时钟倍频 【worldsing笔记】

- 【裸机开发笔记】6410的系统时钟设置(下)---几个常用函数的C源码。

- 【裸机开发笔记】6410的系统时钟设置(中)---相关寄存器介绍

- STM32F103 使用HSI配置系统时钟为64MHZ

- 【裸机开发笔记】6410的系统时钟设置(下)---几个常用函数的C源码。

- 【裸机开发笔记】6410的系统时钟设置(上)---6410时钟控制逻辑框架分析

- 【裸机开发笔记】6410的系统时钟设置(中)---相关寄存器介绍

- 公司内部系统的网络映射设置问题

- C#.NET通用权限管理系统组件中数据集权限设置功能增加内部组织机构选项功能

- 《嵌入式linux应用程序开发完全手册》系统时钟和定时器学习笔记系统时钟和定时器

- C#.NET通用权限管理系统组件中数据集权限设置功能增加内部组织机构选项功能

- 操作系统学习笔记(2)--内核系统设置

- ARM学习笔记--系统时钟和定时器

- 系统时钟学习笔记

- 6410的系统时钟设置(中)---相关寄存器介绍

- linux 系统管理笔记 2. --- ubuntu root初始密码设置

- 6410的系统时钟设置(上)---6410时钟控制逻辑框架分析