Makefile文件的编写

2016-06-05 17:58

399 查看

先举个栗子

:

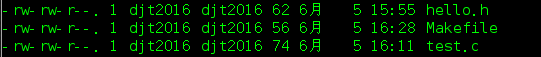

一个工程项目中有这么几个文件:

(ps:这可能算不上是一个项目

)

内容分别如下:

test.c

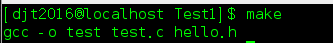

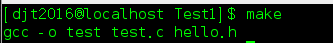

则说明我们的 test.c 文件已经编译完成

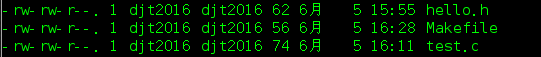

此时我们项目所在目录下面会多出一个名为 test 的可执行文件

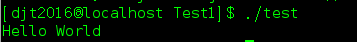

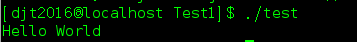

此时我们就可以直接使用 ./test 命令运行程序了

至此,任务完成

那么,有的同学可能就要问了,你想说个啥?

下面开始吹

:

通常,在一个大型项目中,会有很多个 .c 文件和 .h 文件,这些文件互相依赖互相关联,开发过程中需要多次修改代码,每当修改其中一个文件的代码时,通常需要将这些文件重新编译一次,这个过程非常麻烦。想想,不停的输入 gcc -xx xxx 命令,双手可能不保

,因此 Makefile 就应运而生了

。

简单的说,makefile定义了一系列的规则来指定,哪些文件需要先编译,哪些文件需要后编译,哪些文件需要重新编译,甚至可以在makefile中执行shell脚本。makefile带来的好处就是——“自动化编译”,一旦写好,只需要一个make命令,整个工程完全自动编译,极大的提高了软件开发的效率。

Makefile的编写规则:

target ... : prerequisites ...

command

...

...

(注意:command命令前必须有一个Tab)

target 也就是一个目标文件,可以是Object File,也可以是执行文件。还可以是一个标签(Label),对于标签这种特性,后面再说。

prerequisites 就是,要生成那个target所需要的文件或是目标。

command 也就是make需要执行的命令。(任意的Shell命令)

这是一个文件的依赖关系,也就是说,target这一个或多个的目标文件依赖于prerequisites中的文件,其生成规则定义在command中。说白一点就是说,prerequisites中如果有一个以上的文件比target文件要新的话,command所定义的命令就会被执行。这就是Makefile的规则。也就是Makefile中最核心的内容。

下面再举个简单的栗子:

如果一个工程有3个头文件,和8个C文件,我们为了完成前面所述的那三个规则,我们的Makefile文件内容如下:

edit : main.o kbd.o command.o display.o /

insert.o search.o files.o utils.o

gcc -o edit main.o kbd.o command.o display.

insert.o search.o files.o utils.o

main.o : main.c defs.h

gcc -c main.c

kbd.o : kbd.c defs.h command.h

gcc -c kbd.c

command.o : command.c defs.h command.h

gcc -c command.c

display.o : display.c defs.h buffer.h

gcc -c display.c

insert.o : insert.c defs.h buffer.h

gcc -c insert.c

search.o : search.c defs.h buffer.h

gcc -c search.c

files.o : files.c defs.h buffer.h command.h

gcc -c files.c

utils.o : utils.c defs.h

gcc -c utils.c

clean :

rm edit main.o kbd.o command.o display.o /

insert.o search.o files.o utils.o

(注:反斜杠(/)是换行符的意思,这样易读。)

将上面的内容写入到Makefile文件中,然后执行make就可以进行编译,执行make clean就可以删除所有目标文件。解释一下,也就是说生成最终的目标文件edit,依赖于一系列的.o目标文件,而这些.o文件又是需要用源文件来编译生成的。

需要注意的是,clean后面没有条件,而clean本身也不是文件,它只不过是一个动作名字,其冒号后什么也没有,那么,make就不会自动去找文件的依赖性,也就不会自动执行其后所定义的命令。

make的工作原理:

当我们输入make命令时:

1、make会在当前目录下找名字叫“Makefile”或“makefile”的文件。

2、如果找到,它会找文件中的第一个目标文件(target),在上面的例子中,他会找到“edit”这个文件,并把这个文件作为最终的目标文件。

3、如果edit文件不存在,或是edit所依赖的后面的 .o 文件的文件修改时间要比edit这个文件新,那么,他就会执行后面所定义的命令来生成edit这个文件。

4、如果edit所依赖的 .o 文件也不存在,那么make会在当前文件中找目标为.o文件的依赖性,如果找到则再根据那一个规则生成 .o 文件。(这有点像一个堆栈的过程)

5、当然,你的 .c 文件和 .h 文件是存在的啦,于是make会生成 .o 文件,然后再用 .o 文件生命make的终极任务,也就是执行文件edit了。

makefile中使用变量简化书写:

其实前面的知识已经足以让你自己完成一个简单的makefile了,不过makefile的精妙之处远不止如此,下面来看看如何在makefile中使用变量吧。

在上面的例子中,先让我们看看edit的规则:

edit : main.o kbd.o command.o display.o /

insert.o search.o files.o utils.o

gcc -o edit main.o kbd.o command.o display.o /

insert.o search.o files.o utils.o

我们可以看到 .o 文件的字符串被重复了两次,如果我们的工程需要加入一个新的 .o 文 件,那么我们需要在两个地方加(应该是三个地方,还有一个地方在clean中)。当然,我们的 makefile 并不复杂,所以在两个地方加也不累,但如果 makefile 变得复杂,那么我们就有可能会忘掉一个需要加入的地方,而导致编译失败。所以,为了makefile的易维护,在makefile 中我们 可以使用变量。makefile 的变量也就是一个字符串,理解成C语言中的宏可能会更好。

于是,我们使用变量objects(对象) objects = main.o kbd.o command.o display.o /

insert.o search.o files.o utils.o

因此,我们对原来的Makefile文件进行修改: objects = main.o kbd.o command.o display.o /

insert.o search.o files.o utils.o

edit : $(objects)

gcc -o edit $(objects)

main.o : main.c defs.h

gcc -c main.c

kbd.o : kbd.c defs.h command.h

gcc -c kbd.c

command.o : command.c defs.h command.h

gcc -c command.c

display.o : display.c defs.h buffer.h

gcc -c display.c

insert.o : insert.c defs.h buffer.h

gcc -c insert.c

search.o : search.c defs.h buffer.h

gcc -c search.c

files.o : files.c defs.h buffer.h command.h

gcc -c files.c

utils.o : utils.c defs.h

gcc -c utils.c

clean :

rm edit $(objects)

这样看起来方便多了吧,也更加省事了。如果有新的.o文件怎么办?当然是在objects里面添加了,这样只需要一处改变,方便很多。

继续简化书写:让make自动推导

GNU的make很强大,它可以自动推导文件以及文件依赖关系后面的命令,于是我们就没必要去在每一个 .o 文件后都写上类似的命令,因为,我们的make会自动识别,并自己推导命令。

只要make看到一个 .o文件,它就会自动的把 .c 文件加在依赖关系中,如果make找到一 个whatever.o,那么whatever.c,就会是whatever.o的依赖文件。并且 gcc -c whatever.c 也会被推导出来,于是,我们的makefile再也不用写得这么复杂,继续修改Makefile文件:

objects = main.o kbd.o command.o display.o /

insert.o search.o files.o utils.o

edit : $(objects)

gcc -o edit $(objects)

main.o : defs.h

kbd.o : defs.h command.h

command.o : defs.h command.h

display.o : defs.h buffer.h

insert.o : defs.h buffer.h

search.o : defs.h buffer.h

files.o : defs.h buffer.h command.h

utils.o : defs.h

clean :

rm edit $(objects)

当然,如果你觉得那么多[.o]和[.h]的依赖有点不爽的话,好吧,没有问题,这个对于make来说很容易,谁叫它提供了自动推导命令和文件的功能呢?来看看最终的makefile吧。

objects = main.o kbd.o command.o display.o /

insert.o search.o files.o utils.o

edit : $(objects)

cc -o edit $(objects)

$(objects) : defs.h

kbd.o command.o files.o : command.h

display.o insert.o search.o files.o : buffer.h

clean :

rm edit $(objects)

这种方法虽然看起来是Makefile文件更加简洁,但凡事都有两面性,这会破坏文件本身的依赖关系,如果文件过多的话,可能你自己都不清楚了。

其实 Makefile的功能很强大,这里只说了一些基础,还有很多功能和技巧没有说到(其实自己还没掌握

),后面再说

。

:

一个工程项目中有这么几个文件:

(ps:这可能算不上是一个项目

)

内容分别如下:

test.c

#include<stdio.h>

#include "hello.h"

int main()

{

hello();

return 0;

}hello.h#include<stdio.h>

void hello()

{

printf("Hello World\n");

}Makefiletest:test.c gcc -o test test.c hello.h .PHONY: clean clean: rm test此时,我们输入命令:make 会显示 gcc -o test test.c hello.h

则说明我们的 test.c 文件已经编译完成

此时我们项目所在目录下面会多出一个名为 test 的可执行文件

此时我们就可以直接使用 ./test 命令运行程序了

至此,任务完成

那么,有的同学可能就要问了,你想说个啥?

下面开始吹

:

通常,在一个大型项目中,会有很多个 .c 文件和 .h 文件,这些文件互相依赖互相关联,开发过程中需要多次修改代码,每当修改其中一个文件的代码时,通常需要将这些文件重新编译一次,这个过程非常麻烦。想想,不停的输入 gcc -xx xxx 命令,双手可能不保

,因此 Makefile 就应运而生了

。

简单的说,makefile定义了一系列的规则来指定,哪些文件需要先编译,哪些文件需要后编译,哪些文件需要重新编译,甚至可以在makefile中执行shell脚本。makefile带来的好处就是——“自动化编译”,一旦写好,只需要一个make命令,整个工程完全自动编译,极大的提高了软件开发的效率。

Makefile的编写规则:

target ... : prerequisites ...

command

...

...

(注意:command命令前必须有一个Tab)

target 也就是一个目标文件,可以是Object File,也可以是执行文件。还可以是一个标签(Label),对于标签这种特性,后面再说。

prerequisites 就是,要生成那个target所需要的文件或是目标。

command 也就是make需要执行的命令。(任意的Shell命令)

这是一个文件的依赖关系,也就是说,target这一个或多个的目标文件依赖于prerequisites中的文件,其生成规则定义在command中。说白一点就是说,prerequisites中如果有一个以上的文件比target文件要新的话,command所定义的命令就会被执行。这就是Makefile的规则。也就是Makefile中最核心的内容。

下面再举个简单的栗子:

如果一个工程有3个头文件,和8个C文件,我们为了完成前面所述的那三个规则,我们的Makefile文件内容如下:

edit : main.o kbd.o command.o display.o /

insert.o search.o files.o utils.o

gcc -o edit main.o kbd.o command.o display.

insert.o search.o files.o utils.o

main.o : main.c defs.h

gcc -c main.c

kbd.o : kbd.c defs.h command.h

gcc -c kbd.c

command.o : command.c defs.h command.h

gcc -c command.c

display.o : display.c defs.h buffer.h

gcc -c display.c

insert.o : insert.c defs.h buffer.h

gcc -c insert.c

search.o : search.c defs.h buffer.h

gcc -c search.c

files.o : files.c defs.h buffer.h command.h

gcc -c files.c

utils.o : utils.c defs.h

gcc -c utils.c

clean :

rm edit main.o kbd.o command.o display.o /

insert.o search.o files.o utils.o

(注:反斜杠(/)是换行符的意思,这样易读。)

将上面的内容写入到Makefile文件中,然后执行make就可以进行编译,执行make clean就可以删除所有目标文件。解释一下,也就是说生成最终的目标文件edit,依赖于一系列的.o目标文件,而这些.o文件又是需要用源文件来编译生成的。

需要注意的是,clean后面没有条件,而clean本身也不是文件,它只不过是一个动作名字,其冒号后什么也没有,那么,make就不会自动去找文件的依赖性,也就不会自动执行其后所定义的命令。

make的工作原理:

当我们输入make命令时:

1、make会在当前目录下找名字叫“Makefile”或“makefile”的文件。

2、如果找到,它会找文件中的第一个目标文件(target),在上面的例子中,他会找到“edit”这个文件,并把这个文件作为最终的目标文件。

3、如果edit文件不存在,或是edit所依赖的后面的 .o 文件的文件修改时间要比edit这个文件新,那么,他就会执行后面所定义的命令来生成edit这个文件。

4、如果edit所依赖的 .o 文件也不存在,那么make会在当前文件中找目标为.o文件的依赖性,如果找到则再根据那一个规则生成 .o 文件。(这有点像一个堆栈的过程)

5、当然,你的 .c 文件和 .h 文件是存在的啦,于是make会生成 .o 文件,然后再用 .o 文件生命make的终极任务,也就是执行文件edit了。

makefile中使用变量简化书写:

其实前面的知识已经足以让你自己完成一个简单的makefile了,不过makefile的精妙之处远不止如此,下面来看看如何在makefile中使用变量吧。

在上面的例子中,先让我们看看edit的规则:

edit : main.o kbd.o command.o display.o /

insert.o search.o files.o utils.o

gcc -o edit main.o kbd.o command.o display.o /

insert.o search.o files.o utils.o

我们可以看到 .o 文件的字符串被重复了两次,如果我们的工程需要加入一个新的 .o 文 件,那么我们需要在两个地方加(应该是三个地方,还有一个地方在clean中)。当然,我们的 makefile 并不复杂,所以在两个地方加也不累,但如果 makefile 变得复杂,那么我们就有可能会忘掉一个需要加入的地方,而导致编译失败。所以,为了makefile的易维护,在makefile 中我们 可以使用变量。makefile 的变量也就是一个字符串,理解成C语言中的宏可能会更好。

于是,我们使用变量objects(对象) objects = main.o kbd.o command.o display.o /

insert.o search.o files.o utils.o

因此,我们对原来的Makefile文件进行修改: objects = main.o kbd.o command.o display.o /

insert.o search.o files.o utils.o

edit : $(objects)

gcc -o edit $(objects)

main.o : main.c defs.h

gcc -c main.c

kbd.o : kbd.c defs.h command.h

gcc -c kbd.c

command.o : command.c defs.h command.h

gcc -c command.c

display.o : display.c defs.h buffer.h

gcc -c display.c

insert.o : insert.c defs.h buffer.h

gcc -c insert.c

search.o : search.c defs.h buffer.h

gcc -c search.c

files.o : files.c defs.h buffer.h command.h

gcc -c files.c

utils.o : utils.c defs.h

gcc -c utils.c

clean :

rm edit $(objects)

这样看起来方便多了吧,也更加省事了。如果有新的.o文件怎么办?当然是在objects里面添加了,这样只需要一处改变,方便很多。

继续简化书写:让make自动推导

GNU的make很强大,它可以自动推导文件以及文件依赖关系后面的命令,于是我们就没必要去在每一个 .o 文件后都写上类似的命令,因为,我们的make会自动识别,并自己推导命令。

只要make看到一个 .o文件,它就会自动的把 .c 文件加在依赖关系中,如果make找到一 个whatever.o,那么whatever.c,就会是whatever.o的依赖文件。并且 gcc -c whatever.c 也会被推导出来,于是,我们的makefile再也不用写得这么复杂,继续修改Makefile文件:

objects = main.o kbd.o command.o display.o /

insert.o search.o files.o utils.o

edit : $(objects)

gcc -o edit $(objects)

main.o : defs.h

kbd.o : defs.h command.h

command.o : defs.h command.h

display.o : defs.h buffer.h

insert.o : defs.h buffer.h

search.o : defs.h buffer.h

files.o : defs.h buffer.h command.h

utils.o : defs.h

clean :

rm edit $(objects)

当然,如果你觉得那么多[.o]和[.h]的依赖有点不爽的话,好吧,没有问题,这个对于make来说很容易,谁叫它提供了自动推导命令和文件的功能呢?来看看最终的makefile吧。

objects = main.o kbd.o command.o display.o /

insert.o search.o files.o utils.o

edit : $(objects)

cc -o edit $(objects)

$(objects) : defs.h

kbd.o command.o files.o : command.h

display.o insert.o search.o files.o : buffer.h

clean :

rm edit $(objects)

这种方法虽然看起来是Makefile文件更加简洁,但凡事都有两面性,这会破坏文件本身的依赖关系,如果文件过多的话,可能你自己都不清楚了。

其实 Makefile的功能很强大,这里只说了一些基础,还有很多功能和技巧没有说到(其实自己还没掌握

),后面再说

。

相关文章推荐

- Linux socket 初步

- Linux Kernel 4.0 RC5 发布!

- linux lsof详解

- linux 文件权限

- Linux 执行数学运算

- 10 篇对初学者和专家都有用的 Linux 命令教程

- Linux 与 Windows 对UNICODE 的处理方式

- Ubuntu12.04下QQ完美走起啊!走起啊!有木有啊!

- 解決Linux下Android开发真机调试设备不被识别问题

- 运维入门

- 运维提升

- Linux 自检和 SystemTap

- Ubuntu Linux使用体验

- c语言实现hashmap(转载)

- Linux 信号signal处理机制

- linux下mysql添加用户

- Scientific Linux 5.5 图形安装教程

- Linux 下无损图片压缩小工具介绍