STM32学习笔记13——DAC

2016-05-18 11:45

295 查看

DAC 简介

DAC 模块是 12 位电压输出数模转换器。DAC 可以按 8 位或 12 位模式进行配置,并且可与 DMA 控制器配合使用。在 12 位模式下,数据可以采用左对齐或右对齐。DAC 有两个输出 通道,每个通道各有一个转换器。在 DAC 双通道模式下,每个通道可以单独进行转换;当 两个通道组合在一起同步执行更新操作时,也可以同时进行转换。可通过一个输入参考电压引脚 VREF+ (与 ADC 共享)来提高分辨率。

DAC 主要特性

● 两个 DAC 转换器:各对应一个输出通道

● 12 位模式下数据采用左对齐或右对齐

● 同步更新功能

● 生成噪声波

● 生成三角波

● DAC 双通道单独或同时转换

● 每个通道都具有 DMA 功能

● DMA 下溢错误检测

● 通过外部触发信号进行转换

● 输入参考电压 VREF+

DAC引脚

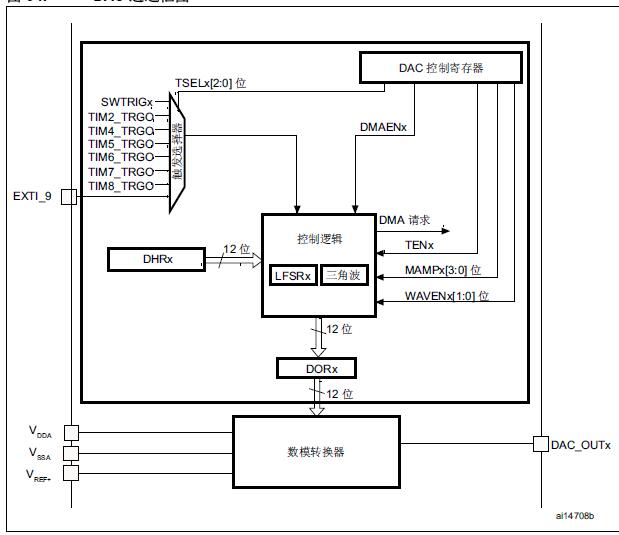

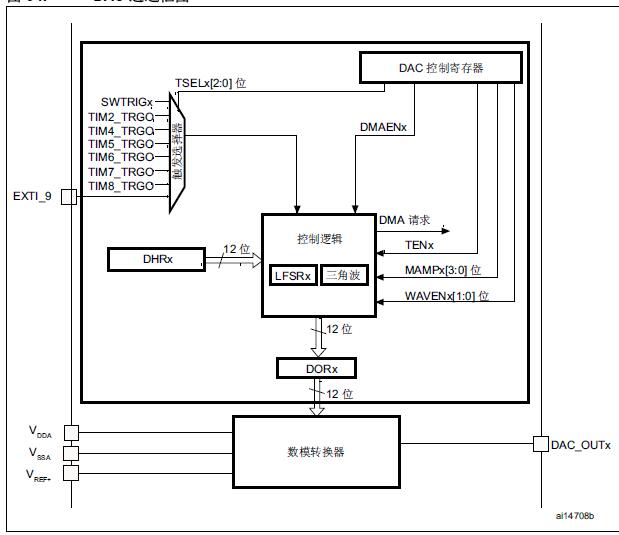

DAC功能说明

DAC 通道使能

将 DAC_CR 寄存器中的相应 ENx 位置 1,即可接通对应 DAC 通道。经过一段启动时间 tWAKEUP 后,DAC 通道被真正使能。

注意:ENx 位只会使能模拟 DAC Channelx 宏单元。即使 ENx 位复位,DAC Channelx 数字接口仍 处于使能状态。

DAC 输出缓冲器使能

DAC 集成了两个输出缓冲器,可用来降低输出阻抗并在不增加外部运算放大器的情况下直接 驱动外部负载。通过 DAC_CR 寄存器中的相应 BOFFx 位,可使能或禁止各 DAC 通道输出 缓冲器。

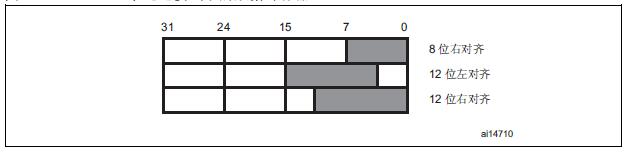

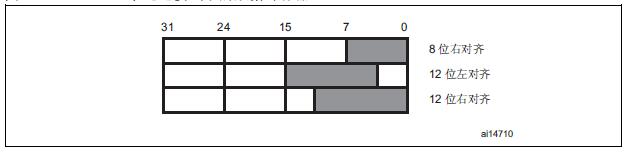

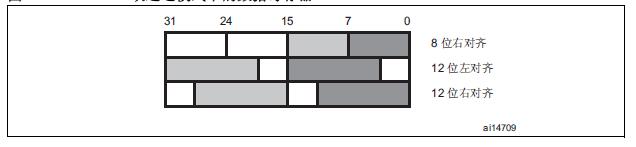

DAC 数据格式

根据所选配置模式,数据必须按如下方式写入指定寄存器:

● 对于 DAC 单通道 x,有三种可能的方式:

— 8 位右对齐:软件必须将数据加载到 DAC_DHR8Rx [7:0] 位(存储到

DHRx[11:4] 位)。

— 12 位左对齐:软件必须将数据加载到 DAC_DHR12Lx [15:4] 位(存储到

DHRx[11:0] 位)。

— 12 位右对齐:软件必须将数据加载到 DAC_DHR12Rx [11:0] 位(存储到

DHRx[11:0] 位)。

根据加载的 DAC_DHRyyyx 寄存器,用户写入的数据将移位并存储到相应的 DHRx(数据保 持寄存器 x,即内部非存储器映射寄存器)。之后,DHRx 寄存器将被自动加载,或者通过 软件或外部事件触发加载到 DORx 寄存器。

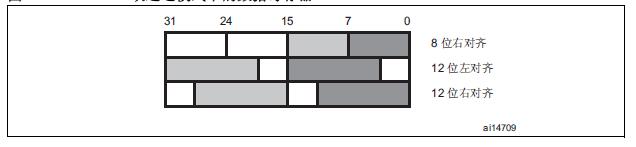

● 对于 DAC 双通道,有三种可能的方式:

— 8 位右对齐:将 DAC 1 通道的数据加载到 DAC_DHR8RD [7:0] 位(存储到

DHR1[11:4] 位),将 DAC 2 通道的数据加载到 DAC_DHR8RD [15:8] 位(存储到

DHR2[11:4] 位)

— 12 位左对齐:将 DAC 1 通道的数据加载到 DAC_DHR12RD [15:4] 位(存储到

DHR1[11:0] 位),将 DAC 2 通道的数据加载到 DAC_DHR12RD [31:20] 位(存储

到 DHR2[11:0] 位)

— 12 位右对齐:将 DAC 1 通道的数据加载到 DAC_DHR12RD [11:0] 位(存储到

DHR1[11:0] 位),将 DAC 2 通道的数据加载到 DAC_DHR12RD [27:16] 位(存储

到 DHR2[11:0] 位)

根据加载的 DAC_DHRyyyD 寄存器,用户写入的数据将移位并存储到 DHR1 和 DHR2(数 据保持寄存器,即内部非存储器映射寄存器)。之后,DHR1 和 DHR2 寄存器将被自动加 载,或者通过软件或外部事件触发分别被加载到 DOR1 和 DOR2 寄存器。

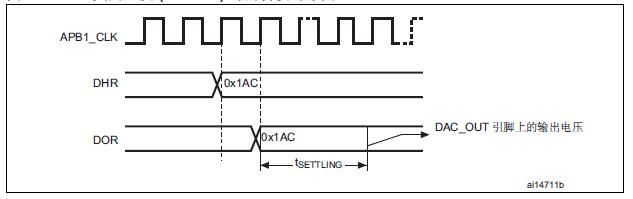

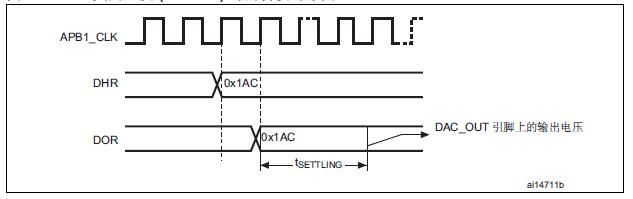

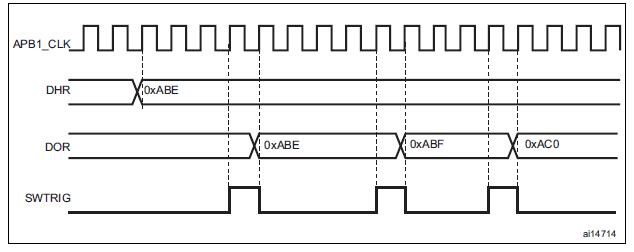

DAC 转换

DAC_DORx 无法直接写入,任何数据都必须通过加载 DAC_DHRx 寄存器(写入 DAC_DHR8Rx、DAC_DHR12Lx、DAC_DHR12Rx、DAC_DHR8RD、DAC_DHR12LD 或 DAC_DHR12LD)才能传输到 DAC 通道 x。

如果未选择硬件触发(DAC_CR 寄存器中的 TENx 位复位),那么经过一个 APB1 时钟周 期后,DAC_DHRx 寄存器中存储的数据将自动转移到 DAC_DORx 寄存器。但是,如果选 择硬件触发(置位 DAC_CR 寄存器中的 TENx 位)且触发条件到来,将在三个 APB1 时钟 周期后进行转移。

当 DAC_DORx 加载了 DAC_DHRx 内容时,模拟输出电压将在一段时间 tSETTLING 后可用, 具体时间取决于电源电压和模拟输出负载。

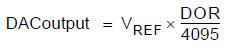

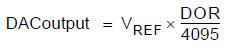

DAC 输出电压

经过线性转换后,数字输入会转换为 0 到 VREF+ 之间的输出电压。

各 DAC 通道引脚的模拟输出电压通过以下公式确定:

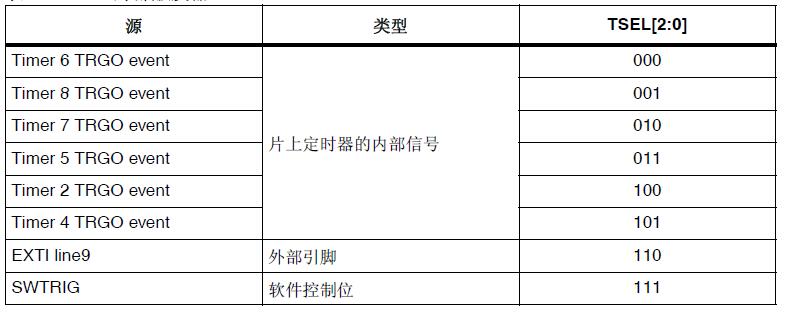

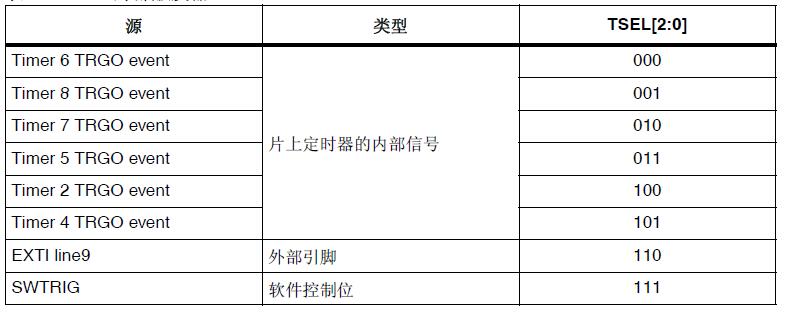

DAC 触发选择

如果 TENx 控制位置 1,可通过外部事件(定时计数器、外部中断线)触发转换。TSELx[2:0] 控制位将决定通过 8 个可能事件中的哪一个来触发转换,如表所示。

每当 DAC 接口在所选定时器 TRGO 输出或所选外部中断线 9 上检测到上升沿时,DAC_DHRx 寄存器中存储的最后一个数据即会转移到 DAC_DORx 寄存器中。发生触发后再经过三个 APB1 周期,DAC_DORx 寄存器将会得到更新。

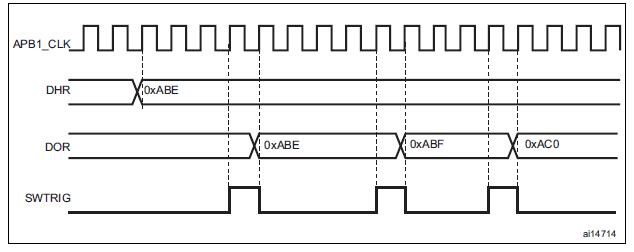

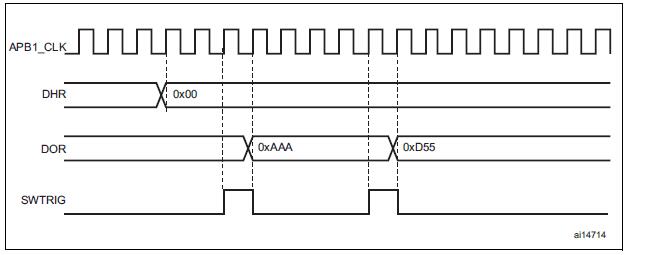

如果选择软件触发,一旦 SWTRIG 位置 1,转换即会开始。DAC_DHRx 寄存器内容加载到 DAC_DORx 寄存器中后,SWTRIG 即由硬件复位。

注意:ENx 位置 1 时,无法更改 TSELx[2:0] 位。

如果选择软件触发,DAC_DHRx 寄存器的内容只需一个 APB1 时钟周期即可转移到 DAC_DORx 寄存器。

DMA 请求

每个 DAC 通道都具有 DMA 功能。两个 DMA 通道用于处理 DAC 通道的 DMA 请求。

当 DMAENx 位置 1 时,如果发生外部触发(而不是软件触发),则将产生 DAC DMA 请 求。DAC_DHRx 寄存器的值随后转移到 DAC_DORx 寄存器。

在双通道模式下,如果两个 DMAENx 位均置 1,则将产生两个 DMA 请求。如果只需要一个 DMA 请求,应仅将相应 DMAENx 位置 1。这样,应用程序可以在双通道模式下通过一个 DMA 请求和一个特定 DMA 通道来管理两个 DAC 通道。

DMA 下溢

DAC DMA 请求没有缓冲队列。这样,如果第二个外部触发到达时尚未收到第一个外部触发 的确认,将不会发出新的请求,并且 DAC_SR 寄存器中的 DAM 通道下溢标志 DMAUDRx 将置 1,以报告这一错误状况。DMA 数据传输随即禁止,并且不再处理其他 DMA 请求。 DAC 通道仍将继续转换旧有数据。

软件应通过写入“1”来将 DMAUDRx 标志清零,将所用 DMA 数据流的 DMAEN 位清零, 并重新初始化 DMA 和 DAC 通道,以便正确地重新开始 DMA 传输。软件应修改 DAC 触发 转换频率或减轻 DMA 工作负载,以避免再次发生 DMA 下溢。最后,可通过使能 DMA 数据 传输和转换触发来继续完成 DAC 转换。

对于各 DAC 通道,如果使能 DAC_CR 寄存器中相应的 DMAUDRIEx 位,还将产生中断。

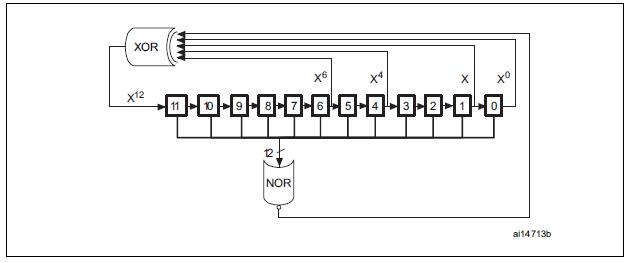

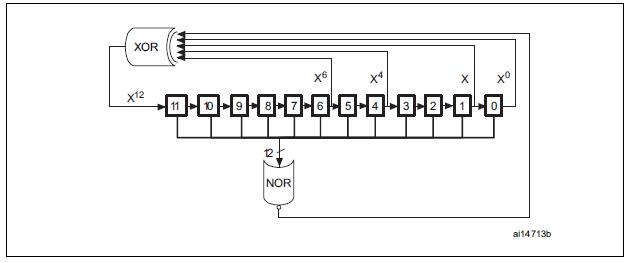

生成噪声

为了生成可变振幅的伪噪声,可使用 LFSR(线性反馈移位寄存器)。将 WAVEx[1:0] 置为 “01”即可选择生成噪声。LFSR 中的预加载值为 0xAAA。在每次发生触发事件后,经过三 个 APB1 时钟周期,该寄存器会依照特定的计算算法完成更新。

LFSR 值可以通过 DAC_CR 寄存器中的 MAMPx[3:0] 位来部分或完全屏蔽,在不发生溢出的 情况下,该值将与 DAC_DHRx 的内容相加,然后存储到 DAC_DORx 寄存器中。

如果 LFSR 为 0x0000,将向其注入“1”(防锁定机制)。

可以通过复位 WAVEx[1:0] 位来将 LFSR 波形产生功能关闭。

注意:要生成噪声,必须通过将 DAC_CR 寄存器中的 TENx 位置 1 来使能 DAC 触发。

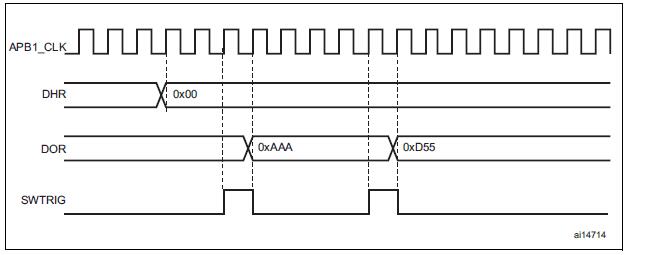

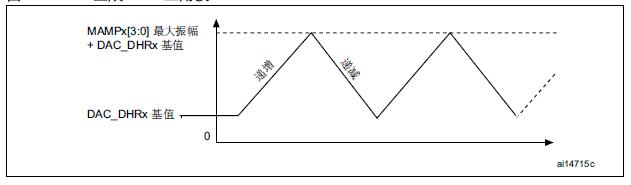

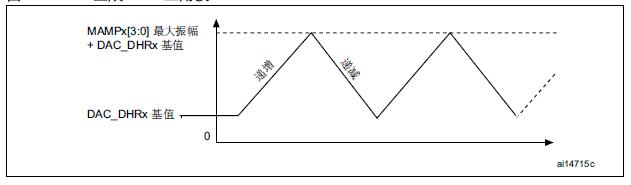

生成三角波

可以在直流电流或慢变信号上叠加一个小幅三角波。将 WAVEx[1:0] 置为“10”即可选择 DAC 生成三角波。振幅通过 DAC_CR 寄存器中的 MAMPx[3:0] 位进行配置。每次发生触发 事件后,经过三个 APB1 时钟周期,内部三角波计数器将会递增。在不发生溢出的情况下, 该计数器的值将与 DAC_DHRx 寄存器内容相加,所得总和将存储到 DAC_DORx 寄存器 中。只要小于 MAMPx[3:0] 位定义的最大振幅,三角波计数器就会一直递增。一旦达到配置 的振幅,计数器将递减至零,然后再递增,以此类推。

可以通过复位 WAVEx[1:0] 位来将三角波产生功能关闭。

生成DAC三角波

生成三角波波形的DAC转换(使能软件触发)

DAC 双通道转换

为了在同时需要两个 DAC 通道的应用中有效利用总线带宽,DAC 模块实现了三个双寄存器: DHR8RD、DHR12RD 和 DHR12LD。这样,只需一个寄存器访问即可同时驱动两个 DAC 通道。

通过两个 DAC 通道和这三个双寄存器可以实现 11 种转换模式。但如果需要,所有这些转换 模式也都可以通过单独的 DHRx 寄存器来实现。

具体模式详见F4参考手册

STM32F4的DAC库

DAC通道

STM32支持两个DAC通道,可以使用独立或者双端模式。

DAC通道1使用DAC_OUT1(PA4)做为输出

DAC通道2使用DAC_OUT2(PA5)作为输出

DAC触发

DAC转换器可以通过DAC_Trigger_None配置成非触发模式,一旦DAC_SetChannel1Data()/DAC_SetChannelData()函数写数据到DHRx寄存器将产生DAC_OUT1/DAC_OUT2输出。

DAC可以通过下面三种方式进行触发

1.外部事件触发:通过DAC_Trigger_Ext_IT9将EXTI Line 9与仍和GPIO9相连接。相应的GPIOx_Pin9必须配置成输入模式。

2.定时器触发:TIM2,TIM4,TIM5,TIM6,TIM7,TIM8(DAC_Trigger_T2_TRGO,DAC_Trigger_T4_TRGO…)通过函数TIM_SelectOutputTrigger()选择定时器触发事件。

3.通过DAC_Trigger_Software配置成软件触发。

DAC缓存模式特性

每个DAC通道都支持DAC缓存模式以减少输出阻抗,从而不需要额外正价运算放大器来驱动外部负载。使能DAC输出缓冲需要执行下面配置1DAC_InitStructure.DAC_OutputBuffer= DAC_OutputBuffer_Enable;

在使用输出缓冲和不适用输出换从的情况下,输出阻抗的大小可以通过参考数据手册获得。

DAC生成波形

通过DAC_WaveGeneration_noise配置产生噪声。

通过DAC_WaveGenertion_Triangle配置产生三角波。

DAC数据格式

通过DAC_Align_8b_R配置成8位数据右对齐。

通过DAC_Align_12b_L配置成12为数据左对齐。

通过DAC_Align_12b_R配置成12位数据右对齐。

DAC数据到电压值的转换

DAC_OUTx = VREF+*DOR/4095

DOR:表示DAC输出数据寄存器。

VREF+:表示输入参考电压。

举一个例子:若果要DAC_OUT1输出0.7v的电压,可以通过下面的函数来实现DAC_SetChannel1Data(DAC_Align_12b_R,868);

假设VREF+=3.3v,DAC_OUT1=(3.3*868)/4095 = 0.7V

DMA请求

通过DAC_DMACmd()使能DAC的DMA通道1.DMA请求的映射关系如下:

DAC通道1映射到DMA1 Stream5 channel7

DAC通道2映射到DMA1 Stream6 channel7

DAC的驱动方法

通过使能DAC时钟RCC_APB1PeriphClockCmd(RCC_APB1Periph_DAC,ENABLE).

配置DAC_OUTx(DAC_OUT1: PA4, DAC_OUT2: PA5)为模拟模式。

通过DAC_Init()初始化DAC。

通过函数DAC_Cmd()使能DAC。

DAC 模块是 12 位电压输出数模转换器。DAC 可以按 8 位或 12 位模式进行配置,并且可与 DMA 控制器配合使用。在 12 位模式下,数据可以采用左对齐或右对齐。DAC 有两个输出 通道,每个通道各有一个转换器。在 DAC 双通道模式下,每个通道可以单独进行转换;当 两个通道组合在一起同步执行更新操作时,也可以同时进行转换。可通过一个输入参考电压引脚 VREF+ (与 ADC 共享)来提高分辨率。

DAC 主要特性

● 两个 DAC 转换器:各对应一个输出通道

● 12 位模式下数据采用左对齐或右对齐

● 同步更新功能

● 生成噪声波

● 生成三角波

● DAC 双通道单独或同时转换

● 每个通道都具有 DMA 功能

● DMA 下溢错误检测

● 通过外部触发信号进行转换

● 输入参考电压 VREF+

DAC引脚

DAC功能说明

DAC 通道使能

将 DAC_CR 寄存器中的相应 ENx 位置 1,即可接通对应 DAC 通道。经过一段启动时间 tWAKEUP 后,DAC 通道被真正使能。

注意:ENx 位只会使能模拟 DAC Channelx 宏单元。即使 ENx 位复位,DAC Channelx 数字接口仍 处于使能状态。

DAC 输出缓冲器使能

DAC 集成了两个输出缓冲器,可用来降低输出阻抗并在不增加外部运算放大器的情况下直接 驱动外部负载。通过 DAC_CR 寄存器中的相应 BOFFx 位,可使能或禁止各 DAC 通道输出 缓冲器。

DAC 数据格式

根据所选配置模式,数据必须按如下方式写入指定寄存器:

● 对于 DAC 单通道 x,有三种可能的方式:

— 8 位右对齐:软件必须将数据加载到 DAC_DHR8Rx [7:0] 位(存储到

DHRx[11:4] 位)。

— 12 位左对齐:软件必须将数据加载到 DAC_DHR12Lx [15:4] 位(存储到

DHRx[11:0] 位)。

— 12 位右对齐:软件必须将数据加载到 DAC_DHR12Rx [11:0] 位(存储到

DHRx[11:0] 位)。

根据加载的 DAC_DHRyyyx 寄存器,用户写入的数据将移位并存储到相应的 DHRx(数据保 持寄存器 x,即内部非存储器映射寄存器)。之后,DHRx 寄存器将被自动加载,或者通过 软件或外部事件触发加载到 DORx 寄存器。

● 对于 DAC 双通道,有三种可能的方式:

— 8 位右对齐:将 DAC 1 通道的数据加载到 DAC_DHR8RD [7:0] 位(存储到

DHR1[11:4] 位),将 DAC 2 通道的数据加载到 DAC_DHR8RD [15:8] 位(存储到

DHR2[11:4] 位)

— 12 位左对齐:将 DAC 1 通道的数据加载到 DAC_DHR12RD [15:4] 位(存储到

DHR1[11:0] 位),将 DAC 2 通道的数据加载到 DAC_DHR12RD [31:20] 位(存储

到 DHR2[11:0] 位)

— 12 位右对齐:将 DAC 1 通道的数据加载到 DAC_DHR12RD [11:0] 位(存储到

DHR1[11:0] 位),将 DAC 2 通道的数据加载到 DAC_DHR12RD [27:16] 位(存储

到 DHR2[11:0] 位)

根据加载的 DAC_DHRyyyD 寄存器,用户写入的数据将移位并存储到 DHR1 和 DHR2(数 据保持寄存器,即内部非存储器映射寄存器)。之后,DHR1 和 DHR2 寄存器将被自动加 载,或者通过软件或外部事件触发分别被加载到 DOR1 和 DOR2 寄存器。

DAC 转换

DAC_DORx 无法直接写入,任何数据都必须通过加载 DAC_DHRx 寄存器(写入 DAC_DHR8Rx、DAC_DHR12Lx、DAC_DHR12Rx、DAC_DHR8RD、DAC_DHR12LD 或 DAC_DHR12LD)才能传输到 DAC 通道 x。

如果未选择硬件触发(DAC_CR 寄存器中的 TENx 位复位),那么经过一个 APB1 时钟周 期后,DAC_DHRx 寄存器中存储的数据将自动转移到 DAC_DORx 寄存器。但是,如果选 择硬件触发(置位 DAC_CR 寄存器中的 TENx 位)且触发条件到来,将在三个 APB1 时钟 周期后进行转移。

当 DAC_DORx 加载了 DAC_DHRx 内容时,模拟输出电压将在一段时间 tSETTLING 后可用, 具体时间取决于电源电压和模拟输出负载。

DAC 输出电压

经过线性转换后,数字输入会转换为 0 到 VREF+ 之间的输出电压。

各 DAC 通道引脚的模拟输出电压通过以下公式确定:

DAC 触发选择

如果 TENx 控制位置 1,可通过外部事件(定时计数器、外部中断线)触发转换。TSELx[2:0] 控制位将决定通过 8 个可能事件中的哪一个来触发转换,如表所示。

每当 DAC 接口在所选定时器 TRGO 输出或所选外部中断线 9 上检测到上升沿时,DAC_DHRx 寄存器中存储的最后一个数据即会转移到 DAC_DORx 寄存器中。发生触发后再经过三个 APB1 周期,DAC_DORx 寄存器将会得到更新。

如果选择软件触发,一旦 SWTRIG 位置 1,转换即会开始。DAC_DHRx 寄存器内容加载到 DAC_DORx 寄存器中后,SWTRIG 即由硬件复位。

注意:ENx 位置 1 时,无法更改 TSELx[2:0] 位。

如果选择软件触发,DAC_DHRx 寄存器的内容只需一个 APB1 时钟周期即可转移到 DAC_DORx 寄存器。

DMA 请求

每个 DAC 通道都具有 DMA 功能。两个 DMA 通道用于处理 DAC 通道的 DMA 请求。

当 DMAENx 位置 1 时,如果发生外部触发(而不是软件触发),则将产生 DAC DMA 请 求。DAC_DHRx 寄存器的值随后转移到 DAC_DORx 寄存器。

在双通道模式下,如果两个 DMAENx 位均置 1,则将产生两个 DMA 请求。如果只需要一个 DMA 请求,应仅将相应 DMAENx 位置 1。这样,应用程序可以在双通道模式下通过一个 DMA 请求和一个特定 DMA 通道来管理两个 DAC 通道。

DMA 下溢

DAC DMA 请求没有缓冲队列。这样,如果第二个外部触发到达时尚未收到第一个外部触发 的确认,将不会发出新的请求,并且 DAC_SR 寄存器中的 DAM 通道下溢标志 DMAUDRx 将置 1,以报告这一错误状况。DMA 数据传输随即禁止,并且不再处理其他 DMA 请求。 DAC 通道仍将继续转换旧有数据。

软件应通过写入“1”来将 DMAUDRx 标志清零,将所用 DMA 数据流的 DMAEN 位清零, 并重新初始化 DMA 和 DAC 通道,以便正确地重新开始 DMA 传输。软件应修改 DAC 触发 转换频率或减轻 DMA 工作负载,以避免再次发生 DMA 下溢。最后,可通过使能 DMA 数据 传输和转换触发来继续完成 DAC 转换。

对于各 DAC 通道,如果使能 DAC_CR 寄存器中相应的 DMAUDRIEx 位,还将产生中断。

生成噪声

为了生成可变振幅的伪噪声,可使用 LFSR(线性反馈移位寄存器)。将 WAVEx[1:0] 置为 “01”即可选择生成噪声。LFSR 中的预加载值为 0xAAA。在每次发生触发事件后,经过三 个 APB1 时钟周期,该寄存器会依照特定的计算算法完成更新。

LFSR 值可以通过 DAC_CR 寄存器中的 MAMPx[3:0] 位来部分或完全屏蔽,在不发生溢出的 情况下,该值将与 DAC_DHRx 的内容相加,然后存储到 DAC_DORx 寄存器中。

如果 LFSR 为 0x0000,将向其注入“1”(防锁定机制)。

可以通过复位 WAVEx[1:0] 位来将 LFSR 波形产生功能关闭。

注意:要生成噪声,必须通过将 DAC_CR 寄存器中的 TENx 位置 1 来使能 DAC 触发。

生成三角波

可以在直流电流或慢变信号上叠加一个小幅三角波。将 WAVEx[1:0] 置为“10”即可选择 DAC 生成三角波。振幅通过 DAC_CR 寄存器中的 MAMPx[3:0] 位进行配置。每次发生触发 事件后,经过三个 APB1 时钟周期,内部三角波计数器将会递增。在不发生溢出的情况下, 该计数器的值将与 DAC_DHRx 寄存器内容相加,所得总和将存储到 DAC_DORx 寄存器 中。只要小于 MAMPx[3:0] 位定义的最大振幅,三角波计数器就会一直递增。一旦达到配置 的振幅,计数器将递减至零,然后再递增,以此类推。

可以通过复位 WAVEx[1:0] 位来将三角波产生功能关闭。

生成DAC三角波

生成三角波波形的DAC转换(使能软件触发)

DAC 双通道转换

为了在同时需要两个 DAC 通道的应用中有效利用总线带宽,DAC 模块实现了三个双寄存器: DHR8RD、DHR12RD 和 DHR12LD。这样,只需一个寄存器访问即可同时驱动两个 DAC 通道。

通过两个 DAC 通道和这三个双寄存器可以实现 11 种转换模式。但如果需要,所有这些转换 模式也都可以通过单独的 DHRx 寄存器来实现。

具体模式详见F4参考手册

STM32F4的DAC库

DAC通道

STM32支持两个DAC通道,可以使用独立或者双端模式。

DAC通道1使用DAC_OUT1(PA4)做为输出

DAC通道2使用DAC_OUT2(PA5)作为输出

DAC触发

DAC转换器可以通过DAC_Trigger_None配置成非触发模式,一旦DAC_SetChannel1Data()/DAC_SetChannelData()函数写数据到DHRx寄存器将产生DAC_OUT1/DAC_OUT2输出。

DAC可以通过下面三种方式进行触发

1.外部事件触发:通过DAC_Trigger_Ext_IT9将EXTI Line 9与仍和GPIO9相连接。相应的GPIOx_Pin9必须配置成输入模式。

2.定时器触发:TIM2,TIM4,TIM5,TIM6,TIM7,TIM8(DAC_Trigger_T2_TRGO,DAC_Trigger_T4_TRGO…)通过函数TIM_SelectOutputTrigger()选择定时器触发事件。

3.通过DAC_Trigger_Software配置成软件触发。

DAC缓存模式特性

每个DAC通道都支持DAC缓存模式以减少输出阻抗,从而不需要额外正价运算放大器来驱动外部负载。使能DAC输出缓冲需要执行下面配置1DAC_InitStructure.DAC_OutputBuffer= DAC_OutputBuffer_Enable;

在使用输出缓冲和不适用输出换从的情况下,输出阻抗的大小可以通过参考数据手册获得。

DAC生成波形

通过DAC_WaveGeneration_noise配置产生噪声。

通过DAC_WaveGenertion_Triangle配置产生三角波。

DAC数据格式

通过DAC_Align_8b_R配置成8位数据右对齐。

通过DAC_Align_12b_L配置成12为数据左对齐。

通过DAC_Align_12b_R配置成12位数据右对齐。

DAC数据到电压值的转换

DAC_OUTx = VREF+*DOR/4095

DOR:表示DAC输出数据寄存器。

VREF+:表示输入参考电压。

举一个例子:若果要DAC_OUT1输出0.7v的电压,可以通过下面的函数来实现DAC_SetChannel1Data(DAC_Align_12b_R,868);

假设VREF+=3.3v,DAC_OUT1=(3.3*868)/4095 = 0.7V

DMA请求

通过DAC_DMACmd()使能DAC的DMA通道1.DMA请求的映射关系如下:

DAC通道1映射到DMA1 Stream5 channel7

DAC通道2映射到DMA1 Stream6 channel7

DAC的驱动方法

通过使能DAC时钟RCC_APB1PeriphClockCmd(RCC_APB1Periph_DAC,ENABLE).

配置DAC_OUTx(DAC_OUT1: PA4, DAC_OUT2: PA5)为模拟模式。

通过DAC_Init()初始化DAC。

通过函数DAC_Cmd()使能DAC。

相关文章推荐

- iOS开发之手势识别

- 连通性总结

- 说说WeakReference弱引用

- Cloneable接口和Object的clone()方法

- Open-E DSS V7 应用系列之六 构建软件iSCSI

- Open-E DSS V7 应用系列之六 构建软件iSCSI

- 利用java求积分(定积分和无穷限积分)

- this与super关键字总结

- mac下Android Studio常用的一些快捷键

- iOS开发之自定义表情键盘(组件封装与自动布局)

- 内存管理总结-autoreleasePool

- 前端交互开发微体验--总结了一些国内外炫酷的网站

- IOC模式及Unity框架文章收藏

- Scrum 项目5.0--软件工程

- JDBC学习2:为什么要写Class.forName("XXX")?

- delphi const的用法

- java学习个人笔记---finally模块的陷阱

- 克隆虚拟机系统(linux)

- 如何捕获java线程中的逃逸的异常

- UI基础第二天(代码)