Voltage Level-Shifter Output Waveform

2015-09-18 23:07

671 查看

http://www.cypress.com/knowledge-base-article/interfacing-sram-jtag-signals-using-voltage-level-shifter-kba81536

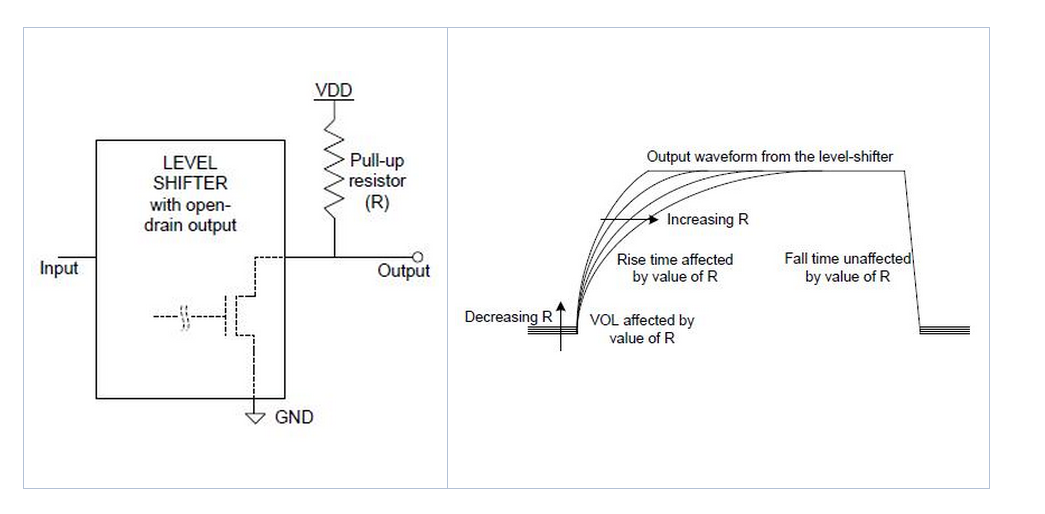

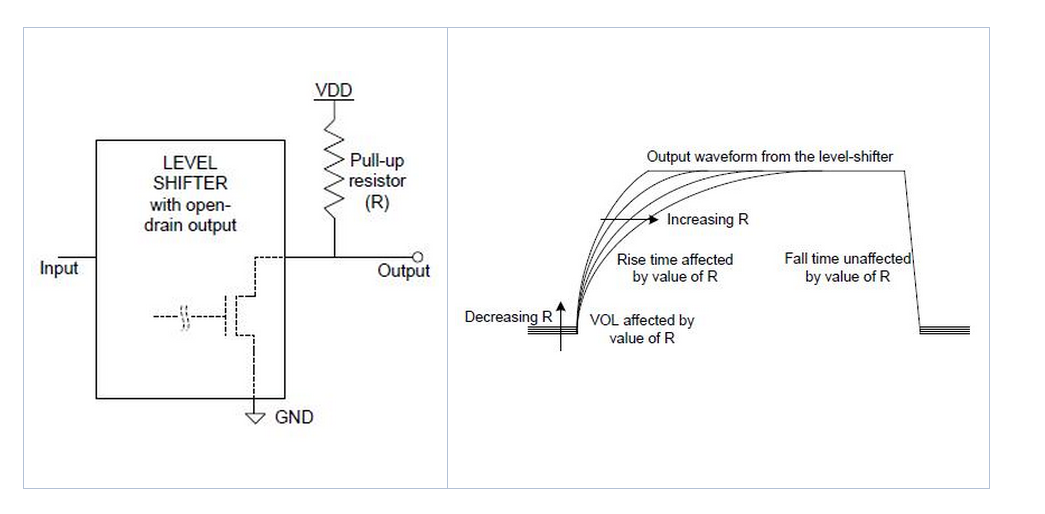

As a best practice, avoid use of level-shifting ICs with open-drain output.

This type of level-shifter requires a resistive pull-up to achieve output high voltage (VOH).

The slew rate of signal from level-shifting IC going to the memory device depends on the value of the pull-up resistor;

the higher the resistor value, the lower the slew rate and vice-versa.

Figure 2 shows the output waveform from this type of level-shifter.

Figure 2: Effect of Pull-up Resistor on Signal Rise Time for Level-Shifter IC with Open Drain Output

[align=center] [/align]

If the open-drain output level-shifting IC is already built into the system,

the problem of false clock/signal trigger can be mitigated by use of a smaller resistor value

at the expense of a slightly higher VOL signal from the level-shifting IC.

Identification of the optimal value requires experimentation with various pull-up resistor values.

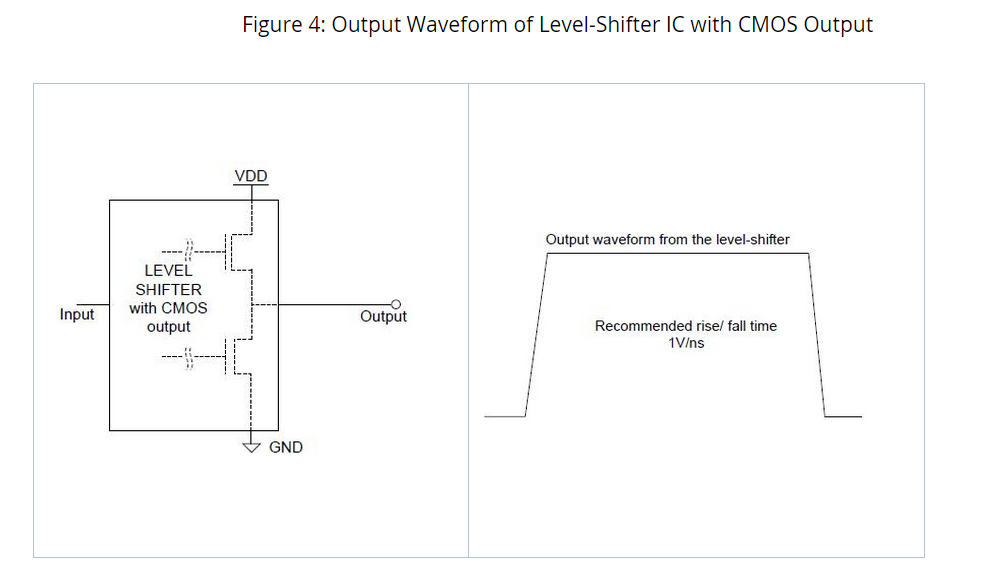

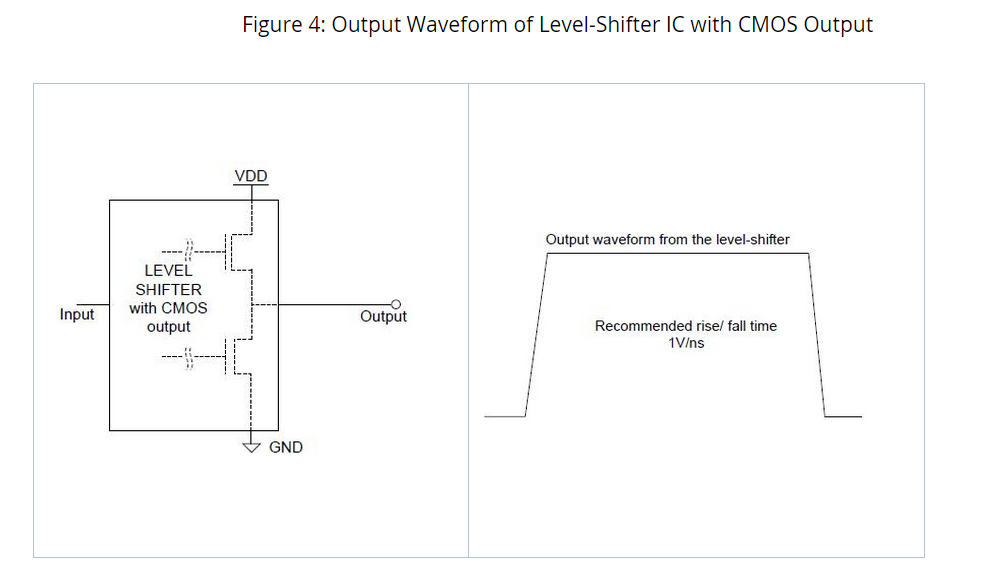

Cypress recommends the use of level-shifting ICs that provide CMOS rail-to-rail output.

This produces a strongly driven VOH/ VOL signal from the level-shifting IC to and from the memory device.

We also recommend maintaining the signal rise and fall time equal to or better than 1 V/ns.

Figure 4 shows the output waveform for this type of level-shifter.

As a best practice, avoid use of level-shifting ICs with open-drain output.

This type of level-shifter requires a resistive pull-up to achieve output high voltage (VOH).

The slew rate of signal from level-shifting IC going to the memory device depends on the value of the pull-up resistor;

the higher the resistor value, the lower the slew rate and vice-versa.

Figure 2 shows the output waveform from this type of level-shifter.

Figure 2: Effect of Pull-up Resistor on Signal Rise Time for Level-Shifter IC with Open Drain Output

[align=center] [/align]

If the open-drain output level-shifting IC is already built into the system,

the problem of false clock/signal trigger can be mitigated by use of a smaller resistor value

at the expense of a slightly higher VOL signal from the level-shifting IC.

Identification of the optimal value requires experimentation with various pull-up resistor values.

Cypress recommends the use of level-shifting ICs that provide CMOS rail-to-rail output.

This produces a strongly driven VOH/ VOL signal from the level-shifting IC to and from the memory device.

We also recommend maintaining the signal rise and fall time equal to or better than 1 V/ns.

Figure 4 shows the output waveform for this type of level-shifter.

相关文章推荐

- phpcmsv9最新高危sql注入exp

- phpStrom主题包分享

- PHP安全之register_globals

- thinkphp中foreach标签中有参数

- Scalaz(4)- typeclass:标准类型-Equal,Order,Show,Enum

- Scalaz(4)- typeclass:标准类型-Equal,Order,Show,Enum

- __FILE__ php解析

- PHP环境搭建(Windows8.1+IIS8.5+PHP5.6+PHPStorm)

- PHP版本中的VC6,VC9,VC11,TS,NTS区别

- 源码编译安装vsftpd3.0.2

- php连接sqlserver

- php输出字体颜色时遇到的小问题

- 使用thinkphp的好处和缺点

- sqlite特性 只能添加字段 不能修改字段 的解决方法 和php sqlite的管理工具 sqlbuddy

- PHP strtr与str_replace函数性能简单测试

- curl在php中的使用

- thinkphp框架之关于网站语言包的设置和使用(多语言支持)

- Elasticsearch-PHP 快速开始

- 【笔记】PHP面向对象编程——特殊实践(DAY 4)

- windows下的php rabbit mq安装、配置