【原创】科研训练指导手册(DE2-115_labs_vhdl)-PART7--实验六

2012-03-05 12:40

525 查看

6.实验6:状态机

Part I :简单的序列检测状态机

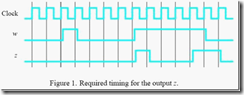

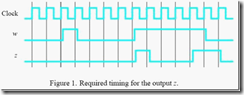

实现一个FSM用于识别2中指定的输入序列:4个1或4个0。输入信号为w,输出为z。当连续4个时钟w=1或0时,z=1;否则,z=0.序列允许重合,比如连续5个时钟w=1,在第4,5个时钟z=1。图7.1描述了w和z的关系。

图7.1 w和z的关系

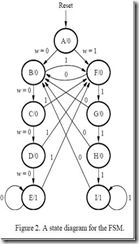

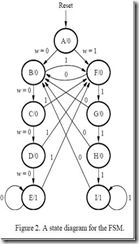

状态图如图7.2所示。用9个触发器,状态编码用独热码,实现本FSM。

表7.1 独热码编码 图7.2 状态图

在DE2-115上按以下步骤实现设计:

1. 为FSM项目创建一个新的Quartus II项目。选定目标芯片。

2. 例化9个触发器。只用assign语句。注意,独热码便于检查逻辑表达式。使用开关SW0作为FSM的同步复位(低有效)。SW1作为w的输入,按键KEY0作为clock输入。LEDG0作为输出z,状态输出到LEDR8到LEDR0.

3. 分配引脚,编译。

4. 仿真。

5.仿真正确后,下载验证。

Part 1代码:

Part II :另一种风格的状态机

用赋值和case语句代替手工推导的逻辑表达式,来实现part1中的状态机。

按以下步骤实现电路:

1. 为FSM创建一个新工程。指定目标芯片。

2. 引脚功能:SW0—复位、SW1—w输入、KEY0—clock、LEDG0—z、:LEDR3-0—状态。

3. 编译之前,必须设定综合工具以指定的状态编码实现FSM。选择Assignments > Setting > Analysis and Synthsis 将State Machine Processing 设为User-encoded。

4. 打开RTL Viewer工具查看Quartus II生成的电路。双击电路图中表示状态机的方框图,查看状态图。要查看状态编码,可在编译报告里选择Analysis and Synthesis > State M:achines.

5. 仿真。

6. 下载测试。

7. 修改,在第3步,选择Assignments > Settings > Analysis and Synthesis > State Machine Processing > One-Hot。重新编译,查看区别。

Part 2代码:

Part I :简单的序列检测状态机

实现一个FSM用于识别2中指定的输入序列:4个1或4个0。输入信号为w,输出为z。当连续4个时钟w=1或0时,z=1;否则,z=0.序列允许重合,比如连续5个时钟w=1,在第4,5个时钟z=1。图7.1描述了w和z的关系。

图7.1 w和z的关系

状态图如图7.2所示。用9个触发器,状态编码用独热码,实现本FSM。

表7.1 独热码编码 图7.2 状态图

在DE2-115上按以下步骤实现设计:

1. 为FSM项目创建一个新的Quartus II项目。选定目标芯片。

2. 例化9个触发器。只用assign语句。注意,独热码便于检查逻辑表达式。使用开关SW0作为FSM的同步复位(低有效)。SW1作为w的输入,按键KEY0作为clock输入。LEDG0作为输出z,状态输出到LEDR8到LEDR0.

3. 分配引脚,编译。

4. 仿真。

5.仿真正确后,下载验证。

Part 1代码:

LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY part1 IS PORT ( KEY : IN STD_LOGIC_VECTOR(0 DOWNTO 0); SW : IN STD_LOGIC_VECTOR(1 DOWNTO 0); LEDG : OUT STD_LOGIC_VECTOR(0 DOWNTO 0); LEDR : OUT STD_LOGIC_VECTOR(8 DOWNTO 0) ); END part1; ARCHITECTURE Behavior OF part1 IS -- Declare intermediate signals for referenced outputs SIGNAL LEDG_x : STD_LOGIC_VECTOR(0 DOWNTO 0); SIGNAL LEDR_x : STD_LOGIC_VECTOR(8 DOWNTO 0); component sequence_detector PORT ( w : IN STD_LOGIC; clk : IN STD_LOGIC; rst_n : IN STD_LOGIC; z : OUT STD_LOGIC; state : OUT STD_LOGIC_VECTOR(8 DOWNTO 0) ); END component; BEGIN -- Drive referenced outputs LEDG <= LEDG_x; LEDR <= LEDR_x; u0 : sequence_detector PORT MAP ( w => SW(1), --序列检测器的输入信号 clk => KEY(0), --时钟 rst_n => SW(0), --复位 z => LEDG_x(0), --序列检测器的输出信号 state => LEDR_x --FSM的状态,编码方式为独热码 ); END Behavior; LIBRARY ieee; USE ieee.std_logic_1164.all; --序列检测器,能识别连续输入的4个1或0 --风格一,直接用逻辑表达式来实现 ENTITY sequence_detector IS PORT ( w : IN STD_LOGIC; clk : IN STD_LOGIC; rst_n : IN STD_LOGIC; z : OUT STD_LOGIC; state : OUT STD_LOGIC_VECTOR(8 DOWNTO 0) ); END sequence_detector; ARCHITECTURE Behavior OF sequence_detector IS SIGNAL D : STD_LOGIC_VECTOR(8 DOWNTO 0); --9个触发器的输入/出 SIGNAL Q : STD_LOGIC_VECTOR(8 DOWNTO 0); component ff PORT ( d : IN STD_LOGIC; clk : IN STD_LOGIC; rst_n : IN STD_LOGIC; set_n : IN STD_LOGIC; q : OUT STD_LOGIC ); END component; BEGIN --用9个触发器构成状态机 D(0) <= '0'; --初始状态A da : ff PORT MAP ( d => D(0), clk => clk, rst_n => '1', set_n => rst_n, q => Q(0) ); D(1) <= (Q(0) OR Q(5) OR Q(6) OR Q(7) OR Q(8)) AND NOT(w); --状态b db : ff PORT MAP ( d => D(1), clk => clk, rst_n => rst_n, set_n => '1', q => Q(1) ); D(2) <= Q(1) AND NOT(w); --状态c dc : ff PORT MAP ( d => D(2), clk => clk, rst_n => rst_n, set_n => '1', q => Q(2) ); D(3) <= Q(2) AND NOT(w); --状态d dd : ff PORT MAP ( d => D(3), clk => clk, rst_n => rst_n, set_n => '1', q => Q(3) ); D(4) <= (Q(3) OR Q(4)) AND NOT(w); --状态e de : ff PORT MAP ( d => D(4), clk => clk, rst_n => rst_n, set_n => '1', q => Q(4) ); D(5) <= (Q(0) OR Q(1) OR Q(2) OR Q(3) OR Q(4)) AND w; --状态f df : ff PORT MAP ( d => D(5), clk => clk, rst_n => rst_n, set_n => '1', q => Q(5) ); D(6) <= Q(5) AND w; --状态g dg : ff PORT MAP ( d => D(6), clk => clk, rst_n => rst_n, set_n => '1', q => Q(6) ); D(7) <= Q(6) AND w; --状态h dh : ff PORT MAP ( d => D(7), clk => clk, rst_n => rst_n, set_n => '1', q => Q(7) ); D(8) <= (Q(7) OR Q(8)) AND w;--状态i di : ff PORT MAP ( d => D(8), clk => clk, rst_n => rst_n, set_n => '1', q => Q(8) ); z <= Q(4) OR Q(8); state <= Q; END Behavior; LIBRARY ieee; USE ieee.std_logic_1164.all; --具有同步复位和置位功能的dff ENTITY ff IS PORT ( d : IN STD_LOGIC; clk : IN STD_LOGIC; rst_n : IN STD_LOGIC; set_n : IN STD_LOGIC; q : OUT STD_LOGIC ); END ff; ARCHITECTURE Behavior OF ff IS BEGIN PROCESS (clk) BEGIN IF (clk'EVENT AND clk = '1') THEN IF ((NOT(rst_n)) = '1') THEN q <= '0'; ELSIF ((NOT(set_n)) = '1') THEN q <= '1'; ELSE q <= d; END IF; END IF; END PROCESS; END Behavior;

Part II :另一种风格的状态机

用赋值和case语句代替手工推导的逻辑表达式,来实现part1中的状态机。

按以下步骤实现电路:

1. 为FSM创建一个新工程。指定目标芯片。

2. 引脚功能:SW0—复位、SW1—w输入、KEY0—clock、LEDG0—z、:LEDR3-0—状态。

3. 编译之前,必须设定综合工具以指定的状态编码实现FSM。选择Assignments > Setting > Analysis and Synthsis 将State Machine Processing 设为User-encoded。

4. 打开RTL Viewer工具查看Quartus II生成的电路。双击电路图中表示状态机的方框图,查看状态图。要查看状态编码,可在编译报告里选择Analysis and Synthesis > State M:achines.

5. 仿真。

6. 下载测试。

7. 修改,在第3步,选择Assignments > Settings > Analysis and Synthesis > State Machine Processing > One-Hot。重新编译,查看区别。

Part 2代码:

LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY lab7_part2 IS PORT ( clk, w, rst: in std_logic; z: out std_logic); END lab7_part2; ARCHITECTURE Behavior OF lab7_part2 IS TYPE State_type IS (A, B, C, D, E, F, G, H, I); SIGNAL present_state, next_state : State_type; BEGIN PROCESS (w, present_state) BEGIN case present_state IS WHEN A => z<='0'; IF (w = '0') THEN next_state <= B; ELSE next_state <= F; END IF; WHEN B => z<='0'; IF (w = '0') THEN next_state <= C; ELSE next_state <= F; END IF; WHEN C => z<='0'; IF (w = '0') THEN next_state <= D; ELSE next_state <= F; END IF; WHEN D => z<='0'; IF (w = '0') THEN next_state <= E; ELSE next_state <= F; END IF; WHEN E => z<='1'; IF (w = '0') THEN next_state <= E; ELSE next_state <= F; END IF; WHEN F => z<='0'; IF (w = '0') THEN next_state <= B; ELSE next_state <= G; END IF; WHEN G => z<='0'; IF (w = '0') THEN next_state <= B; ELSE next_state <= H; END IF; WHEN H => z<='0'; IF (w = '0') THEN next_state <= B; ELSE next_state <= I; END IF; WHEN I => z<='1'; IF (w = '0') THEN next_state <= B; ELSE next_state <= I; END IF; END CASE; END PROCESS; PROCESS (clk,rst) BEGIN if rst = '1' then present_state <= A; elsif rising_edge(clk) then present_state <= next_state; end if; END PROCESS; END Behavior;

相关文章推荐

- 【原创】科研训练指导手册(DE2-115_labs_vhdl)-PART2--实验一

- 【原创】科研训练指导手册(DE2-115_labs_vhdl)-PART3--实验二

- 【原创】科研训练指导手册(DE2-115_labs_vhdl)-PART4--实验三

- 【原创】科研训练指导手册(DE2-115_labs_vhdl)-PART5--实验四

- 【原创】科研训练指导手册(DE2-115_labs_vhdl)-PART6--实验五

- 【原创】科研训练指导手册(DE2-115_labs_vhdl)-PART8--附录

- RBM训练指导手册粗略(A Practical Guide to Training Restricted Boltzmann Machines)

- 【原创】DE2 实验练习解答—lab4 counters【verilog】【digital logic】

- 【原创】DE2 实验练习解答—lab 2:数字和显示(digital Logic)(DE2)

- 【原创】基于Altera DE2的数字实验—001_3 (DE2)(Digital Logical)(Verilog)

- 【原创】SD卡WAV音乐播放器(quartus11.0)(FAT32)(DE2-115)

- (原创) DE2 实验练习解答—lab 1 (Digital Logic) (DE2) (Quartus II)

- 【原创】DE2 实验练习解答—lab 3:锁存器、触发器和寄存器(digital Logic)(DE2)(quartus II)

- 网络工程师交换试验手册之三:默认网关实验(扩展训练)

- 【原创】基于DE2-115的8点FFT实现

- 实验07《训练功能的用户界面编程》实验指导书

- 【原创】基于Altera DE2的数字实验—001_1 (DE2)(Digital Logical)(Verilog)

- 网络工程师交换试验手册之三:默认网关实验(扩展训练)

- [转帖](原创) 深入探讨inout port (SOC) (Verilog) (VHDL) (Quartus II) (SignalTap II) (DE2-70)

- 实验08《训练功能的业务逻辑编程》实验指导书V07-2初稿