【原创】基于Altera DE2的数字实验—001_3 (DE2)(Digital Logical)(Verilog)

2011-05-14 16:59

633 查看

Project 3

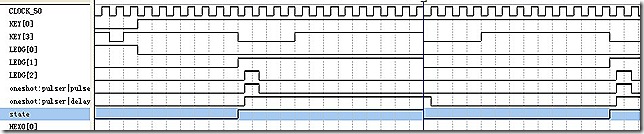

本实验实现一个定时器。KEY3可以启动和停止计时。KEY0复位(计数停止)。基本思路就是利用Project 2的分频时钟100Hz驱动十进制的计数器,将4个十进制的计数器串联,那么在HEX3-2上显示的数字就以S递增。本实验包含以下内容:

1. 顶层模块的设计。2. 单稳态脉冲的生成。

3. 编译报告。

设计

1. 顶层模块(1)设置状态变量和计数器

hex_7seg.v

module hex_7seg(hex_digit,seg);

input [3:0] hex_digit;

output [6:0] seg;

reg [6:0] seg;

// seg = {g,f,e,d,c,b,a};

// 0 is on and 1 is off

always @ (hex_digit)

case (hex_digit)

4'h0: seg = 7'b1000000;

4'h1: seg = 7'b1111001; // ---a----

4'h2: seg = 7'b0100100; // | |

4'h3: seg = 7'b0110000; // f b

4'h4: seg = 7'b0011001; // | |

4'h5: seg = 7'b0010010; // ---g----

4'h6: seg = 7'b0000010; // | |

4'h7: seg = 7'b1111000; // e c

4'h8: seg = 7'b0000000; // | |

4'h9: seg = 7'b0011000; // ---d----

4'ha: seg = 7'b0001000;

4'hb: seg = 7'b0000011;

4'hc: seg = 7'b1000110;

4'hd: seg = 7'b0100001;

4'he: seg = 7'b0000110;

4'hf: seg = 7'b0001110;

endcase

endmodule仿真结果:

参考

John S. Loomis ,diglab3.http://www.johnloomis.org/digitallab/diglab/diglab3/diglab3.html

相关文章推荐

- 【原创】基于Altera DE2的数字实验—001_2 (DE2)(Digital Logical)(Verilog)

- 【原创】基于Altera DE2的数字实验—001_1 (DE2)(Digital Logical)(Verilog)

- (原创)DE2数字逻辑实验——Mechanics of DE2 Projects-Altera DE2 Project Diglab1(DE2)(Quartus ii)(Verilog)

- 【原创】DE2 实验练习解答—lab 2:数字和显示(digital Logic)(DE2)

- 【原创】DE2 实验练习解答—lab4 counters【verilog】【digital logic】

- ALTERA DE2 之 verilog HDL 学习笔记04 -altera DE2 上 SRAM的读写

- (原创)基于or1200最小sopc系统搭建(二)--QuartuII工程及DE2平台下载

- 【原创】科研训练指导手册(DE2-115_labs_vhdl)-PART2--实验一

- 基于basys2用verilog设计多功能数字钟(重写)

- 【iCore2双核心板】SRAM 读写实验(基于Verilog语言)

- 【原创】基于FPGA的等精度测频方法(学习实验)

- [Craftor原创]基于Verilog的I2C总线驱动设计

- (原创)多功能数字钟(Digital Logic)(DE2)(QuartusII)

- 【原创】DE2 实验练习解答—lab 3:锁存器、触发器和寄存器(digital Logic)(DE2)(quartus II)

- [原创].串行ADC TLC549读取实验,Verilog版本

- 【原创】基于DE2-115的8点FFT实现

- 【原创】科研训练指导手册(DE2-115_labs_vhdl)-PART3--实验二

- [转帖](原创) 深入探讨inout port (SOC) (Verilog) (VHDL) (Quartus II) (SignalTap II) (DE2-70)

- 【原创】DE2实验解答—lab09 (Quartus II)(Verilog HDL)(Digital Logic)

- 【原创】DE2实验练习解答—lab5 Clocks and Timers 【Verilog】【Digital Logic】