我脑残实验室verilog学习笔记——5/30/2011

2011-06-06 09:59

274 查看

1、跳边沿检测和电平检测:

电平检测较为简单,只要在always中运用if(signal=1)或者if(signal=0)来检测就行,简单但有时会不满足设计的要求,这就需要跳边沿检测来弥补。但是跳变沿检测就较为麻烦,以下是一种用于跳边沿检测的方法:

always @(posedge clock) // indicate的上跳沿

begin

a <= indicate;

b <= a;

end

assign flag_indicate = ((b==0)&&(a==1))?1:0

这段程序利用了非阻塞赋值的特点,在时钟的上跳沿触发对a和b的赋值,a的值是当前的indicate的值,而b的值是前一个周期的indicate的值,最后的assign连续赋值根据a和b的值来对标志位flag_indicate赋值,本例中b为0且a为1时候说明检测到了indicate的上跳沿,将标志位置1。

2、task(任务)和function(函数)中都不允许使用always语句,因为always语句一旦触发不能停止,返回值(对函数而言)和被赋值参数(对任务而言)就会不断改变。但是《verilog数字系统设计第二版》中P84的这个例子可行:

task light

output color;

input[31:0] tics;

begin

repeat(tics) @(posedge clock)

这是因为repeat指定等待tics个时钟的上跳后沿关灯,可停止。

3、for循环的综合。只有一些简单的for循环才能被综合器综合,为了探究综合器的具体综合方法,我编了一段程序:实际上就是一个累加器,输出b是在时钟上跳沿的输入信号a累加8次得结果。

module sbox(ck, a, b );

input ck;

input[7:0] a;

output b;

reg [7:0] tmp;

reg [7:0] b;

integer k;

always @(posedge ck)

begin

tmp = 0;

for(k=0;k<8;k=k+1)

begin

tmp = tmp + a;

end

b = tmp;

end

endmodule

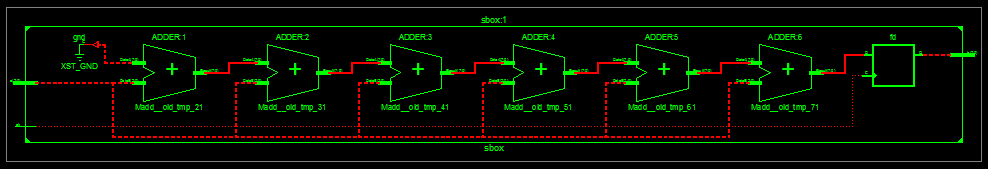

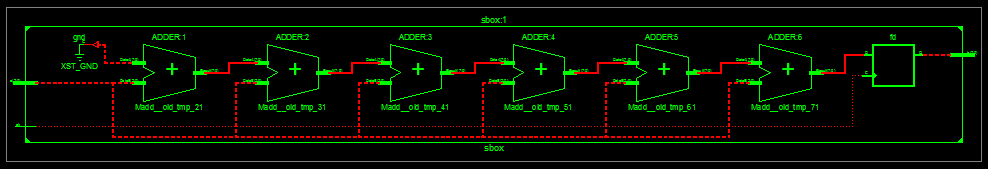

这个for循环比较简单,综合后查看RTL图:

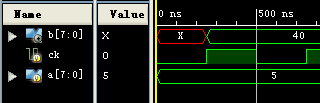

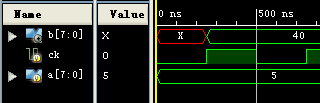

由图可知,综合器将这个for循环综合(展开)成了8个同时进行加法器(adder),因为在功能仿真中门级电路是没有时延的,所以这8次累加是在同一时刻同时完成的,最右端是由钟控触发器,将结果输出(同样也没有时延),所以用Isim仿真的图显示在上跳沿输入a=5的同时,就输出了b=40。

但是比较复杂的for循环(比如本次用到上次的结果的取模的值,取模运算比较复杂)就不能被综合器综合了,要么报错,要么警告,要么一直综合,一直处在HDL Analysis过程。所以除一些简单的循环(如初始化寄存器)之外,一般不用for循环。

电平检测较为简单,只要在always中运用if(signal=1)或者if(signal=0)来检测就行,简单但有时会不满足设计的要求,这就需要跳边沿检测来弥补。但是跳变沿检测就较为麻烦,以下是一种用于跳边沿检测的方法:

always @(posedge clock) // indicate的上跳沿

begin

a <= indicate;

b <= a;

end

assign flag_indicate = ((b==0)&&(a==1))?1:0

这段程序利用了非阻塞赋值的特点,在时钟的上跳沿触发对a和b的赋值,a的值是当前的indicate的值,而b的值是前一个周期的indicate的值,最后的assign连续赋值根据a和b的值来对标志位flag_indicate赋值,本例中b为0且a为1时候说明检测到了indicate的上跳沿,将标志位置1。

2、task(任务)和function(函数)中都不允许使用always语句,因为always语句一旦触发不能停止,返回值(对函数而言)和被赋值参数(对任务而言)就会不断改变。但是《verilog数字系统设计第二版》中P84的这个例子可行:

task light

output color;

input[31:0] tics;

begin

repeat(tics) @(posedge clock)

这是因为repeat指定等待tics个时钟的上跳后沿关灯,可停止。

3、for循环的综合。只有一些简单的for循环才能被综合器综合,为了探究综合器的具体综合方法,我编了一段程序:实际上就是一个累加器,输出b是在时钟上跳沿的输入信号a累加8次得结果。

module sbox(ck, a, b );

input ck;

input[7:0] a;

output b;

reg [7:0] tmp;

reg [7:0] b;

integer k;

always @(posedge ck)

begin

tmp = 0;

for(k=0;k<8;k=k+1)

begin

tmp = tmp + a;

end

b = tmp;

end

endmodule

这个for循环比较简单,综合后查看RTL图:

由图可知,综合器将这个for循环综合(展开)成了8个同时进行加法器(adder),因为在功能仿真中门级电路是没有时延的,所以这8次累加是在同一时刻同时完成的,最右端是由钟控触发器,将结果输出(同样也没有时延),所以用Isim仿真的图显示在上跳沿输入a=5的同时,就输出了b=40。

但是比较复杂的for循环(比如本次用到上次的结果的取模的值,取模运算比较复杂)就不能被综合器综合了,要么报错,要么警告,要么一直综合,一直处在HDL Analysis过程。所以除一些简单的循环(如初始化寄存器)之外,一般不用for循环。

相关文章推荐

- 我脑残实验室Verilog学习笔记——在Xilinx ISE中运用符号设计顶层模块的方法

- 我脑残实验室Verilog学习笔记1

- 我脑残实验室verilog学习笔记2

- 我脑残实验室Verilog学习笔记3

- 我脑残实验室Verilog学习笔记4

- JavaScript学习笔记30-数组属性和方法

- C/C++学习笔记30:C标准库函数

- IOS学习笔记30—两个ViewController间传值(一)

- Verilog学习笔记(四)

- 31天重构学习笔记30. 尽快返回

- 31天重构学习笔记30. 尽快返回

- 2011寒假-操作系统学习笔记

- 【Linux学习笔记】30:declare命令(声明/取消/查看变量类型)

- verilog状态机学习笔记

- 2011斯坦福大学iOS应用开发教程学习笔记(第一课)MVC.and.Introduction.to.Objective-C

- 31天重构学习笔记30. 尽快返回

- 有关ImplicitStyleManager组件的研究——Silverlight学习笔记[30]

- Verilog HDL语言学习笔记

- oracle 11g 学习笔记 10_30(2)_数据字典和动态性能视图

- [Android新手学习笔记30]-Broadcast-如何自定义广播