Hold Time违例,该如何解决

首先,我们要知道的是,Hold Time违例,是因为时钟绕的太远,到达时间太晚。而且综合之后给出的时序报告都是估计值,因此综合之后可以不考虑Hold Time,只考虑Setup Time;即便此时Hold Time违例,我们也不需要去理会。在Place Design之后再去看Hold Time,如果此时Hold Time的违例比较小(比如-0.05ns),还是不需要理会的,因为工具在布线时会修复Hold,但如果Slack太大了,无法修复了,就会牺牲setup来弥补hold。

这里补充一下综合实现的步骤:

synth_design -> opt_design -> place-design -> phys_opt_design -> route_design

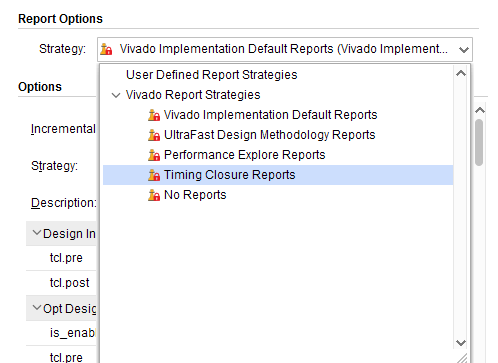

我们可以让工具在每一步执行后都会有时序报告,只需要把Report Options的策略选择为Timing Closure Reports

image-20200810165751733

image-20200810165751733

如果route design之后hold time还是违例,可以使用tcl指令:

phys_opt_design -directive ExploreWithHoldFix

这个指令会尝试不同的算法来优化hold time违例。

如果运行该指令后,hold time还是违例,又不想改设计,可以尝试不同的实现策略,但这种方式比较笨,只能试出来,并没有一个很固定的解决方案。

如果还是没有解决,只能修改设计,要么减少时钟的延迟,要么增加数据的延迟:

检查违例的时钟是否是在全局时钟网络上,若没有的话,则最好增加BUFG

插入延迟模块,在数据路径上增加逻辑延迟

FPGA时序约束教程

3. FPGA时序约束理论篇之IO约束

4. FPGA时序约束理论篇之时钟周期约束

5. FPGA时序约束理论篇之两种时序例外

6. FPGA时序约束理论篇之xdc约束优先级 7. FPGA时序约束实战篇之梳理时钟树 8. FPGA时序约束实战篇之主时钟约束 9. FPGA时序约束实战篇之衍生时钟约束 10. FPGA时序约束实战篇之延迟约束 11. FPGA时序约束实战篇之伪路径约束

12. FPGA时序约束实战篇之多周期路径约束

13. Vivado时序约束辅助工具 14. FPGA时序约束之Tcl命令的对象及属性

欢迎关注微信公众号:Quant_Times

本文分享自微信公众号 - 科学计算Tech(Quant_Times)。

如有侵权,请联系 support@oschina.cn 删除。

本文参与“OSC源创计划”,欢迎正在阅读的你也加入,一起分享。

- 以+scheduledTimerWithTimeInterval... 的方式触发的 timer,在滑动页面上的列表时, timer 会暂定回调,为什么?如何解决?

- 如何解决端口的time_wait

- 如何解决Error: failed PB timebomb check

- Linux大量TIME_WAIT如何解决

- 如何解决VS警告warning C4244: “参数”: 从“time_t”转换到“unsigned int”,可能丢失数据

- 如何解决分布式系统的Logical Time问题?(一)

- 如何解决Error: failed PB timebomb check

- 如何解决TIME_WAIT过多的解决办法(附Socket中的TIME_WAIT状态详解)

- 如何解决TIME_WAIT过多的解决办法(附Socket中的TIME_WAIT状态详解)

- 安卓原生TimePicker时间数字颜色如何改变?TimePickerUIUtil来解决这个问题

- 如何解决Error: failed PB timebomb check

- 以+scheduledTimerWithTimeInterval...的方式触发的timer,在滑动页面上的列表时,timer会暂定回调,为什么?如何解决?

- 如何解决TIME_WAIT过多的解决办法(附Socket中的TIME_WAIT状态详解)

- 如何解决TIME_WAIT过多的解决办法(附Socket中的TIME_WAIT状态详解)

- 如何解决TIME_WAIT过多的解决办法(附Socket中的TIME_WAIT状态详解)

- 如何解决端口的time_wait

- 如何解决TIME_WAIT过多的解决办法(附Socket中的TIME_WAIT状态详解)

- 如何高效的解决问题

- SecureCRT下如何解决vi背景色的问题

- 如何解决软键盘弹出引起的各种不适