FPGA SPI加载时间计算

FPGA SPI加载时间计算

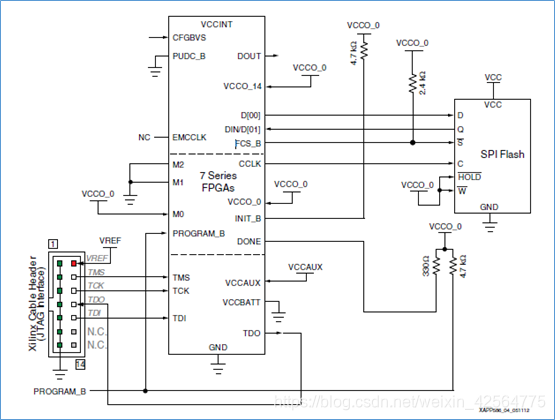

1、下图描述了1X或2X数据宽度的连接方式,2X模式下,master-out-slave-in (MOSI) 引脚为双向IO,同时作为数据引脚。

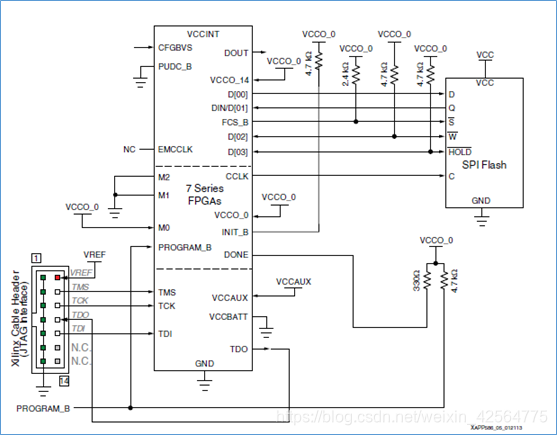

2、下图描述了4X数据宽度的连接方式。

3、FPGA采用SPI加载的注意事项

上电加载过程中,FPGA和SPI Flash都要进行自检,自检完成后FPGA将读命令发送到SPI Flash以检索配置数据,此时SPI Flash必须准备好响应此命令。通常,FPGA的自检时间(毫秒级)要长于SPI FLASH的自检时间(微秒级)。

4、FPGA的配置过程

FPGA完成自检后,INIT被释放,FPGA对模式引脚(M [2:0])进行采样,以确定使用哪种配置模式。在模式引脚M [2:0] = 001(SPI加载方式)的情况下,FPGA开始以大约3 MHz的频率在CCLK上输出时钟。而后,FCS_B拉低,开始读取SPI Flash数据。

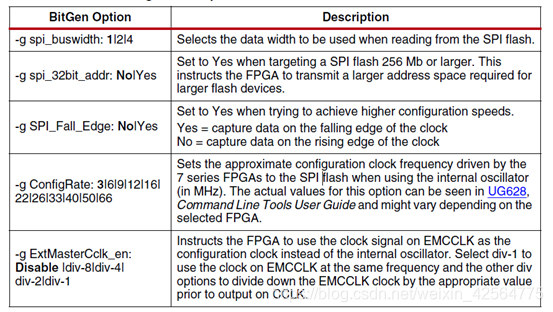

在BIT文件的前端对1X、2X、4X模式进行了配置,FPGA根据此配置进行数据加载,读取数据时,默认CCLK的下降沿从SPI Flash输出数据,CCLK的上升沿FPGA对数据进行捕获,通过使能SPI_FALL_EDGE BitGen选项,可以更改默认配置从而实现FPGA在下降沿捕获。

使用公式1来确定SPI FLASH可以安全运行的最大频率,并仍然可靠地传输比特流。对于下面的等式,假设启用了SPIFLASH配置选项,使FPGA能够在下降沿捕获数据(-g spi_fall_edge:yes)。这样可以利用整个时钟周期,因此实现高频率传输。

在7系列FPGA中,内部振荡器(fMCCKTOL)的频率容

4000

差很大。减小配置时间至关重要,建议使用外部时钟(EMCCLK)。

最大配置时钟频率 = 1/(Tspitco+Tspiddc+Ttpd) 公式1

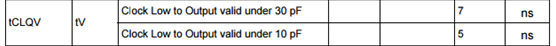

Tspitco(SPI FLASH输出时钟):根据SPI FLASH数据手册,SPI FLASH时钟输出具有多个值,具体取决于VCC和输出引脚上的电容。这里以N25Q128为例手册中对于时钟的频率范围如下图:

其范围为5到7ns之间。

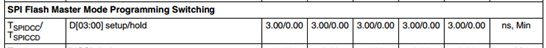

Tspiddc(FPGA data setup):Kintex-7 FPGA及Artix-7 FPGA的配置时间为3.0 ns

Ttpd(CCLK到C引脚延时时间):经验是每英寸165 ps ,为了获得更准确的结果,建议使用仿真。

在确定最佳配置速率后,设计人员需要将总比特流大小除以配置速率,以确定x1模式下的总配置时间。如果使用x2或x4数据宽度,则除以宽度。

举例:

最大配置时钟频率 = 1/(7ns+3ns+2ns)=83.3MHz,设计人员应考虑使用FPGA的内部振荡器,最接近83.3 MHz的值为66 MHz。但是,XC7K325T的频率容差(fMCCKTOL)为±50%,因此该时钟频率可能为(66 MHz x 1.5)= 99 MHz,超出了理论计算值。

下一个最快的配置速率是50 MHz,其最大频率为(50 MHz x 1.5)= 75 MHz。满足要求小于83.3MHz。

假设BIT流文件大小为91,548,896 bits(约为11MB文件),FPGA在1X模式及50MHz的配置速率下,其配置时间为 91,548,896 bits/50MHz = 1.83s

假设配置速率为80 MHz,其配置时间为 91,548,896 bits/80MHz = 1.144s,在此基础上如果为4X模式,其配置时间为 91,548,896 bits/80MHz/4 = 286ms

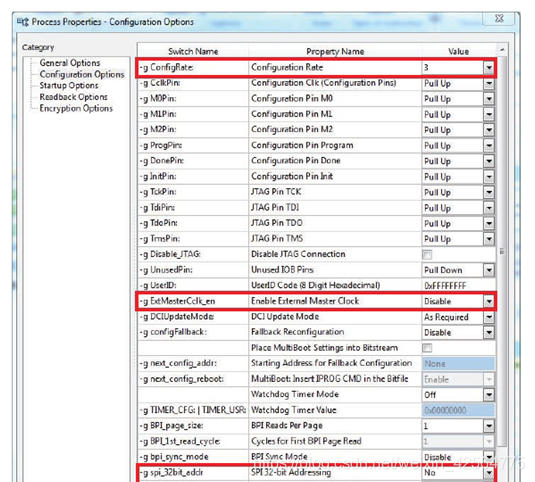

5、软件配置

黑色字体为默认配置,从菜单栏上的Process下拉菜单中选择Process Properties,然后选择Configuration Options,从窗口底部的“属性”显示级别下拉菜单中,选择“高级”以查看所有选项。

- FPGA BPI加载时间计算

- 时间序列数据库——索引用ES、聚合分析时加载数据用什么?docvalues的列存储貌似更优优势一些。那分布式计算呢?ES做

- 实例:计算页面加载时间

- 如何计算首屏加载时间?

- asp 页面执行时间,页面加载时间,timer()用法,毫秒计算

- PHP 计算页面加载时间

- php简单计算页面加载时间的方法

- asp.net页面加载时间计算方案

- web页面加载时间计算

- php简单计算页面加载时间的方法

- Flex如何计算加载时间

- asp.net页面加载时间计算

- asp.net页面加载时间计算

- 计算加载页面所用的时间

- js计算页面加载时间

- jquery利用frame计算第三方网页加载时间

- 时间序列数据库的秘密(3)——加载和分布式计算

- STM32 定时器 定时时间的计算

- <编程>比较两种素数表生成算法+计算程序运行时间+通过CMD重定向测试程序

- 为什么编程语言以及数据库要从1970年1月1日开始计算时间