Verilog学习笔记(三):计数器的设计

2018-02-14 11:58

1256 查看

计数器

●同步计数器:所有寄存器共享一个时钟●异步计数器(行波计数器):不断地分频

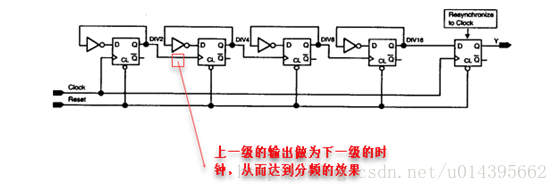

下图就是一个行波计数器的实例:

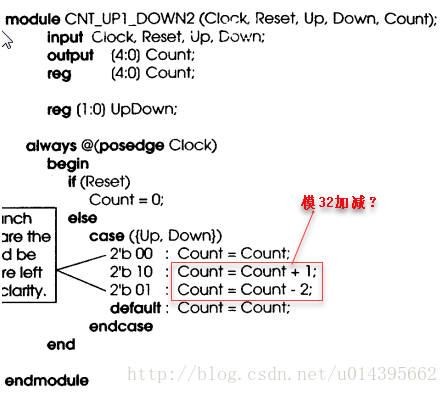

example:5-bit up-by-one down-by-two counter

小结:上述代码实现的就是最简单的同步计数器。

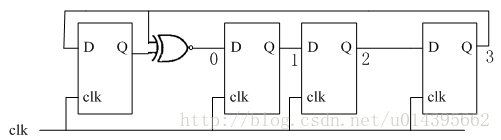

Example: 用LFSR(线性反馈移位寄存器)实现的13倍分频计数器●XNOR 4bit LFSR设计:

●XNOR 4bit LFSR状态转移图示(16进制):

0->2->6->e->d->b->7->c->9->3->4->a->5->8->1->0

从e开始,到0结束,即可实现13个时钟周期的计数

●代码:

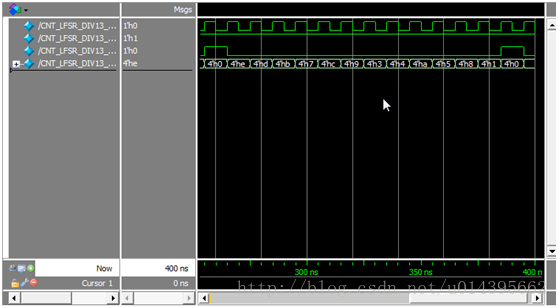

●仿真结果:

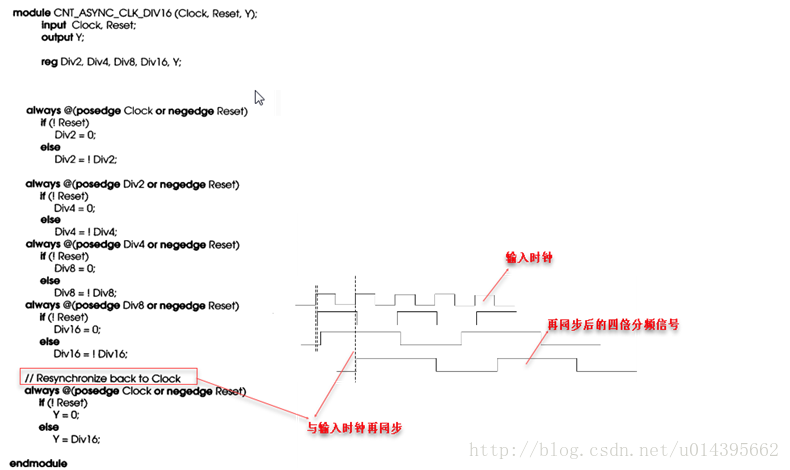

Example:用行波计数器设计16倍分频器●代码:

小结:在代码的最后有一个和时钟重新同步的过程,左边的代码写到了Div16,而右边的图只画到了Div4。

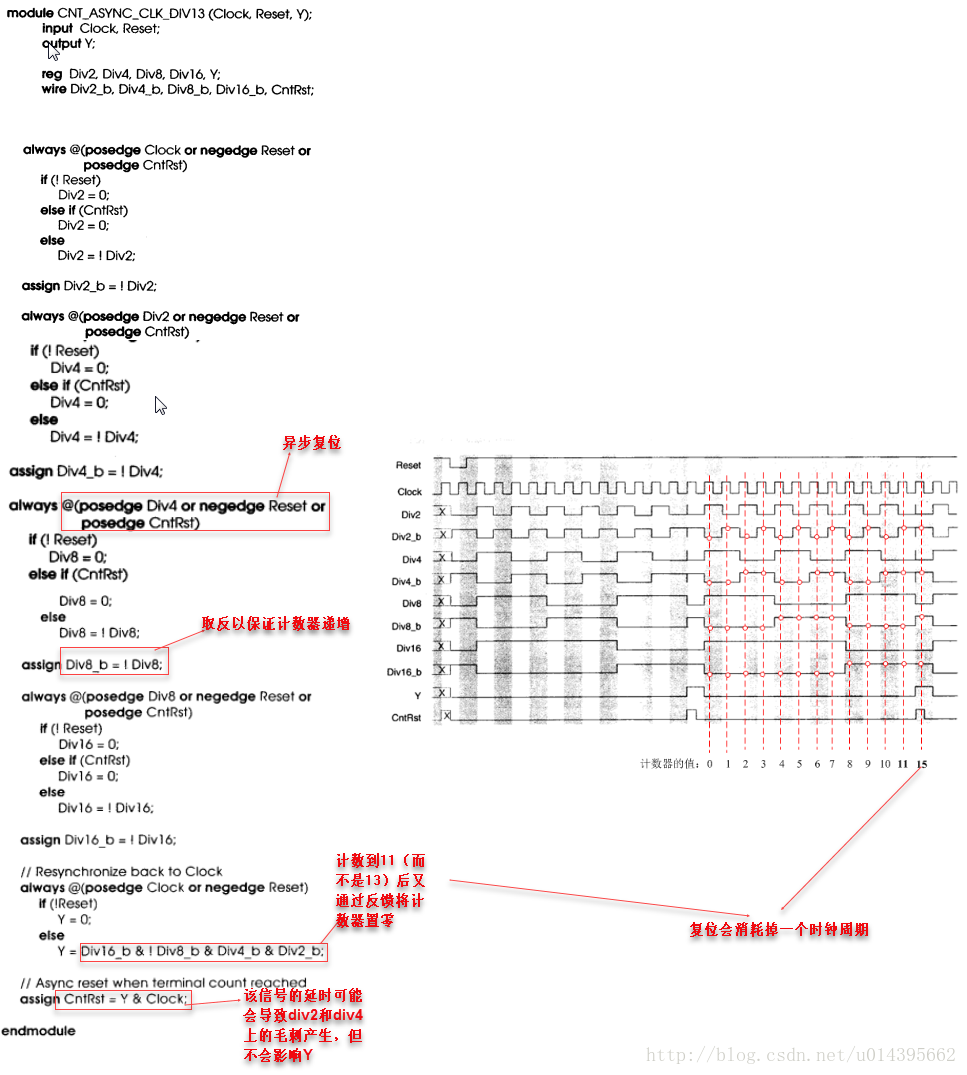

Example: 用行波计数器设计13倍分频器

小结:使用行波计数器的好处是在电路比较简单的情况下,计数器的值还会按顺序增加(用移位寄存器的话计数器的值不是按顺序增加的),不好的地方是D触发器之间数据传输会有延迟,以至于最后还需要与时钟重新同步,如果累计延迟超过一个时钟周期就会出问题。

相关文章推荐

- verilog学习笔记——8位带置位信号的计数器

- 【verilog】Verilog数字系统设计教程学习笔记(夏宇闻)《一》

- Verilog学习笔记6:层次化设计-数码管位选

- 我脑残实验室Verilog学习笔记——在Xilinx ISE中运用符号设计顶层模块的方法

- Verilog学习笔记5:层次化设计-数码管段选

- [转]Verilog数字系统设计教程(大连理工一博士学习笔记)

- 微信公号“架构师之路”学习笔记(五)-数据库扩展性架构设计(水平切分,秒级扩容,平滑迁移,在线表结构变更,一个大数据量多属性高并发的数据库设计等)

- Java学习笔记38:通过Spring Bean 注入static变量,来设计一套适合测试,开发,生产环境的配置项

- 设计模式学习笔记(七)——Adapter适配器模式

- 微软企业库4.1学习笔记(二十)缓存模块8 性能计数器

- HeadFirst 设计模式学习笔记6--适配器模式和外观模式

- 系统分析与设计学习笔记(四)领域模型

- 『框架设计(第2版)CLR Via C#』学习笔记——使用is和as操作符来进行强制类型转换

- 设计模式学习笔记——原型模式

- java/android 设计模式学习笔记(16)---命令模式

- 设计模式学习笔记——创建者模式

- Kafka/Metaq设计思想学习笔记

- Kafka/Metaq设计思想学习笔记

- 【转】数据库设计规范(学习笔记)

- 设计模式学习笔记之(一、工厂模式)