uboot启动流程详解(2)-reset

2018-02-06 08:58

267 查看

转载地址:http://blog.csdn.net/silent123go/article/details/53142329

reset是uboot最先执行的代码,接下来我们来看看reset的具体流程。

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

通过向模式位M[4:0]里写入相应的数据切换到不同的模式,在对CPSR,SPSR寄存器进行操作不能使用mov,ldr等通用指令,只能使用特权指令msr和mrs。

在ARM处理器中,只有MRS(Move to Register from State register)指令可以对状态寄存器CPSR和SPSR进行读操作。通过读CPSR可以获得当前处理器的工作状态。读SPSR寄存器可以获得进入异常前的处理器状态(因为只有异常模式下有SPSR寄存器)。

除了用户模式和系统模式,其余模式下都有一个私有SPSR保存状态寄存器,用来保存切换到该模式之前的执行状态,之所以用户模式和系统模式没有SPSR是因为,通常CPU大部分时间执行在用户模式下,当产生异常或系统调用时会分别切换进入另外几种模式,保存用户模式下的状态,当切换回原先模式时,直接回复SPSR的值到CPSR就可以了,因此,用户模式和系统模式下不需要SPSR。

mrs

将状态寄存器的内容传送至通用寄存器。

teq

TEQ R1,R2 ;将寄存器R1的值与寄存器R2的值按位异或,并根据结果设置CPSR的标志位。该指令通常用于比较操作数1和操作数2是否相等。常与EQ和NE条件码配合使用,当两个数据相等时,条件码EQ有效,否则条件码NE有效。

bic

指令格式:BIC{cond}{S} Rd,Rn,operand2

BIC指令将Rn 的值与操作数operand2 的反码按位逻辑”与”,结果存放到目的寄存器Rd 中。

指令示例:BIC R0,R0,#0x0F ;将R0最低4位清零,其余位不变。

orr

指令格式:orr {cond}{S} Rd,Rn,operand2

orr指令将操作数operand2 与Rn 的值按位逻辑"或",结果存放到目的寄存器Rd 中。

指令示例:orrs R1,R1,R2 ;R1=R1|R2,并根据运算的结果更新标志位。

orr R0,R0,#0x0F ;R0=R0|0x0F,将R0最低4位置1,其余位不变。

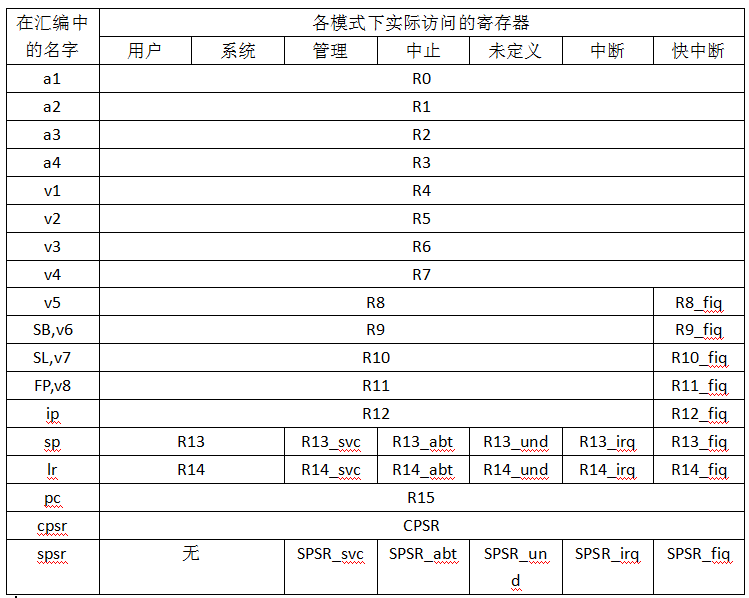

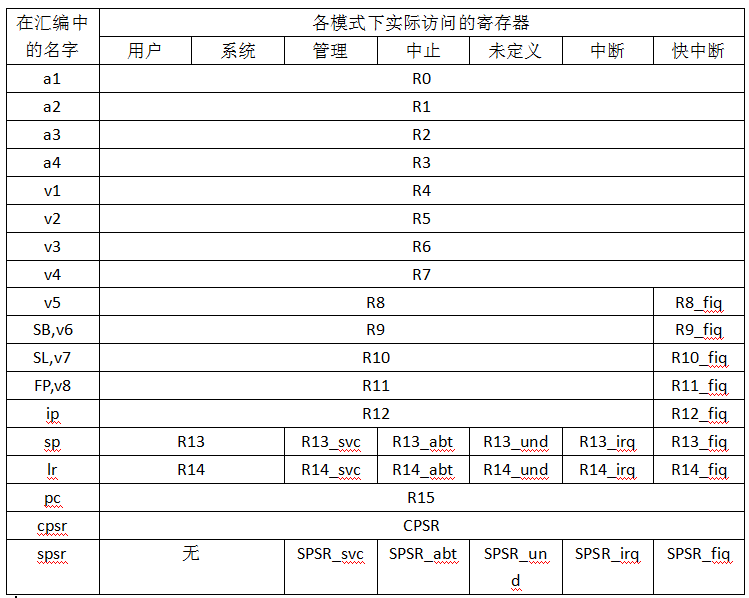

在ARM处理器内部有37个用户可见的寄存器:30个通用寄存器,6个状态寄存器(1个专用于记录当前状态,5个专用于记录模式切换前的状态),1个程序计数器PC。在不同的工作模式和处理器状态下,程序员可以访问的寄存器也不尽相同。

-31个通用寄存器:

R0~R15;

R13_svc、R14_svc;

R13_abt、R14_abt;

R13_und;R14_und;

R13_irq、R14_irq;

R8_fiq-R14_fiq

-6 个状态寄存器:

CPSR、SPSR_svc、SPSR_abt、SPSR_und、SPSR_irq和SPSR_fiq

通用寄存器包括R0~R15,可以分为三类:

─ 未分组寄存器R0~R7

─ 分组寄存器R8~R14

─ 程序计数器PC(R15)

(1)未分组寄存器R0~R7

在所有的运行模式下,未分组寄存器都指向同一个物理寄存器,他们未被系统用作特殊的用途,是真正的通用寄存器。因此,在中断或异常处理进行运行模式转换时,由于不同的处理器运行模式均使用相同的物理寄存器,可能会造成寄存器中数据的破坏,这一点在进行程序设计时应引起注意。

(2)分组的寄存器R8~R14

对于R8~R12,每一次所访问的物理寄存器,与处理器当前的工作模式有关。

一、R8~R12

当处理器工作于fiq模式时,访问的寄存器为R8_fiq~R12_fiq;

除fiq模式以外的其他模式,访问的寄存器为R8_usr~R12_usr。

二、R13和R14:

每个寄存器对应6个不同的物理寄存器,其中的一个是用户模式与系统模式共用,另外5个物理寄存器,对应于其他5种不同的异常模式。

R13:寄存器R13在ARM指令中常用作堆栈指针SP。但这只是一种习惯用法,用户也可使用其他的寄存器作为堆栈指针。而在Thumb指令集中,某些指令强制性的要求使用R13作为堆栈指针。

R14:寄存器R14也称作子程序链接寄存器(Subroutine Link Register)或链接寄存器LR。当执行BL子程序调用指令时,R14中得到R15(程序计数器PC)的备份。其他情况下,R14用作通用寄存器。与之类似,当发生中断或异常时,对应的分组寄存器R14_svc、R14_irq、R14_fiq、R14_abt和R14_und用来保存R15的返回值。

(3)程序计数器PC(R15)

寄存器R15用作程序计数器(PC)。在ARM状态下,位[1:0]为0,位[31:2]用于保存PC;在Thumb状态下,位[0]为0,位[31:1]用于保存PC。

使用R15时注意:虽然R15可以用作通用寄存器,但是有一些指令在使用R15时有一些特殊限制,若不注意,执行的结果将是不可预料的。所以,一般不这么使用。

关于PC的值:由于ARM采用多级流水线技术,所以PC总是指向正在取指的指令,而不是正在执行的指令。也即PC总是指向当前指令的下两条指令的地址。因此,对于ARM指令集而言,PC的值为当前指令的地址值加8个字节。

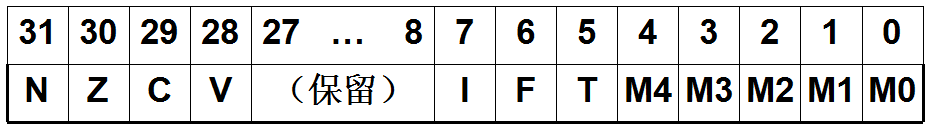

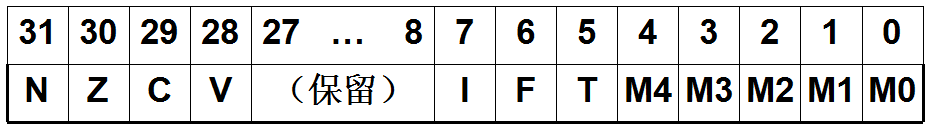

在ARM微处理器中,有CPSR和SPSR两种程序状态寄存器。

1、当前程序状态寄存器 CPSR (Current Program Status Register)用来保存当前程序状态的寄存器。所有处理器模式下都可以访问当前程序状态寄存器CPSR。仅一个CPSR。

2、保存程序状态寄存器SPSR_mode (Saved Program Status Register)SPSR_mode用来进行异常处理,其功能包括:

─ 保存ALU中的当前操作信息,当异常发生时, 用来保存CPSR的值,从异常返回时,将 SPSR_mode复制到CPSR中,恢复CPSR的值。

─ 控制允许和禁止中断 修改SPSR的值

─ 设置处理器的运行模式 修改SPSR的值

问题:一共有多少个SPSR?为什么?

ARM状态寄存器的格式

1、条件码标志位(保存ALU中的当前操作信息)

N:正负号/大小 标志位

0表示:正数/大于;1表示:负数/小于

Z:零标志位

0表示:结果不为零;1表示:结果为零

C:进位/借位/移出位

0表示:未进位/借位/移出0;1表示:进位/未借位/移出1

V:溢出标志位

0表示:结果未溢出;1表示:结果溢出

2、控制位

I、F中断控制位——控制允许和禁止中断

I=1 禁止IRQ中断 I=0 允许IRQ中断

F=1 禁止FIQ中断 F=0 允许FIQ中断

T控制(标志)位——反映处理器的运行状态

T=1时,程序运行于Thumb状态

T=0时,程序运行于ARM状态

M控制位——决定了处理器的运行模式

当发生异常时这些位被改变。如果处理器运行在特权模式,这些位也可以由程序修改。

1、源码及注释

reset是uboot最先执行的代码,接下来我们来看看reset的具体流程。reset: /*如果没有重新定义save_boot_params,则使用<arch/arm/cpu/armv7/start.S> 中的save_boot_params。其不做任何事情,直接返回。*/ bl save_boot_params /* * disable interrupts (FIQ and IRQ), also set the cpu to SVC32 mode, * except if in HYP mode already */ mrs r0, cpsr /*将cpsr寄存器的内容传送到r0寄存器*/ and r1, r0, #0x1f /*标志位清零*/ teq r1, #0x1a /*测试处理器是否处于HYP模式, HYP是armv-7a为cortex-A15处理器提供硬件虚拟化引进的管理模式。*/ bicne r0, r0, #0x1f /*工作模式位清零*/ orrne r0, r0, #0x13 /*设置成SVC管理模式*/ orr r0, r0, #0xc0 /*关闭FIQ和IRQ中断*/ msr cpsr,r0 /*将r0的值赋给cpsr*/ /* * Setup vector: * (OMAP4 spl TEXT_BASE is not 32 byte aligned. * Continue to use ROM code vector only in OMAP4 spl) */ #if !(defined(CONFIG_OMAP44XX) && defined(CONFIG_SPL_BUILD)) /**************************************************************** 设置异常向量的基地址,正常异常模式下异常向量的基地址为0x00000000,高异常模式下 异常向量的基地址为0xffff0000,这里V=0设置成正常异常模式。CP15协处理器的操作及 相关知识可以看另一篇文章。 *****************************************************************/ /* Set V=0 in CP15 SCTRL register - for VBAR to point to vector */ mrc p15, 0, r0, c1, c0, 0 @ Read CP15 SCTRL Register bic r0, #CR_V @ V = 0 mcr p15, 0, r0, c1, c0, 0 @ Write CP15 SCTRL Register /********************************************* 重新设置异常向量的基地址,只有上面V=0的情况下,这里才能去重新 配置异常向量表的基地址! **********************************************/ /* Set vector address in CP15 VBAR register */ ldr r0, =_start mcr p15, 0, r0, c12, c0, 0 @Set VBAR #endif /* the mask ROM code should have PLL and others stable */ #ifndef CONFIG_SKIP_LOWLEVEL_INIT bl cpu_init_cp15 //初始化协处理器,具体流程请看另一篇文章 bl cpu_init_crit //初始化内存和锁相环,具体流程请看另一篇文章 #endif bl _main //调用c代码,具体流程请看另一篇文章。1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

2、CPSR寄存器介绍

通过向模式位M[4:0]里写入相应的数据切换到不同的模式,在对CPSR,SPSR寄存器进行操作不能使用mov,ldr等通用指令,只能使用特权指令msr和mrs。

在ARM处理器中,只有MRS(Move to Register from State register)指令可以对状态寄存器CPSR和SPSR进行读操作。通过读CPSR可以获得当前处理器的工作状态。读SPSR寄存器可以获得进入异常前的处理器状态(因为只有异常模式下有SPSR寄存器)。

除了用户模式和系统模式,其余模式下都有一个私有SPSR保存状态寄存器,用来保存切换到该模式之前的执行状态,之所以用户模式和系统模式没有SPSR是因为,通常CPU大部分时间执行在用户模式下,当产生异常或系统调用时会分别切换进入另外几种模式,保存用户模式下的状态,当切换回原先模式时,直接回复SPSR的值到CPSR就可以了,因此,用户模式和系统模式下不需要SPSR。

3、相关汇编指令介绍

mrs 将状态寄存器的内容传送至通用寄存器。

teq

TEQ R1,R2 ;将寄存器R1的值与寄存器R2的值按位异或,并根据结果设置CPSR的标志位。该指令通常用于比较操作数1和操作数2是否相等。常与EQ和NE条件码配合使用,当两个数据相等时,条件码EQ有效,否则条件码NE有效。

bic

指令格式:BIC{cond}{S} Rd,Rn,operand2

BIC指令将Rn 的值与操作数operand2 的反码按位逻辑”与”,结果存放到目的寄存器Rd 中。

指令示例:BIC R0,R0,#0x0F ;将R0最低4位清零,其余位不变。

orr

指令格式:orr {cond}{S} Rd,Rn,operand2

orr指令将操作数operand2 与Rn 的值按位逻辑"或",结果存放到目的寄存器Rd 中。

指令示例:orrs R1,R1,R2 ;R1=R1|R2,并根据运算的结果更新标志位。

orr R0,R0,#0x0F ;R0=R0|0x0F,将R0最低4位置1,其余位不变。

4、处理器模式介绍

5、ARM通用寄存器介绍

在ARM处理器内部有37个用户可见的寄存器:30个通用寄存器,6个状态寄存器(1个专用于记录当前状态,5个专用于记录模式切换前的状态),1个程序计数器PC。在不同的工作模式和处理器状态下,程序员可以访问的寄存器也不尽相同。 -31个通用寄存器:

R0~R15;

R13_svc、R14_svc;

R13_abt、R14_abt;

R13_und;R14_und;

R13_irq、R14_irq;

R8_fiq-R14_fiq

-6 个状态寄存器:

CPSR、SPSR_svc、SPSR_abt、SPSR_und、SPSR_irq和SPSR_fiq

5.1 通用寄存器

通用寄存器包括R0~R15,可以分为三类: ─ 未分组寄存器R0~R7

─ 分组寄存器R8~R14

─ 程序计数器PC(R15)

(1)未分组寄存器R0~R7

在所有的运行模式下,未分组寄存器都指向同一个物理寄存器,他们未被系统用作特殊的用途,是真正的通用寄存器。因此,在中断或异常处理进行运行模式转换时,由于不同的处理器运行模式均使用相同的物理寄存器,可能会造成寄存器中数据的破坏,这一点在进行程序设计时应引起注意。

(2)分组的寄存器R8~R14

对于R8~R12,每一次所访问的物理寄存器,与处理器当前的工作模式有关。

一、R8~R12

当处理器工作于fiq模式时,访问的寄存器为R8_fiq~R12_fiq;

除fiq模式以外的其他模式,访问的寄存器为R8_usr~R12_usr。

二、R13和R14:

每个寄存器对应6个不同的物理寄存器,其中的一个是用户模式与系统模式共用,另外5个物理寄存器,对应于其他5种不同的异常模式。

R13:寄存器R13在ARM指令中常用作堆栈指针SP。但这只是一种习惯用法,用户也可使用其他的寄存器作为堆栈指针。而在Thumb指令集中,某些指令强制性的要求使用R13作为堆栈指针。

R14:寄存器R14也称作子程序链接寄存器(Subroutine Link Register)或链接寄存器LR。当执行BL子程序调用指令时,R14中得到R15(程序计数器PC)的备份。其他情况下,R14用作通用寄存器。与之类似,当发生中断或异常时,对应的分组寄存器R14_svc、R14_irq、R14_fiq、R14_abt和R14_und用来保存R15的返回值。

(3)程序计数器PC(R15)

寄存器R15用作程序计数器(PC)。在ARM状态下,位[1:0]为0,位[31:2]用于保存PC;在Thumb状态下,位[0]为0,位[31:1]用于保存PC。

使用R15时注意:虽然R15可以用作通用寄存器,但是有一些指令在使用R15时有一些特殊限制,若不注意,执行的结果将是不可预料的。所以,一般不这么使用。

关于PC的值:由于ARM采用多级流水线技术,所以PC总是指向正在取指的指令,而不是正在执行的指令。也即PC总是指向当前指令的下两条指令的地址。因此,对于ARM指令集而言,PC的值为当前指令的地址值加8个字节。

5.2 状态寄存器

在ARM微处理器中,有CPSR和SPSR两种程序状态寄存器。 1、当前程序状态寄存器 CPSR (Current Program Status Register)用来保存当前程序状态的寄存器。所有处理器模式下都可以访问当前程序状态寄存器CPSR。仅一个CPSR。

2、保存程序状态寄存器SPSR_mode (Saved Program Status Register)SPSR_mode用来进行异常处理,其功能包括:

─ 保存ALU中的当前操作信息,当异常发生时, 用来保存CPSR的值,从异常返回时,将 SPSR_mode复制到CPSR中,恢复CPSR的值。

─ 控制允许和禁止中断 修改SPSR的值

─ 设置处理器的运行模式 修改SPSR的值

问题:一共有多少个SPSR?为什么?

ARM状态寄存器的格式

1、条件码标志位(保存ALU中的当前操作信息)

N:正负号/大小 标志位

0表示:正数/大于;1表示:负数/小于

Z:零标志位

0表示:结果不为零;1表示:结果为零

C:进位/借位/移出位

0表示:未进位/借位/移出0;1表示:进位/未借位/移出1

V:溢出标志位

0表示:结果未溢出;1表示:结果溢出

2、控制位

I、F中断控制位——控制允许和禁止中断

I=1 禁止IRQ中断 I=0 允许IRQ中断

F=1 禁止FIQ中断 F=0 允许FIQ中断

T控制(标志)位——反映处理器的运行状态

T=1时,程序运行于Thumb状态

T=0时,程序运行于ARM状态

M控制位——决定了处理器的运行模式

当发生异常时这些位被改变。如果处理器运行在特权模式,这些位也可以由程序修改。

相关文章推荐

- uboot启动流程详解(2)-reset

- uboot启动流程详解(3)-cpu_init_cp15

- 1.移植uboot-分析uboot启动流程(详解)

- uboot启动流程详解(4)-cpu_init_crit

- uboot启动流程详解(5)-_main

- uboot启动流程详解(3)-cpu_init_cp15

- uboot启动流程详解(1)-_start

- uboot启动流程详解(5)-_main

- uboot启动命令设置详解

- linux系统启动流程详解

- ODL openflowjava和openflowplugin的启动流程,代码详解。

- Linux启动流程详解

- 从0移植uboot (二) _uboot启动流程分析

- uboot启动流程分析之五

- uboot启动流程-s3c2410

- s5pv210 IROM启动流程详解

- CentOS系列启动流程详解

- 详解openstack命令启动实现流程及原理(nova --debug image-list)

- 基于mips架构的uboot 启动流程 (2)

- linux系统启动流程详解