[PCI/PCIe总线] 一、 基础

2018-01-06 11:02

204 查看

处理器系统中的PCI

PCI总线全称Peripheral Component Interconnect,它是处理器系统的一部分,属于局部总线,其主要功能是连接外部设备。PCI总线有独立的地址空间,它与处理器地址空间是隔离的。隔离两者的是一种叫做Host Bus Controller的组件。

下面是一个具有PCI总线的系统的逻辑示意图:

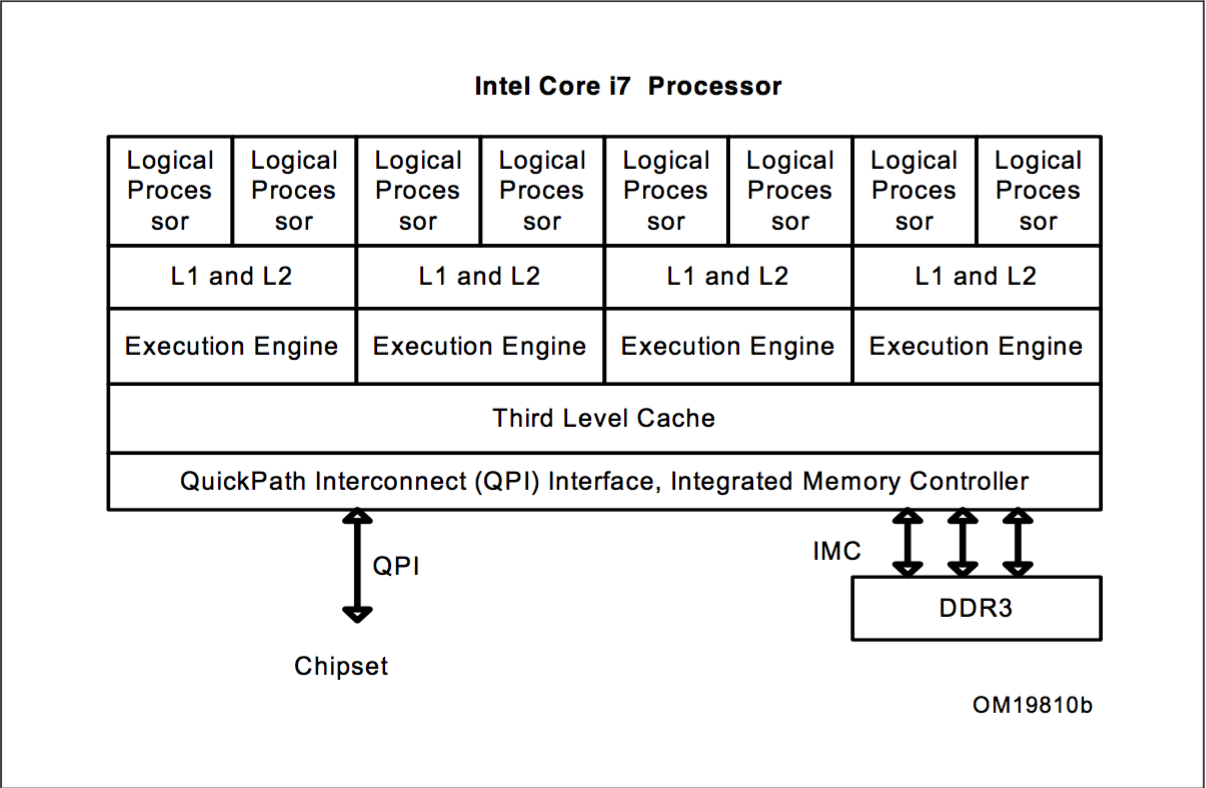

首先是CPU的结构,下面以Intel I7处理器为例:

上图还没有涉及到PCI的部分,PCI部分位于上图的Chipset中。Chipset有南北桥之分,之前北桥是独立的,不过现在一般集成在CPU当中;南桥也不再叫南桥了,而是被称为PCH的部件所代替。另外,对于一些用于嵌入式的系统,连南桥(PCH)也集成在了CPU中。

从上图可以看到多个Host Bus Controller(即上图的HB x)。一个Chipset可以包含多个HB,而每一个HB可以包含一个到多个的PCI Root Bridge:

一个PCI Root Bridge是PCI树结构的根节点,从它往下可以挂不同的设备。PCI Root Bridge下的总线一般称为BUS(0),不过需要注意这里的0并非表示实际的总线地址是0,因为一个Host Bus Controller下可能存在多个PCI Root Bridge,所以实际的地址要根据PCI Root Bridge的个数来分配。例如有两个PCI Root Bridge,而一个Host Bus Controller下总线的最大个数是256个(0x00~0xFF),所以两个PCI Root Bridge下的总线应该是0x00和0x80,即将总线地址分成了两个PCI总线域。

下面是有两个Host Bus Controller的系统:

由于存在两个Host Bus Controllers,因此这个系统支持最多512个PCI总线。

注意,上面的几张图中有个问题,即CPU连接Chipset分别使用了FSB和QPI两种不同的总线,这个不需要特别关注。实际上两种总线都是用来连接CPU和Chipset的,只是QPI更新一点,所以效率更高一点(带宽更大),新的Intel处理器系统一般都使用了QPI而不再使用FSB。

历史

PCI是一种并行总线,在它之前也有一些连接外设的并行总线,如IAS、EISA和MCA等。而在PCI之后,也有PCI-X和PCIe总线,两者都是基于PCI总线设计的。

PCI-X总线仍旧采用并行总线技术,而PCIe使用了高速差分总线来达到更高的频率和更大的带宽,且不同于PCI的共享方式,PCIe总线采用端到端的连接方式,在每一条PCIe链路上只能连接两个设备。

PCI树

前面已经讲到PCI Root Bridge是PCI树的根节点,在它之下是BUS(0)。而在BUS(0)下面可以接两种类型的PCI设备,分别是PCI Bridge和PCI Agent。

其中PCI Bridge用来扩展原来的PCI总线,在PCI Bridge之下可以延伸出新的总线,以此连接更多的设备。

而PCI Agent就是真正的PCI设备(比如网卡)了,是PCI树的最末端。

另外,PCI Bridge还分透明桥和非透明桥,PCI Agent还分主设备和从设备,在这里不多做介绍。

在Linux下,可以通过lspci命令查看PCI树:

原文链接:http://blog.csdn.net/jiangwei0512/article/details/51589276

相关文章推荐

- PCIe总线学习笔记(一、PCI基础知识简介)

- PCIe总线学习笔记(一、PCI基础知识简介)

- 4.1 PCIe总线的基础知识 分类: 浅谈PCI-E 2013-07-22 16:27 975人阅读 评论(1) 收藏

- 7、PCIE总线-PCI、PCIE关系及信号定义

- USB3.0、PCIe、PCI等各总线速度对比与介绍

- PCIe总线的基础知识

- 4.1 PCIe总线的基础知识

- pci-pcie总线序号分配

- 4.1 PCIe总线的基础知识

- 4.1 PCIe总线的基础知识

- USB3.0、PCIe、PCI等各总线速度对比与介绍

- PCI 总线 协议 基础 详解

- 4.1 PCIe总线的基础知识

- 4.1 PCIe总线的基础知识

- PCI/PCIe 的那些事(1)- 总线基本知识

- 7、PCIE总线-PCI、PCIE关系及信号定义

- 设备驱动基础1:设备模型之总线,驱动,设备

- 总线基础--UART

- USB、UART、SPI、I2C、Ethernet、SD、SATA、PCI、 XGMII/XLGMII/CGMII总线的传输速度

- pci总线