STM32学习笔记之时钟分析(硬件设计(535)&keil(476)&Cortex-M3(171)&PCB(334)很有见解)

2017-12-25 02:36

591 查看

STM32学习笔记之时钟分析http://www.cnblogs.com/heiyue/p/7231350.html

本文结合网上的两篇时钟分析文章,并结合本人的理解来分析STM32的时钟系统。

众所周知,一个微控制器或处理器的运行必须要依赖周期性的时钟脉冲来驱动,通常是通过外接晶振来实现的。在学习单片机(51系列,AVR系列,PIC系列)的过程中,只要设定了外接晶振,我们就只关心的时序图,无需再进行时钟的配置,而STM32微控制器的时钟树则是可配置的,其时钟输入源与最终达到外设处的时钟速率不再有固定的关系,本文将来详细解析STM32微控制器的时钟树。

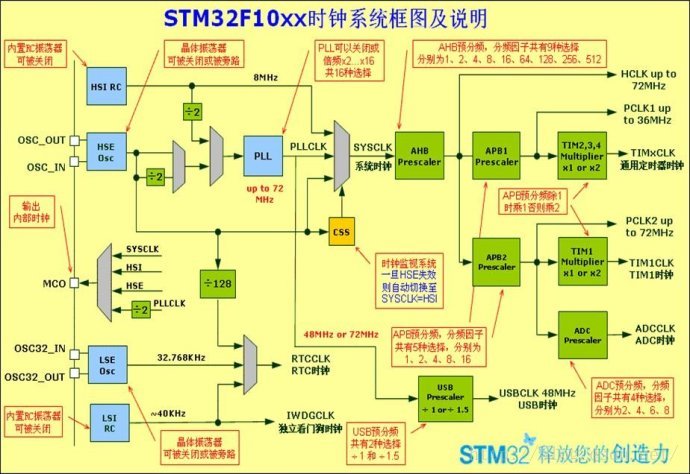

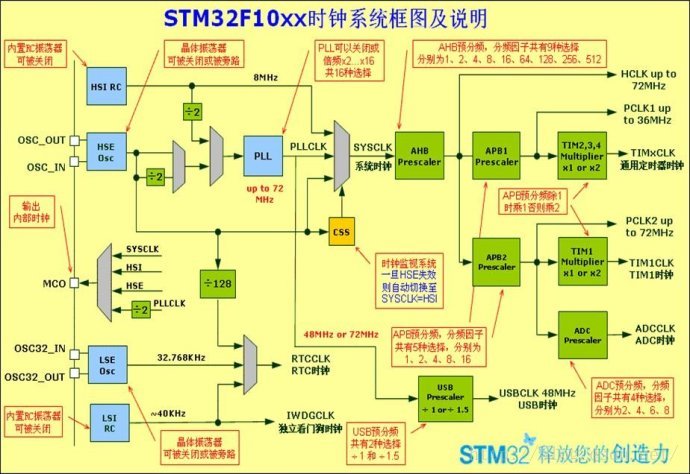

在官方提供的STM32参考手册或数据手册中,提供了如下的时钟树结构图:

为了方便分析,简化为如下的时钟树,

由图可知:STM32主要有5个时钟源,分别为HSI、HSE、LSI、LSE、PLL,如灰蓝色如示,而PLL是由锁相环电路倍频得到PLL时钟。从上到下分析,分别 为:

HSI是高速内部时钟,内置RC振荡器,频率为8MHz;

HSE是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz~16MHz,一般接8MHz石英晶振;

LSE是低速外部时钟,接频率为32.768kHz的石英晶体,主要提供一个精确的时钟源一般作为RTC时钟使用;

LSI是低速内部时钟,RC振荡器,频率为40kHz。它供独立看门狗IWDG使用,另外它还可以被选择为实时时钟RTC的时钟源。另外,实时时钟RTC的时钟源还可以选择LSE,或者是HSE的128分频。RTC的时钟源通过RTCSEL[1:0]来选择;

PLL为锁相环倍频输出,其时钟输入源可选择为HSI/2、HSE或者HSE/2,倍频可选择为2~16倍,但是其输出频率最大不得超过72MHz。

系统时钟SYSCLK,它是供STM32中绝大部分部件工作的时钟源。系统时钟可选择为PLL输出、HSI或者HSE。系统时钟最大频率为72MHz,它通过AHB分频器分频后送给各模块使用,AHB分频器可选择1、2、4、8、16、64、128、256、512分频。其中AHB分频器输出的时钟送给5大模块使用:

送给AHB总线、内核、内存和DMA使用的HCLK时钟;

通过8分频后送给Cortex的系统定时器时钟;

直接送给Cortex的空闲运行时钟FCLK;

送给APB1分频器。APB1分频器可选择1、2、4、8、16分频,其输出一路供APB1外设使用(PCLK1,最大频率36MHz),另一路送给定时器(Timer)2、3、4倍频器使用。该倍频器可选择1或者2倍频,时钟输出供定时器2、3、4使用;

送给APB2分频器。APB2分频器可选择1、2、4、8、16分频,其输出一路供APB2外设使用(PCLK2,最大频率72MHz),另一路送给定时器(Timer)1倍频器使用。该倍频器可选择1或者2倍频,时钟输出供定时器1使用。另外,APB2分频器还有一路输出供ADC分频器使用,分频后送给ADC模块使用。ADC分频器可选择为2、4、6、8分频。

另外:

(1)STM32中有一个全速功能的USB模块,其串行接口引擎需要一个频率为48MHz的时钟源。该时钟源只能从PLL输出端获取,可以选择为1.5分频或者1分频,也就是,当需要使用USB模块时,PLL必须使能,并且时钟频率配置为48MHz或72MHz。

(2)STM32还可以选择一个时钟信号输出到MCO脚(PA8)上,可以选择为PLL输出的2分频、HSI、HSE、或者系统时钟。

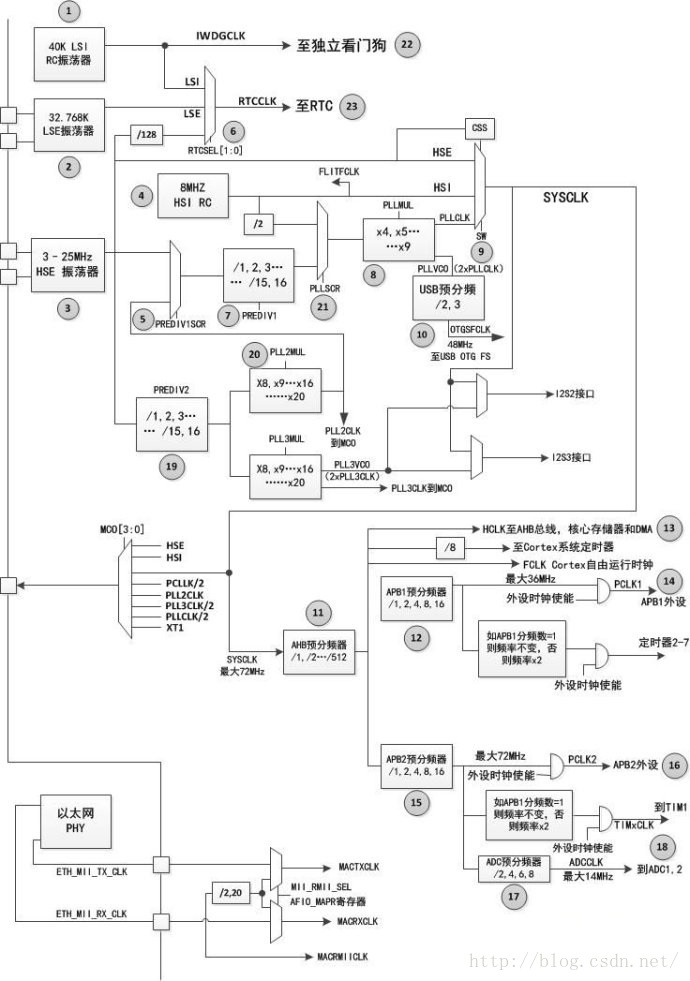

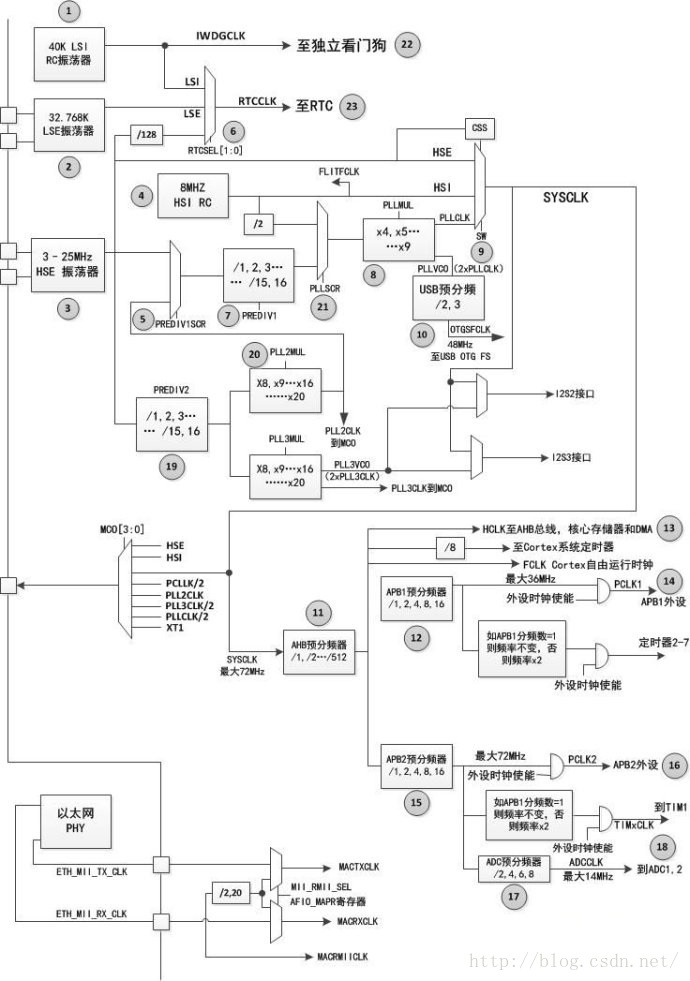

在STM32处理器,对应每一模块,都需要为其配置时钟源,我们将官方提供的时钟树再进行细化,就得到如下的时钟树,其中图中的标号分别为:1:内部低速振荡器(LSI,40Khz);2:外部低速振荡器(LSE,32.768Khz);3:外部高速振荡器(HSE,3-25MHz);4:内部高速振荡器(HSI,8MHz);5:PLL输入选择位;6:RTC时钟选择位;7:PLL1分频数寄存器;8:PLL1倍频寄存器;9:系统时钟选择位;10:USB分频寄存器;11:AHB分频寄存器;12:APB1分频寄存器;13:AHB总线;14:APB1外设总线;15:APB2分频寄存器;16:APB2外设总线;17:ADC预分频寄存器;18:ADC外设;19:PLL2分频数寄存器;20:PLL2倍频寄存器;21:PLL时钟源选择寄存器;22:独立看门狗设备;23:RTC设备

假设我们要设置位于APB2控制的GPIO外设时钟,则我们得到的时钟轨迹应该是:3-->5-->7-->21-->8-->9-->11-->15-->16。即:首先(3)是外部的3-25MHz(前文已假设为8MHz)输入;通过(5)PLL选择位预先选择后续PLL分支的输入时钟(假设选择外部晶振);设置(7)外部晶振的分频数(假设1分频);选择(21)PLL倍频的时钟源(假设选择经过分频后的外部晶振时钟);对于8,设置(8)PLL倍频数(假设9倍频);选择(9)系统时钟源(假设选择经过PLL倍频所输出的时钟);设置(11)AHB总线分频数(假设1分频);设置(15)APB2总线分频数(假设1分频);时钟到达APB2总线(16)。

GPIO设备的最大驱动时钟速率(各个条件已在上述要点中假设):

1) 由3所知晶振输入为8MHz,由5——21知PLL的时钟源为经过分频后的外部晶振时钟,并且此分频数为1分频,因此首先得出PLL的时钟源为:8MHz / 1 = 8MHz。

2) 由8、9知PLL倍频数为9,且将PLL倍频后的时钟输出选择为系统时钟,则得出系统时钟为 8MHz * 9 = 72MHz。

3) 时钟到达AHB预分频器,由11知时钟经过AHB预分频器之后的速率仍为72MHz。

4) 时钟到达APB2预分频器,由15经过APB2预分频器后速率仍为72MHz。

5) 时钟到达APB2总线外设。

因此STM32的APB2总线外设,所能达到的最大速率为72MHz。

接下来从程序的角度分析时钟树的设置,程序清单如下:

即:

(1)定义一个ErrorStatus类型的变量HSEStartUpStatus;

(2)将时钟树复位至默认设置;

(3)开启HSE晶振;

(4)等待HSE晶振起振稳定,并将起振结果保存至HSEStartUpStatus变量中;

(5)判断HSE晶振是否起振成功(假设成功了,进入if内部);

(6)设置HCLK时钟为SYSCLK的1分频;

(7)设置PLCK2时钟为SYSCLK的1分频;

(8)设置PLCK1时钟为SYSCLK的2分频;

(11)选择PLL输入源为HSE时钟经过1分频,并进行9倍频;

(12)使能PLL输出;

(13)等待PLL输出稳定;

(14)选择系统时钟源为PLL输出;

(15)等待系统时钟稳定;

注:(1)PLLCLK表示PLL锁相环的输出时钟,SYSCLK表示系统时钟,HCLK表示AHB总线的时钟,PCLK1表示APB1总线的时钟,PCLK2则表示APB2总线的时钟

(2)以上是ST官方所提供的STM32时钟树配置函数

本文结合网上的两篇时钟分析文章,并结合本人的理解来分析STM32的时钟系统。

众所周知,一个微控制器或处理器的运行必须要依赖周期性的时钟脉冲来驱动,通常是通过外接晶振来实现的。在学习单片机(51系列,AVR系列,PIC系列)的过程中,只要设定了外接晶振,我们就只关心的时序图,无需再进行时钟的配置,而STM32微控制器的时钟树则是可配置的,其时钟输入源与最终达到外设处的时钟速率不再有固定的关系,本文将来详细解析STM32微控制器的时钟树。

在官方提供的STM32参考手册或数据手册中,提供了如下的时钟树结构图:

为了方便分析,简化为如下的时钟树,

由图可知:STM32主要有5个时钟源,分别为HSI、HSE、LSI、LSE、PLL,如灰蓝色如示,而PLL是由锁相环电路倍频得到PLL时钟。从上到下分析,分别 为:

HSI是高速内部时钟,内置RC振荡器,频率为8MHz;

HSE是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz~16MHz,一般接8MHz石英晶振;

LSE是低速外部时钟,接频率为32.768kHz的石英晶体,主要提供一个精确的时钟源一般作为RTC时钟使用;

LSI是低速内部时钟,RC振荡器,频率为40kHz。它供独立看门狗IWDG使用,另外它还可以被选择为实时时钟RTC的时钟源。另外,实时时钟RTC的时钟源还可以选择LSE,或者是HSE的128分频。RTC的时钟源通过RTCSEL[1:0]来选择;

PLL为锁相环倍频输出,其时钟输入源可选择为HSI/2、HSE或者HSE/2,倍频可选择为2~16倍,但是其输出频率最大不得超过72MHz。

系统时钟SYSCLK,它是供STM32中绝大部分部件工作的时钟源。系统时钟可选择为PLL输出、HSI或者HSE。系统时钟最大频率为72MHz,它通过AHB分频器分频后送给各模块使用,AHB分频器可选择1、2、4、8、16、64、128、256、512分频。其中AHB分频器输出的时钟送给5大模块使用:

送给AHB总线、内核、内存和DMA使用的HCLK时钟;

通过8分频后送给Cortex的系统定时器时钟;

直接送给Cortex的空闲运行时钟FCLK;

送给APB1分频器。APB1分频器可选择1、2、4、8、16分频,其输出一路供APB1外设使用(PCLK1,最大频率36MHz),另一路送给定时器(Timer)2、3、4倍频器使用。该倍频器可选择1或者2倍频,时钟输出供定时器2、3、4使用;

送给APB2分频器。APB2分频器可选择1、2、4、8、16分频,其输出一路供APB2外设使用(PCLK2,最大频率72MHz),另一路送给定时器(Timer)1倍频器使用。该倍频器可选择1或者2倍频,时钟输出供定时器1使用。另外,APB2分频器还有一路输出供ADC分频器使用,分频后送给ADC模块使用。ADC分频器可选择为2、4、6、8分频。

另外:

(1)STM32中有一个全速功能的USB模块,其串行接口引擎需要一个频率为48MHz的时钟源。该时钟源只能从PLL输出端获取,可以选择为1.5分频或者1分频,也就是,当需要使用USB模块时,PLL必须使能,并且时钟频率配置为48MHz或72MHz。

(2)STM32还可以选择一个时钟信号输出到MCO脚(PA8)上,可以选择为PLL输出的2分频、HSI、HSE、或者系统时钟。

在STM32处理器,对应每一模块,都需要为其配置时钟源,我们将官方提供的时钟树再进行细化,就得到如下的时钟树,其中图中的标号分别为:1:内部低速振荡器(LSI,40Khz);2:外部低速振荡器(LSE,32.768Khz);3:外部高速振荡器(HSE,3-25MHz);4:内部高速振荡器(HSI,8MHz);5:PLL输入选择位;6:RTC时钟选择位;7:PLL1分频数寄存器;8:PLL1倍频寄存器;9:系统时钟选择位;10:USB分频寄存器;11:AHB分频寄存器;12:APB1分频寄存器;13:AHB总线;14:APB1外设总线;15:APB2分频寄存器;16:APB2外设总线;17:ADC预分频寄存器;18:ADC外设;19:PLL2分频数寄存器;20:PLL2倍频寄存器;21:PLL时钟源选择寄存器;22:独立看门狗设备;23:RTC设备

假设我们要设置位于APB2控制的GPIO外设时钟,则我们得到的时钟轨迹应该是:3-->5-->7-->21-->8-->9-->11-->15-->16。即:首先(3)是外部的3-25MHz(前文已假设为8MHz)输入;通过(5)PLL选择位预先选择后续PLL分支的输入时钟(假设选择外部晶振);设置(7)外部晶振的分频数(假设1分频);选择(21)PLL倍频的时钟源(假设选择经过分频后的外部晶振时钟);对于8,设置(8)PLL倍频数(假设9倍频);选择(9)系统时钟源(假设选择经过PLL倍频所输出的时钟);设置(11)AHB总线分频数(假设1分频);设置(15)APB2总线分频数(假设1分频);时钟到达APB2总线(16)。

GPIO设备的最大驱动时钟速率(各个条件已在上述要点中假设):

1) 由3所知晶振输入为8MHz,由5——21知PLL的时钟源为经过分频后的外部晶振时钟,并且此分频数为1分频,因此首先得出PLL的时钟源为:8MHz / 1 = 8MHz。

2) 由8、9知PLL倍频数为9,且将PLL倍频后的时钟输出选择为系统时钟,则得出系统时钟为 8MHz * 9 = 72MHz。

3) 时钟到达AHB预分频器,由11知时钟经过AHB预分频器之后的速率仍为72MHz。

4) 时钟到达APB2预分频器,由15经过APB2预分频器后速率仍为72MHz。

5) 时钟到达APB2总线外设。

因此STM32的APB2总线外设,所能达到的最大速率为72MHz。

接下来从程序的角度分析时钟树的设置,程序清单如下:

void RCC_Configuration(void)

{

ErrorStatusHSEStartUpStatus; (1)

RCC_DeInit(); (2)

RCC_HSEConfig(RCC_HSE_ON); (3)

HSEStartUpStatus= RCC_WaitForHSEStartUp(); (4)

if(HSEStartUpStatus== SUCCESS) (5)

{

RCC_HCLKConfig(RCC_SYSCLK_Div1); (6)

RCC_PCLK2Config(RCC_HCLK_Div1); (7)

RCC_PCLK1Config(RCC_HCLK_Div2); (8)

FLASH_SetLatency(FLASH_Latency_2); (9)

FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable); (10)

RCC_PLLConfig(RCC_PLLSource_HSE_Div1, RCC_PLLMul_9); (11)

RCC_PLLCmd(ENABLE); (12)

while(RCC_GetFlagStatus(RCC_FLAG_PLLRDY)== RESET); (13)

RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK); (14)

while(RCC_GetSYSCLKSource() != 0x08); (15)

}

} 即:

(1)定义一个ErrorStatus类型的变量HSEStartUpStatus;

(2)将时钟树复位至默认设置;

(3)开启HSE晶振;

(4)等待HSE晶振起振稳定,并将起振结果保存至HSEStartUpStatus变量中;

(5)判断HSE晶振是否起振成功(假设成功了,进入if内部);

(6)设置HCLK时钟为SYSCLK的1分频;

(7)设置PLCK2时钟为SYSCLK的1分频;

(8)设置PLCK1时钟为SYSCLK的2分频;

(11)选择PLL输入源为HSE时钟经过1分频,并进行9倍频;

(12)使能PLL输出;

(13)等待PLL输出稳定;

(14)选择系统时钟源为PLL输出;

(15)等待系统时钟稳定;

注:(1)PLLCLK表示PLL锁相环的输出时钟,SYSCLK表示系统时钟,HCLK表示AHB总线的时钟,PCLK1表示APB1总线的时钟,PCLK2则表示APB2总线的时钟

(2)以上是ST官方所提供的STM32时钟树配置函数

相关文章推荐

- cortex_m3_stm32嵌入式学习笔记(十四):RTC实时时钟(秒中断)

- cortex_m3_stm32嵌入式学习笔记(七):独立看门狗&窗口看门狗

- cortex_m3_stm32嵌入式学习笔记(四):外部中断实验

- cortex_m3_stm32嵌入式学习笔记(二十):IIC实验(I2C串行总线)

- cortex_m3_stm32嵌入式学习笔记(十):输入捕捉实验(定时器的输入捕捉)

- cortex_m3_stm32嵌入式学习笔记(二十四):内存管理实验(动态内存)

- cortex_m3_stm32嵌入式学习笔记(十一):TFTLCD显示(初涉显示器)

- cortex_m3_stm32嵌入式学习笔记(十八):DAC实验(数模转换)

- cortex_m3_stm32嵌入式学习笔记(十九):DMA实验(高速传输)

- cortex_m3_stm32嵌入式学习笔记(一):建立工程模板+跑马灯实验(IO输出)

- STM32学习笔记之时钟分析

- cortex_m3_stm32嵌入式学习笔记(五):独立看门狗实验(IWDG)

- 系统分析与设计学习笔记之一: Introduction of SE & OOAD

- cortex_m3_stm32嵌入式学习笔记(二十二):触摸屏实验(触摸屏驱动)

- cortex_m3_stm32嵌入式学习笔记(九):PWM 输出实验(定时器的PWM输出)

- cortex_m3_stm32嵌入式学习笔记(十二):TFTLCD显示(深入库函数)

- cortex_m3_stm32嵌入式学习笔记(二):独立按键实验(IO输入)

- STM32学习笔记之时钟分析(受启发有汲取之处)

- cortex_m3_stm32嵌入式学习笔记(十七):内部温度传感器(ADC采集)

- cortex_m3_stm32嵌入式学习笔记(三):串口实验(串口通信)