【操作系统】设备管理

2017-12-07 21:07

274 查看

一、前言

学习了存储器管理后,继续学习设备管理,设备管理的主要功能有缓冲区管理、设备分配、设备处理、虚拟设备及实现设备独立性等,由于I/O设备不仅种类繁多,而且他们的特性和操作方式往往相差甚大,使得设备管理称为操作系统中最繁杂且与硬件最紧密的部分,下面开始正式的学习。

二、I/O系统

2.1 I/O设备

I/O设备类型繁多,在OS观点看,设备使用特性、数据传输速率、数据的传输单位、设备共享属性等都是重要的性能指标。可以按照不同角度对他们进行分类

① 按设备的使用特性分类,可把设备分为两类,第一类是存储设备,也称为外存活后备存储器、辅助存储器,是计算机系统用于存储信息的主要设备,该设备速度慢,容量大,价格便宜。第二类是输入/输出设备,可分为输入设备、输出设备和交互式设备,如键盘,鼠标,扫描仪,打印机,显示器等。

② 按传输速率分类,可将I/O设备分为三类,第一类是低速设备,其传输速率仅为每秒钟几个字节至几百个字节的设备,如键盘、鼠标等。第二类是中速设备,其传输速率为每秒数千个字节至十万个字节的设备,如行式打印机、激光打印机等。第三类是高速设备,其传输速率在数百个千字节至千兆字节的设备,如磁带机、磁盘机、光盘机等。

③ 按信息交换的单位分类,可把I/O设备分为两类,第一类为块设备,这类设备用于存储信息,信息以数据块为单位,如磁盘,每个盘块512B~4KB,传输速率较高,通常每秒钟几兆位,另一特征是可寻址,即对它可随机地读/写任一块,磁盘设备的I/O常采用DMA方式。第二类是字符设备,用于数据的输入和输出,其基本单位是字符,属于无结构类型,如打印机等,其传输速率较低,通常为几个字节至数千个字节,另一特征是不可寻址,即输入/出时不能指定数据的输入源地址及输出的目标地址,此外,常采用中断驱动方式。

④ 按设备的共享属性分类,可以分为三类,独占设备,在一段时间内只允许一个用户(进程)访问的设备,即临界资源。共享设备,在一段时间内允许多个进程同时访问的设备,当然,每一时刻仍然只允许一个进程访问,如磁盘(可寻址和可随机访问)。虚拟设备,通过虚拟技术将一台设备变换为若干台逻辑设备,供若干个用户(进程)同时使用。

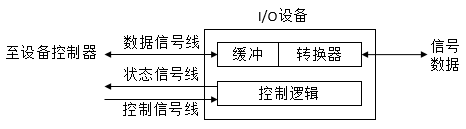

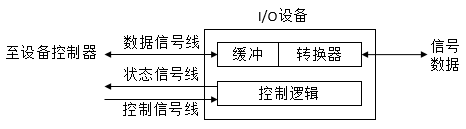

通常,设备并不是直接与CPU进行通信,而是与设备控制器通信,因此,在I/O设备中应该含有与设备控制器之间的接口,在该接口有三种类型的信号,各对应一条信号线。

① 数据信号线,用于在设备控制器之间传送数据信号,对于输入设备而言,由外界输入的信号经转换器转换后所形成的数据,通常先送入缓冲器中,当数量达到一定的比特(字符)数后,再从缓冲器通过一组信号线传送给设备控制器。对输出设备而言,则先将从设备控制器经过数据信号线传送来的一批数据先暂存于缓冲器中,经转换器做适当转换后,再逐个字符地输出。

② 控制信号线,作为由设备控制器向I/O设备发送控制信号时的通路,该信号规定了设备将要执行的操作,如读操作(指由设备向控制器传送数据)或写操作(由控制器接受数据),或执行磁头移动等操作。

③ 状态信号线,用于传送设备当前状态的信号,设备的当前状态有正在读(或写);设备已读(写)完成,并准备好新的数据传送。

2.2 设备控制器

设备控制器是计算机中的一个实体,其主要职责是控制一个或多个I/O设备,以实现I/O设备和计算机之间的数据交换,它是CPU与I/O设备之间的接口,它接收从CPU发来的命令,并去控制I/O设备工作,以使处理从繁杂的设备控制事务中解脱出来。其是一个可编址的设备,当它仅控制一个设备时,它只有一个唯一的设备地址,若控制器可连接多个设备时,则应该含有多个设备地址,并使每个设备地址对应一个设备。设备控制器可以分为用于控制字符设备的控制器和用于控制块设备的控制器。

设备控制器的基本功能如下

① 接收和识别命令,CPU可以向控制器发送多种不同的命令,设备控制器应能够接收并识别这些命令,为此,控制器中应具有相应的控制寄存器,用来存放接收的命令和参数,并对所接收的命令进行译码,相应的,在磁盘控制器中有多个寄存器和命令译码器。

② 数据交换,实现CPU与控制器之间、控制器与设备之间的数据交换,对于前者,通过数据总线,由CPU并行地将数据写入控制器,或从控制器中并行地读出数据,对于后者,是是被将数据输入到控制器,或从控制器传送给设备,为此,在控制器中必须设置一个数据寄存器。

③ 标识和报告设备的状态,控制器应该几下设备的状态供CPU了解,在控制器中设置一状态寄存器,用其中的每一位来反映设备的某一种状态,当CPU将该寄存器的内存读入后,便可了解该设备的状态。

④ 地址识别,系统中的每一个设备都有一个地址,而设备控制器又必须能够识别它所控制的每个设备的地址,此外,为使CPU能向(或从)寄存器中写入(或读出)数据,这些寄存器都应该具有唯一的地址,如硬盘控制器中各寄存器的地址分别为320~32F之一,控制器应该能正确识别这些地址,为此,需要在控制器中配置地址译码器。

⑤ 数据缓冲,由于I/O设备的速率较低而CPU和内存速率很高,故在控制器中必须设置一个缓冲器,在输出时,用此缓冲器暂存由主机高速传来的数据,然后才以I/O设备所具有的速率将缓冲器的数据传送给I/O设备,在输入时,缓冲器则用于暂存从I/O设备送来的数据,待接收一批数据后,再将缓冲器中的数据高速地传送至主机。

⑥ 差错控制,设备控制器监管对I/O设备传送来的数据进行差错检测,若发现传送中出现了错误,则向CPU报告,于是CPU将本次传送的数据作废,并重新传送一次,这样便可以确保数据输入的正确性。

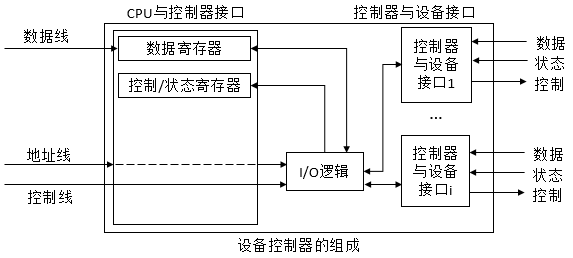

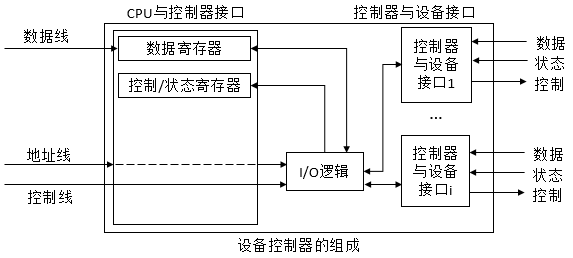

由于设备控制器位于CPU与设备之间,既要与CPU通信,又要与设备通信,还应具有按照CPU所发来的命令去控制设备工作的功能,因此,现有的大多数控制器都是由如下的三部分组成。

① 设备控制器与处理机的接口,该接口用于实现CPU与设备控制器之间的通信,共有三类信号线,数据线、地址线、控制线,数据线与两类寄存器相连接,第一类是数据寄存器,第二类是控制/状态寄存器。

② 设备控制器与设备的接口,设备控制器可以连接一个或多个设备,相应地,在控制器中便有一个或多个设备接口,一个接口连接一台设备,在每个接口中都存在数据、控制和状态三种类型的信号,控制器中的I/O逻辑根据处理机发来的地址信号去选择一个设备接口。

③ I/O逻辑,用于实现对设备的控制,通过一组控制线与处理机交互,处理机利用该逻辑向控制器发送I/O命令,I/O逻辑对收到的命令进行译码,每当CPU要启动一个设备时,一方面将启动命令发送给控制器,另一方面又同时通过地址线把地址发送给控制器,由控制器的I/O逻辑对收到的地址进行译码,再根据所译出的命令对所选设备进行控制。

2.2 I/O通道

虽然在CPU与I/O设备之间增加了设备控制器后,可以大大减少CPU对I/O的干预,但是当主机所配置的外设很多时,CPU的负担仍然很重,因此,在CPU和设备控制器之间又增设了通道。其主要目的是为了建立独立的I/O操作,不仅使数据的传送能独立于CPU,而且也希望有关对I/O操作的组织、管理及其结束处理尽量独立,以保证CPU有更多的时间去进行数据处理。在设置了通道后,CPU只需要向通道发送一条I/O指令,通道在收到该指令后,便从内存中取出本次要执行的通道程序,然后执行该通道程序,仅当通道完成了规定的I/O任务后,才向CPU发中断信号。I/O通道是一种特殊的处理机,具有执行I/O指令的能力,并通过执行通道(I/O)程序来控制I/O操作,但I/O通道与一般的处理机不同,因为其指令类型单一同时没有自己的内存,与CPU共享主内存。

通道用于控制外围设备(包括字符设备和块设备),由于外围设备的类型较多,传输速率相差甚大,因为使通道具有多种类型,根据信息交换方式的不同,将通道分为以下三种。

① 字节多路通道,这是一种按照字节交叉方式工作的通道,通常都含有许多非分配型子通道,其数量可以几十到数百个,每个子通道连接一台I/O设备,并控制该设备的I/O操作,这些子通道按照时间片轮转方式共享主通道。

② 数组选择通道,字节多路通道不适合连接高速设备,数组选择通道按数组进行数据传送,其通常只含有一个分配型子通道,在一段时间内只能执行一道通道程序,控制一台设备进行数据传送,致使当某台设备占用了该通道后,便一直由它独占,即使是它无数据传送,通道被闲置,也不允许其他设备使用该通道,直至该设备传送完毕释放该通道,其利用率很低。

③ 数组多路通道,由于数组选择通道每次只允许一个设备传送数据,数组多路通道是将数组选择通道传输速率高和字节多路通道能使各子通道(设备)分时并行操作的优点相结合而形成的一种新通道,其含有多个非分配型子通道,具有很高的数据传输速率,其数据传输是按数组方式进行的。

由于通道价格昂贵,计算所设置的通道较少,提高通道的利用率的一种很有效的方法是增加设备到主机间的通路而不增加通道。

三、I/O控制方式

* 3.1 程序I/O方式*

在早起计算机系统中,由于无中断机构,处理机对I/O设备的控制采取程序I/O方式,或称为忙-等待方式,即在处理机向控制器发出一条I/O指令启动输入设备输入数据时,要同时把状态寄存器中的忙/闲标志busy设置为1,然后便不断地循环测试busy,只有当其为0时,表示输入已经送入控制器的数据寄存器中,于是处理机将数据寄存器中的数据取出,送入内存指定单元中,这样便完成了一个字(符)的I/O。

在程序I/O方式中,由于CPU的高速性和I/O设备的低速性,致使CPU的绝大部分时间都处于等待I/O设备完成数据I/O的循环测试中,造成对CPU的极大浪费。

3.2 中断驱动I/O控制方式

当某进程要启动某个I/O设备工作时,便由CPU向相应的设备控制器发出一条I/O命令,然后立即返回继续执行原来的任务,设备控制器于是按照该命令的要求去控制指定I/O设备,此时,CPU与I/O设备并行操作。一旦数据进入数据寄存器,控制器便通过控制线向CPU发送一个中断信号,由CPU检查输入过程中是否出错,若无错,便由控制器发送取走数据的信号,再通过控制器及数据线将数据写入内存指定单元中。

在I/O设备输入每个数据的过程中,由于无需CPU干预,因而可使CPU与I/O设备并行工作,仅当完成一个数据输入时,才需CPU花费极短的时间去做一些中断处理。

3.3 直接存储器访问(DMA)I/O控制方式

虽然中断驱动I/O比程序I/O方式更有效,但是,它仍是以字(节)为单位进行I/O的,每当完成一个字(节)的I/O时,控制器便要向CPU请求一次中断,换言之,采用中断驱动I/O方式时的CPU是以字(节)为单位进行干预的,将这种方式用于块设备的I/O是非常低效的,例如,为了从磁盘读取1KB的数据块,需要中断CPU1K次,为了进一步减少CPU对I/O的干预而引入了直接存储器访问方式,该方式的特点如下

① 数据传输的基本单位是数据块,即在CPU与I/O设备之间,每次传送至少一个数据块。

② 所传送的数据是从设备直接送入内存的,或者相反。

③ 仅在传送一个或多个数据块的开始和结束时,需要CPU干预,整块数据的传送是在控制器的控制下完成的。

DMA控制器由三部分组成,主机与DMA控制器的接口;DMA控制器与块设备的接口;I/O控制逻辑。

说明:DMA控制器中的寄存器说明如下

① 命令/状态寄存器(CR),用于接收从CPU发送来的I/O命令,或有关控制信息,或设备的状态。

② 内存地址寄存器(MAR),在输入时,它存放把数据从设备传送到内存的起始目标地址,在输出时,它存放由内存到设备的内存源地址。

③ 数据寄存器(DR),用于暂存从设备到内存,或从内存到设备的数据。

④ 数据计数器(DC),存放本次CPU要读或写的字(节)数。

当CPU要从磁盘读入一个数据块时,便向磁盘控制器发送一条读命令,该命令被送到其中的命令寄存器(CR)中,同时,还需要发送本次要将数据读入的内存起始目标地址,该地址被送入内存地址寄存器(MAR)中,本次要读数据的字(节)数被送入数据寄存器(DC)中,还须将磁盘中的源地址直接送至DMA控制器的I/O控制逻辑上,然后,启动DMA控制器进行数据传送,以后,CPU便可去处理其他任务,此后,整个数据传送过程便由DMA控制器进行控制,当DMA控制器已从磁盘中读入一个字(节)的数据并送入数据寄存器(DR)后,再挪用一个存储器周期,将该字(节)传送到MAR所指示的内存单元中,接着便对MAR内容加1,将DC内存减1,若减后DC内存不为0,表示传送未完成,便继续传送下一个字(节),否则,由DMA控制发出中断请求。

下图展示了三种不同方式的流程。

3.4 I/O通道控制方式

虽然DMA方式比起中断方式已经显著地减少CPU的干预,即已由以字(节)为单位的干预减少到了以数据块为单位进行干预,但CPU没发出一条I/O指令,也只能去读(或写)一个连续的数据块,而当我们需要一次去读多个数据块且将他们分别传送到不同的内存区域,或者相反时,则须由CPU分别发出多条I/O指令及进行多次中断才能完成。I/O通道方式是DMA的发展,它可以进一步减少CPU的干预,即把一个数据块的读(或写)为单位的干预减少为对一组数据块的读(或写)及有关的控制和管理为单位的干预。同时,可以实现CPU、通道、I/O设备的并行操作,提高资源利用率。

通道是通过执行通道程序,并与设备控制器共同实现对I/O设备的控制的,通道程序是由一系列通道指令(或称为通道命令)所构成的,通道指令与一般的机器指令不同,它的每条指令都包含下列的信息。

① 操作码,操作码规定了指令所执行的操作,如读、写、控制等操作。

② 内存地址,内存地址标明字符送入内存(读操作)和从内存取出(写操作)时的内存首址。

③ 计数,该信息表示本条指令所要读(或写)数据的字节数。

④ 通道程序结束位P,该位用于表示通道程序是否结束,P=1表示本条指令是通道程序的最后一条指令。

⑤ 记录结束标志R,R=0表示本通道指令与下一条指令所处理的数据是同属于一个记录,R=1表示这是处理某记录的最后一条指令。

下面给出了一个由六条通道指令所构成的简单通道程序,该程序的功能是将内存中不同地址的数据携程多个记录,其中,前三条指令是分别将813~892单元中的80个字符和1034~1173单元中的140个字符及5830~5889单元的60个字符携程一个记录,第四条指令是单独写一个具有300个字符的记录,第五、六条指令共写含500个字符的记录。

四、缓冲管理

在设备管理中,为了缓和CPU与I/O设备速度不匹配的矛盾,提高CPU与I/O设备的并行性,在I/O设备与处理机交换数据时都用到了缓冲区。

① 缓和CPU和I/O设备间速度不匹配的矛盾。

② 减少对CPU的中断频率,放宽对CPU中断响应时间的限制。

③ 提高CPU和I/O设备之间的并行性。

4.1 单缓冲

每当用户进程发出一个I/O请求时,操作系统便在主存中为之分配一个缓冲区,假定从磁盘把一块数据输入到缓冲区的时间为T,操作系统将该缓冲区中的数据传送到用户区的时间为M,而CPU对这一块数据处理(计算)的时间为C,由于T和C是可以并行的,当T>C时,系统对每一块数据的处理时间为M+T,反之,为M+C,系统对每一块数据的处理时间为Max(C,T) + M。

在字符设备输入时,缓冲区用于暂存用户输入的一行数据,在输入期间,用户进程被挂起以等待数据输入完毕,在输出时,用户进程将一行数据输入到缓冲区后,继续进行处理,当用户进程已有第二行数据输出时,如果第一行数据尚未被提取完毕,则此时用户进程应该阻塞。

4.2 双缓冲

为了加快输入和输出的速度,提高设备利用率,人们又引入了双缓冲区机制,称为缓冲对换,在设备输入时,先将数据送入第一个缓冲区,装满后便转向第二个缓冲区,此时操作系统可以从第一缓冲区中移出数据,并送入用户进程,接着由CPU对数据进行计算,在双缓冲时,系统处理一块数据的时间可以粗略地认为是Max(C,T),如果C

学习了存储器管理后,继续学习设备管理,设备管理的主要功能有缓冲区管理、设备分配、设备处理、虚拟设备及实现设备独立性等,由于I/O设备不仅种类繁多,而且他们的特性和操作方式往往相差甚大,使得设备管理称为操作系统中最繁杂且与硬件最紧密的部分,下面开始正式的学习。

二、I/O系统

2.1 I/O设备

I/O设备类型繁多,在OS观点看,设备使用特性、数据传输速率、数据的传输单位、设备共享属性等都是重要的性能指标。可以按照不同角度对他们进行分类

① 按设备的使用特性分类,可把设备分为两类,第一类是存储设备,也称为外存活后备存储器、辅助存储器,是计算机系统用于存储信息的主要设备,该设备速度慢,容量大,价格便宜。第二类是输入/输出设备,可分为输入设备、输出设备和交互式设备,如键盘,鼠标,扫描仪,打印机,显示器等。

② 按传输速率分类,可将I/O设备分为三类,第一类是低速设备,其传输速率仅为每秒钟几个字节至几百个字节的设备,如键盘、鼠标等。第二类是中速设备,其传输速率为每秒数千个字节至十万个字节的设备,如行式打印机、激光打印机等。第三类是高速设备,其传输速率在数百个千字节至千兆字节的设备,如磁带机、磁盘机、光盘机等。

③ 按信息交换的单位分类,可把I/O设备分为两类,第一类为块设备,这类设备用于存储信息,信息以数据块为单位,如磁盘,每个盘块512B~4KB,传输速率较高,通常每秒钟几兆位,另一特征是可寻址,即对它可随机地读/写任一块,磁盘设备的I/O常采用DMA方式。第二类是字符设备,用于数据的输入和输出,其基本单位是字符,属于无结构类型,如打印机等,其传输速率较低,通常为几个字节至数千个字节,另一特征是不可寻址,即输入/出时不能指定数据的输入源地址及输出的目标地址,此外,常采用中断驱动方式。

④ 按设备的共享属性分类,可以分为三类,独占设备,在一段时间内只允许一个用户(进程)访问的设备,即临界资源。共享设备,在一段时间内允许多个进程同时访问的设备,当然,每一时刻仍然只允许一个进程访问,如磁盘(可寻址和可随机访问)。虚拟设备,通过虚拟技术将一台设备变换为若干台逻辑设备,供若干个用户(进程)同时使用。

通常,设备并不是直接与CPU进行通信,而是与设备控制器通信,因此,在I/O设备中应该含有与设备控制器之间的接口,在该接口有三种类型的信号,各对应一条信号线。

① 数据信号线,用于在设备控制器之间传送数据信号,对于输入设备而言,由外界输入的信号经转换器转换后所形成的数据,通常先送入缓冲器中,当数量达到一定的比特(字符)数后,再从缓冲器通过一组信号线传送给设备控制器。对输出设备而言,则先将从设备控制器经过数据信号线传送来的一批数据先暂存于缓冲器中,经转换器做适当转换后,再逐个字符地输出。

② 控制信号线,作为由设备控制器向I/O设备发送控制信号时的通路,该信号规定了设备将要执行的操作,如读操作(指由设备向控制器传送数据)或写操作(由控制器接受数据),或执行磁头移动等操作。

③ 状态信号线,用于传送设备当前状态的信号,设备的当前状态有正在读(或写);设备已读(写)完成,并准备好新的数据传送。

2.2 设备控制器

设备控制器是计算机中的一个实体,其主要职责是控制一个或多个I/O设备,以实现I/O设备和计算机之间的数据交换,它是CPU与I/O设备之间的接口,它接收从CPU发来的命令,并去控制I/O设备工作,以使处理从繁杂的设备控制事务中解脱出来。其是一个可编址的设备,当它仅控制一个设备时,它只有一个唯一的设备地址,若控制器可连接多个设备时,则应该含有多个设备地址,并使每个设备地址对应一个设备。设备控制器可以分为用于控制字符设备的控制器和用于控制块设备的控制器。

设备控制器的基本功能如下

① 接收和识别命令,CPU可以向控制器发送多种不同的命令,设备控制器应能够接收并识别这些命令,为此,控制器中应具有相应的控制寄存器,用来存放接收的命令和参数,并对所接收的命令进行译码,相应的,在磁盘控制器中有多个寄存器和命令译码器。

② 数据交换,实现CPU与控制器之间、控制器与设备之间的数据交换,对于前者,通过数据总线,由CPU并行地将数据写入控制器,或从控制器中并行地读出数据,对于后者,是是被将数据输入到控制器,或从控制器传送给设备,为此,在控制器中必须设置一个数据寄存器。

③ 标识和报告设备的状态,控制器应该几下设备的状态供CPU了解,在控制器中设置一状态寄存器,用其中的每一位来反映设备的某一种状态,当CPU将该寄存器的内存读入后,便可了解该设备的状态。

④ 地址识别,系统中的每一个设备都有一个地址,而设备控制器又必须能够识别它所控制的每个设备的地址,此外,为使CPU能向(或从)寄存器中写入(或读出)数据,这些寄存器都应该具有唯一的地址,如硬盘控制器中各寄存器的地址分别为320~32F之一,控制器应该能正确识别这些地址,为此,需要在控制器中配置地址译码器。

⑤ 数据缓冲,由于I/O设备的速率较低而CPU和内存速率很高,故在控制器中必须设置一个缓冲器,在输出时,用此缓冲器暂存由主机高速传来的数据,然后才以I/O设备所具有的速率将缓冲器的数据传送给I/O设备,在输入时,缓冲器则用于暂存从I/O设备送来的数据,待接收一批数据后,再将缓冲器中的数据高速地传送至主机。

⑥ 差错控制,设备控制器监管对I/O设备传送来的数据进行差错检测,若发现传送中出现了错误,则向CPU报告,于是CPU将本次传送的数据作废,并重新传送一次,这样便可以确保数据输入的正确性。

由于设备控制器位于CPU与设备之间,既要与CPU通信,又要与设备通信,还应具有按照CPU所发来的命令去控制设备工作的功能,因此,现有的大多数控制器都是由如下的三部分组成。

① 设备控制器与处理机的接口,该接口用于实现CPU与设备控制器之间的通信,共有三类信号线,数据线、地址线、控制线,数据线与两类寄存器相连接,第一类是数据寄存器,第二类是控制/状态寄存器。

② 设备控制器与设备的接口,设备控制器可以连接一个或多个设备,相应地,在控制器中便有一个或多个设备接口,一个接口连接一台设备,在每个接口中都存在数据、控制和状态三种类型的信号,控制器中的I/O逻辑根据处理机发来的地址信号去选择一个设备接口。

③ I/O逻辑,用于实现对设备的控制,通过一组控制线与处理机交互,处理机利用该逻辑向控制器发送I/O命令,I/O逻辑对收到的命令进行译码,每当CPU要启动一个设备时,一方面将启动命令发送给控制器,另一方面又同时通过地址线把地址发送给控制器,由控制器的I/O逻辑对收到的地址进行译码,再根据所译出的命令对所选设备进行控制。

2.2 I/O通道

虽然在CPU与I/O设备之间增加了设备控制器后,可以大大减少CPU对I/O的干预,但是当主机所配置的外设很多时,CPU的负担仍然很重,因此,在CPU和设备控制器之间又增设了通道。其主要目的是为了建立独立的I/O操作,不仅使数据的传送能独立于CPU,而且也希望有关对I/O操作的组织、管理及其结束处理尽量独立,以保证CPU有更多的时间去进行数据处理。在设置了通道后,CPU只需要向通道发送一条I/O指令,通道在收到该指令后,便从内存中取出本次要执行的通道程序,然后执行该通道程序,仅当通道完成了规定的I/O任务后,才向CPU发中断信号。I/O通道是一种特殊的处理机,具有执行I/O指令的能力,并通过执行通道(I/O)程序来控制I/O操作,但I/O通道与一般的处理机不同,因为其指令类型单一同时没有自己的内存,与CPU共享主内存。

通道用于控制外围设备(包括字符设备和块设备),由于外围设备的类型较多,传输速率相差甚大,因为使通道具有多种类型,根据信息交换方式的不同,将通道分为以下三种。

① 字节多路通道,这是一种按照字节交叉方式工作的通道,通常都含有许多非分配型子通道,其数量可以几十到数百个,每个子通道连接一台I/O设备,并控制该设备的I/O操作,这些子通道按照时间片轮转方式共享主通道。

② 数组选择通道,字节多路通道不适合连接高速设备,数组选择通道按数组进行数据传送,其通常只含有一个分配型子通道,在一段时间内只能执行一道通道程序,控制一台设备进行数据传送,致使当某台设备占用了该通道后,便一直由它独占,即使是它无数据传送,通道被闲置,也不允许其他设备使用该通道,直至该设备传送完毕释放该通道,其利用率很低。

③ 数组多路通道,由于数组选择通道每次只允许一个设备传送数据,数组多路通道是将数组选择通道传输速率高和字节多路通道能使各子通道(设备)分时并行操作的优点相结合而形成的一种新通道,其含有多个非分配型子通道,具有很高的数据传输速率,其数据传输是按数组方式进行的。

由于通道价格昂贵,计算所设置的通道较少,提高通道的利用率的一种很有效的方法是增加设备到主机间的通路而不增加通道。

三、I/O控制方式

* 3.1 程序I/O方式*

在早起计算机系统中,由于无中断机构,处理机对I/O设备的控制采取程序I/O方式,或称为忙-等待方式,即在处理机向控制器发出一条I/O指令启动输入设备输入数据时,要同时把状态寄存器中的忙/闲标志busy设置为1,然后便不断地循环测试busy,只有当其为0时,表示输入已经送入控制器的数据寄存器中,于是处理机将数据寄存器中的数据取出,送入内存指定单元中,这样便完成了一个字(符)的I/O。

在程序I/O方式中,由于CPU的高速性和I/O设备的低速性,致使CPU的绝大部分时间都处于等待I/O设备完成数据I/O的循环测试中,造成对CPU的极大浪费。

3.2 中断驱动I/O控制方式

当某进程要启动某个I/O设备工作时,便由CPU向相应的设备控制器发出一条I/O命令,然后立即返回继续执行原来的任务,设备控制器于是按照该命令的要求去控制指定I/O设备,此时,CPU与I/O设备并行操作。一旦数据进入数据寄存器,控制器便通过控制线向CPU发送一个中断信号,由CPU检查输入过程中是否出错,若无错,便由控制器发送取走数据的信号,再通过控制器及数据线将数据写入内存指定单元中。

在I/O设备输入每个数据的过程中,由于无需CPU干预,因而可使CPU与I/O设备并行工作,仅当完成一个数据输入时,才需CPU花费极短的时间去做一些中断处理。

3.3 直接存储器访问(DMA)I/O控制方式

虽然中断驱动I/O比程序I/O方式更有效,但是,它仍是以字(节)为单位进行I/O的,每当完成一个字(节)的I/O时,控制器便要向CPU请求一次中断,换言之,采用中断驱动I/O方式时的CPU是以字(节)为单位进行干预的,将这种方式用于块设备的I/O是非常低效的,例如,为了从磁盘读取1KB的数据块,需要中断CPU1K次,为了进一步减少CPU对I/O的干预而引入了直接存储器访问方式,该方式的特点如下

① 数据传输的基本单位是数据块,即在CPU与I/O设备之间,每次传送至少一个数据块。

② 所传送的数据是从设备直接送入内存的,或者相反。

③ 仅在传送一个或多个数据块的开始和结束时,需要CPU干预,整块数据的传送是在控制器的控制下完成的。

DMA控制器由三部分组成,主机与DMA控制器的接口;DMA控制器与块设备的接口;I/O控制逻辑。

说明:DMA控制器中的寄存器说明如下

① 命令/状态寄存器(CR),用于接收从CPU发送来的I/O命令,或有关控制信息,或设备的状态。

② 内存地址寄存器(MAR),在输入时,它存放把数据从设备传送到内存的起始目标地址,在输出时,它存放由内存到设备的内存源地址。

③ 数据寄存器(DR),用于暂存从设备到内存,或从内存到设备的数据。

④ 数据计数器(DC),存放本次CPU要读或写的字(节)数。

当CPU要从磁盘读入一个数据块时,便向磁盘控制器发送一条读命令,该命令被送到其中的命令寄存器(CR)中,同时,还需要发送本次要将数据读入的内存起始目标地址,该地址被送入内存地址寄存器(MAR)中,本次要读数据的字(节)数被送入数据寄存器(DC)中,还须将磁盘中的源地址直接送至DMA控制器的I/O控制逻辑上,然后,启动DMA控制器进行数据传送,以后,CPU便可去处理其他任务,此后,整个数据传送过程便由DMA控制器进行控制,当DMA控制器已从磁盘中读入一个字(节)的数据并送入数据寄存器(DR)后,再挪用一个存储器周期,将该字(节)传送到MAR所指示的内存单元中,接着便对MAR内容加1,将DC内存减1,若减后DC内存不为0,表示传送未完成,便继续传送下一个字(节),否则,由DMA控制发出中断请求。

下图展示了三种不同方式的流程。

3.4 I/O通道控制方式

虽然DMA方式比起中断方式已经显著地减少CPU的干预,即已由以字(节)为单位的干预减少到了以数据块为单位进行干预,但CPU没发出一条I/O指令,也只能去读(或写)一个连续的数据块,而当我们需要一次去读多个数据块且将他们分别传送到不同的内存区域,或者相反时,则须由CPU分别发出多条I/O指令及进行多次中断才能完成。I/O通道方式是DMA的发展,它可以进一步减少CPU的干预,即把一个数据块的读(或写)为单位的干预减少为对一组数据块的读(或写)及有关的控制和管理为单位的干预。同时,可以实现CPU、通道、I/O设备的并行操作,提高资源利用率。

通道是通过执行通道程序,并与设备控制器共同实现对I/O设备的控制的,通道程序是由一系列通道指令(或称为通道命令)所构成的,通道指令与一般的机器指令不同,它的每条指令都包含下列的信息。

① 操作码,操作码规定了指令所执行的操作,如读、写、控制等操作。

② 内存地址,内存地址标明字符送入内存(读操作)和从内存取出(写操作)时的内存首址。

③ 计数,该信息表示本条指令所要读(或写)数据的字节数。

④ 通道程序结束位P,该位用于表示通道程序是否结束,P=1表示本条指令是通道程序的最后一条指令。

⑤ 记录结束标志R,R=0表示本通道指令与下一条指令所处理的数据是同属于一个记录,R=1表示这是处理某记录的最后一条指令。

下面给出了一个由六条通道指令所构成的简单通道程序,该程序的功能是将内存中不同地址的数据携程多个记录,其中,前三条指令是分别将813~892单元中的80个字符和1034~1173单元中的140个字符及5830~5889单元的60个字符携程一个记录,第四条指令是单独写一个具有300个字符的记录,第五、六条指令共写含500个字符的记录。

四、缓冲管理

在设备管理中,为了缓和CPU与I/O设备速度不匹配的矛盾,提高CPU与I/O设备的并行性,在I/O设备与处理机交换数据时都用到了缓冲区。

① 缓和CPU和I/O设备间速度不匹配的矛盾。

② 减少对CPU的中断频率,放宽对CPU中断响应时间的限制。

③ 提高CPU和I/O设备之间的并行性。

4.1 单缓冲

每当用户进程发出一个I/O请求时,操作系统便在主存中为之分配一个缓冲区,假定从磁盘把一块数据输入到缓冲区的时间为T,操作系统将该缓冲区中的数据传送到用户区的时间为M,而CPU对这一块数据处理(计算)的时间为C,由于T和C是可以并行的,当T>C时,系统对每一块数据的处理时间为M+T,反之,为M+C,系统对每一块数据的处理时间为Max(C,T) + M。

在字符设备输入时,缓冲区用于暂存用户输入的一行数据,在输入期间,用户进程被挂起以等待数据输入完毕,在输出时,用户进程将一行数据输入到缓冲区后,继续进行处理,当用户进程已有第二行数据输出时,如果第一行数据尚未被提取完毕,则此时用户进程应该阻塞。

4.2 双缓冲

为了加快输入和输出的速度,提高设备利用率,人们又引入了双缓冲区机制,称为缓冲对换,在设备输入时,先将数据送入第一个缓冲区,装满后便转向第二个缓冲区,此时操作系统可以从第一缓冲区中移出数据,并送入用户进程,接着由CPU对数据进行计算,在双缓冲时,系统处理一块数据的时间可以粗略地认为是Max(C,T),如果C

相关文章推荐

- 操作系统(十)——设备管理

- 计算机操作系统——设备管理(6)

- 操作系统--设备管理

- 【操作系统】第五章——设备管理

- 操作系统核心原理-7.设备管理:I/O原理

- 操作系统--设备管理

- 计算机操作系统——设备管理(2)

- 操作系统基础知识--设备管理

- 图解操作系统系列-设备管理

- 操作系统 第六章 设备管理

- 【操作系统】设备管理

- 操作系统—设备管理

- 读书笔记-计算机操作系统-设备管理-3

- 操作系统——设备管理

- [STF手机设备管理平台]连接其它操作系统上的安卓设备实操介绍

- 156day(高速缓存,储存设备形成层次结构,操作系统管理硬件)

- 操作系统_再识(linux设备管理文件系统-devfs与udev)

- 操作系统--6设备管理

- 计算机操作系统之设备管理

- 使用netbeans完成的操作系统课程设计-设备管理模拟