Verilog之计数器资源优化

2017-10-27 13:57

627 查看

Verilog之计数器资源优化

采用Verilog编写计数器延时或定时时,会消耗FPGA的片内资源,同时也进而对综合出来的逻辑电路的路径延时产生影响。为此本文探讨以下两种情况对FPGA片内资源的消耗,以及路径延时对系统最大工作频率的影响。其一,计数器实现语句位于同一个always逻辑块中;其二,计数器实现语句采用单独的always逻辑块,与程序其他逻辑块相互独立。(1)计数器实现语句与程序其他逻辑位于同一个always逻辑块

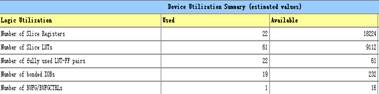

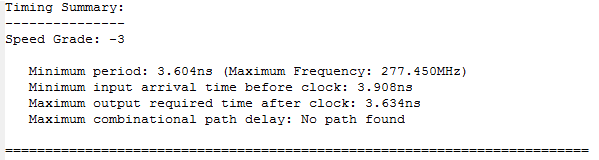

上述代码如下所示,系统最大工作频率约为256.6MHz,消耗61个LUT,22个寄存器。

//------------------------------------------------- Clear: begin if( (!en)&& (cnt1==cnt_ms) ) begin cnt1 <= 0; dout <= 0; state <= Idle; end else begin cnt1 <= cnt1 + 1; state <= Clear; end end //-------------------------------------------------

(2)计数器实现语句与程序其他逻辑位于两个独立的always逻辑块

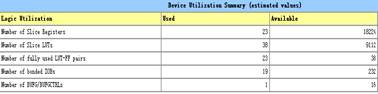

上述代码如下所示,系统最大工作频率约为277.5MHz,消耗38个LUT,23个寄存器。多用的一个寄存器为DelayOver变量。

//------------------------------------------------- Clear: begin if( (!en)&& DelayOver ) begin dout <= 0; state <= Idle; end else begin state <= Clear; end end default: state <= Idle; endcase end always@(posedge clk) if(rst) begin cnt1 <= 0; DelayOver <= 0; end else begin if(cnt1==cnt_ms) begin cnt1 <= 0; DelayOver <= 1; end else begin cnt1 <= cnt1 + 1; DelayOver <= 0; end end //-------------------------------------------------

结论

对比两种情况可知,尤其对于位宽较大的计数器可以进行优化,由独立的always块进行实现,同时可以将一个计数器拆分为两级计数实现,这样可以减小计数器的位宽。

相关文章推荐

- Verilog HDL计数器组合电路(作业2)

- Windows系统资源性能常用计数器

- 转:前端工程与性能优化(下):静态资源管理与模板框架

- 定时/计数器的verilog代码

- 资源受限的数据流处理优化算法的发现之旅

- Verilog RTL 代码设计——译码器&计数器

- Spark性能优化指南(二)(资源调优)

- andrpid优化之删除无用资源

- android 网络加载图片,对图片资源进行优化,并且实现内存双缓存 + 磁盘缓存

- 如何优化FPGA资源例子——我是如何两行代码搞成800行的

- 日志压缩资源消耗优化: Linux CGroup 的使用

- spark性能调优:资源优化

- 【连载】 FPGA Verilog HDL 系列实例--------十进制加减法计数器

- App 优化之查找项目中无用资源

- Cocos2D-X射击小游戏(十一)编码9 图片资源优化以及添加音乐

- 多媒体:图片PNG、IconFont、SVG图标资源优化详解

- Tomcat优化静态资源—— Native APR Connector 配置

- APP瘦身之资源优化篇

- verilog语言定义的“寄存器”是否被优化掉的实验

- 网站优化研究之图像资源网站优化矢量图形下载站优化 之 图形防盗链 以及 缓存图像数据,节省硬盘IO