FPGA综合系统设计(二):基于FPGA的温度采集和以太网传输

2017-06-30 11:53

253 查看

概述

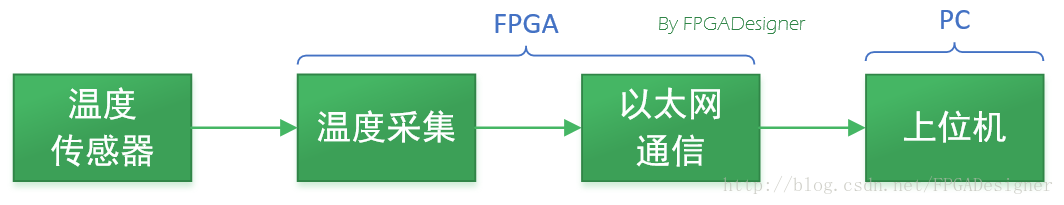

接着上一篇博文的主题,继续讨论FPGA数据采集-传输-显示系统的设计方法。本文以“基于FPGA的温度采集与以太网传输”这个课题为核心展开讨论系统设计的方法,一方面巩固上一篇介绍的设计思想,另一方面会看到一些新产生的问题。系统结构框图如下图所示。

温度传感器如模拟式的PT100,FPGA可以用ADC模块来采集,这种对采集速率要求不高的应用就不需要用上一篇中那样的高速并行ADC,用普通的串行ADC采集即可,这种ADC大多采用的是SPI总线驱动方式。数字式温度传感器如DS18B20、HDC1050,FPGA需要用总线通信的方式来读取温度数据,前者采用的是单总线,后者采用的是IIC通信。

以太网传输目前按速率分有10M、100M和1G(1000M)等,支持哪种速率需要看网卡芯片。以太网传输时可以按UDP或TCP协议来传输数据,前者因为不受控所以不太安全,可能会丢包,但数据传输速度快,只要设计合理也可以避免数据丢失的问题。

本文设计选择使用FPGA通过单总线读取DS18B20的温度数据,通过千兆以太网端口按UDP协议将温度数据发送到网络调试助手中显示。

环境与设备

黑金AX515开发板(Cyclone IV代)和板载Realtek TL8211EG以太网PHY芯片;Quartus II软件;

网络调试助手v3.8。

基于FPGA的温度采集和以太网传输

按照上一篇文章的设计思想,我们可以想到,DS18B20的温度采集速度和以太网发送数据的速度是不一样的,而且差距很大。如果我们在FPGA设计时直接将DS18B20的温度数据接口与以太网模块的接口相连接,上位机上我们会接收到大量的“老数据”,也就是采集一次温度数据而被发送了多次。避免这个问题的方法就是在两个模块之间加一级存储器,上次我们用了FIFO,这次体验一下双口RAM。双口RAM比起FIFO的优势是可以在读出端口随意的读取RAM中存储的任意一个数据,而FIFO只能按顺序读出,两者在不同的地方有不同的应用。因此FPGA程序的模块划分设计如下。

单总线通信可以用有限状态机的方式实现,读出温度数据按符号位、十位、个位、小数点位拆分开,这里不得提一下,DS18B20的精度虽然不高,但是分辨率很高,小数点可以推到后面很多位,但是使用时完全不需要这么高的分辨率,根据需求提取数据即可。

以太网在传输过程中需要按ASIIC码来传输,这样传到上位机中的数字和字符就可以直接显示出来。因此在把温度数据写入RAM的时候转换为ASIIC码后再写入。

按照上述方法完成FPGA的设计,在UDP模块中指定好要传入的网卡MAC地址和IP地址,在PC上把IP地址做出对应的修改。经过测试确发现接收到的数据全是0,这让博主百思不得其解,一开始一位是总线程序设计出错,导致读取不到正确的数据,后来无意间的按了一下复位键,确发现接收到了正确的温度数据,只是温度数据是一个固定值,不会随环境改变。而重新下载后才会收到新的温度数据。

思考一下就会发现,该问题很明显是由于双口RAM的状态设计上出错造成的。可以收到温度数据表示总线模块和UDP模块应该是都没有问题,而UDP模块是从RAM中读取的数据,很显然UDP读取的是固定的一个温度值,也就是表明RAM中存储的数据没有被刷新。再简单点讲,在总线通信还没有完成的时候,RAM中就已经被写入了0,而总线通信完成后,新的温度数据没有写到RAM中,UDP模块读到的就一直是0。

找到了问题便有了解决思路,重新检查下RAM的设计状态,在RAM读满后将地址移向RAM的开头位置,让温度数据覆盖最早的旧数据,保持数据的不断更新。修改后再进行测试结果正确,效果如下图所示。

总结

其实在1.2/50μs脉冲电压采集的设计中也有类似的问题,就是在FIFO为满时该怎么操作,FIFO为空时该做出什么反应?如果上一节的实验在FIFO满时不刷新FIFO中的数据同样会有本文遇到的问题。而FIFO为空时就应该禁止数据的传输,以避免传输错误的数据。本文可以提供完整的QuartusII源工程,因为把一些代码的零碎片段放在文中也没有太大意义,如果您需要该工程,请发送邮件至godwar_liuqi@outlook.com中索取。

如果您发现本文中有错别字、言语混论、逻辑不通或难以理解的地方,请评论留言,谢谢!

相关文章推荐

- 基于VB的单片机温度数据采集与传输系统设计

- 基于VB的单片机温度数据采集与传输系统设计 下位机程序

- FPGA设计——CMOS图像采集与以太网传输显示(OV7670)

- 【科研论文】基于FPGA和W5100的以太网通信系统设计

- 【科研论文】基于W5300的以太网数据传输系统的设计与实现

- 基于PSoC的飞艇智能无线温度采集系统设计

- 基于W5300和FPGA的实时数据采集系统设计

- 基于stm32的无线多点温度采集系统设计

- 基于ZigBee 的多点温度采集系统设计与实现

- 基于FPGA和W5100的以太网通信系统设计

- 基于RBAC扩展模型的实验室综合管理系统设计与实现

- 基于usb的数据采集系统设计 学习笔记一

- Zigbee之旅(十):综合小实验——基于CC2430的温度监测系统(转)

- 基于FPGA的以太网MII接口扩展设计与实现

- 基于TMS320DM355的VGA视频采集系统的设计与实现

- 基于NIOS II处理器的面阵CCD采集系统设计

- 【转】基于verilog HDL 的FPGA设计中可综合的问题

- 基于蓝牙的数据传输系统的设计

- 基于TCP/IP协议的电力通信综合监控管理系统设计与实现

- 基于FPGA的以太网MII接口扩展设计与实现