嵌入式Linux裸机开发(六)——S5PV210时钟系统

2017-03-26 12:41

330 查看

嵌入式Linux裸机开发(六)——S5PV210时钟系统

一、时钟系统简介

外设工作需要一定频率的时钟,这些时钟都由系统时钟提供。系统时钟一般由外部低频24MHZ晶体振荡器通过锁相环电路PLL倍频产生。通过外部的低频晶体振荡器产生系统时钟不仅可以减少干扰还可以降低成本。外设的工作频率越高,功耗越高,越不稳定。通过关闭外设的时钟可以关闭外设。二、时钟域

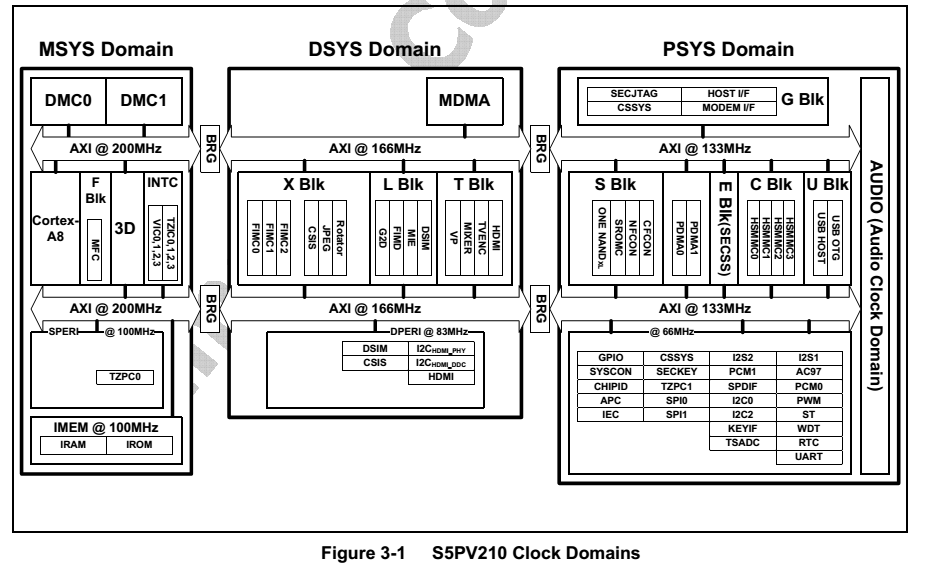

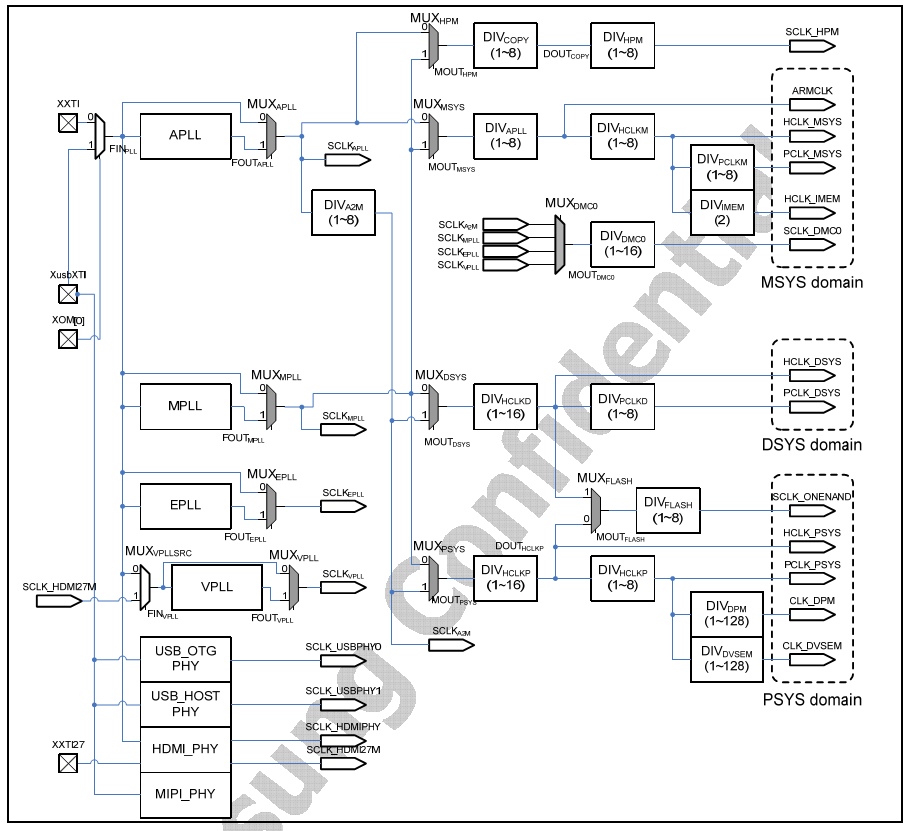

S5PV210 中包含 3 大类时钟 domain, 分别是主系统时钟 domain (简称 MSYS)、显示相关的时钟 domain (DSYS)、 外围设备的时钟 domain (PSYS)。 1、MSYS: 用来给 cortex a8 处理器, dram 控制器, 3D, IRAM, IROM,中断控制器等提供时钟,cortex a8只支持同步模式,因此必须用200MHZ的AXI总线提供同步。2、DSYS: 用来给显示相关的部件提供时钟,包括 FIMC, FIMD, JPEG, and multimedia IPs 3、PSYS:用来给外围设备提供时钟,如 i2s, spi,i2c,uart 等4、每一种总线系统分别提供200MHZ、166MHZ、133MHZ时钟,两个不同时钟域通过异步总线桥(BRG)连接。S5PV210时钟域图如下:

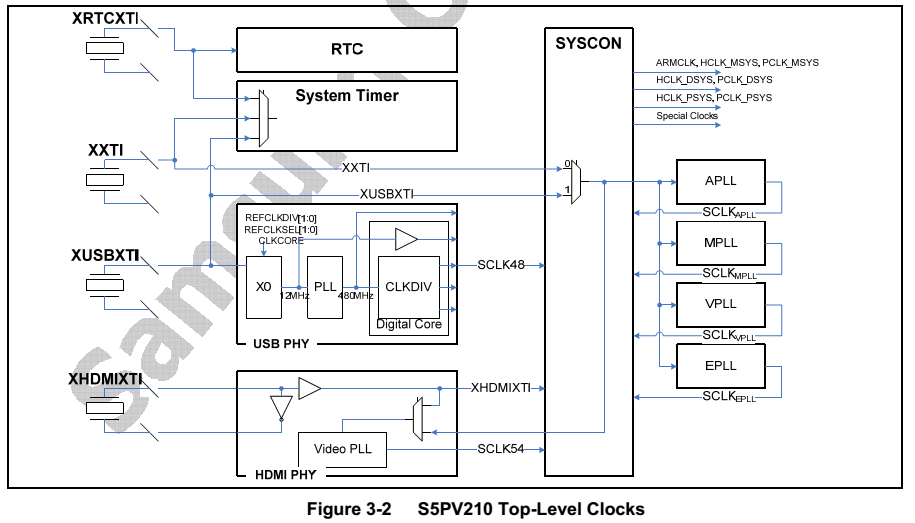

S5PV210原始时钟来源:

S5PV210有四个外部晶体振荡器接口,开发板设计时可以选择外接什么晶体振荡器。

原始时钟产生如下图:

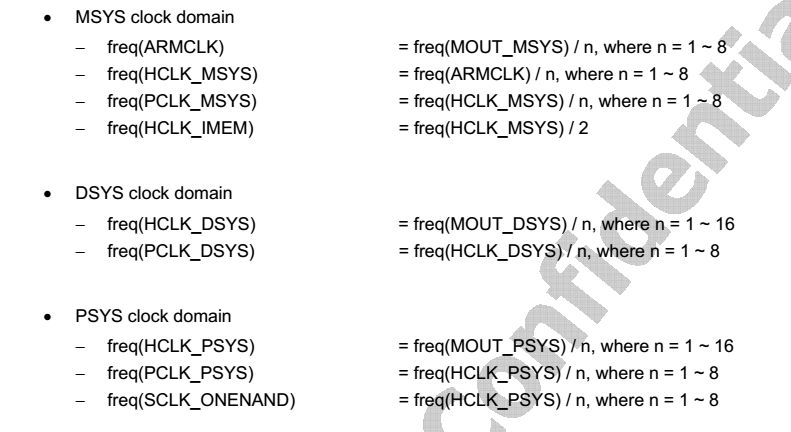

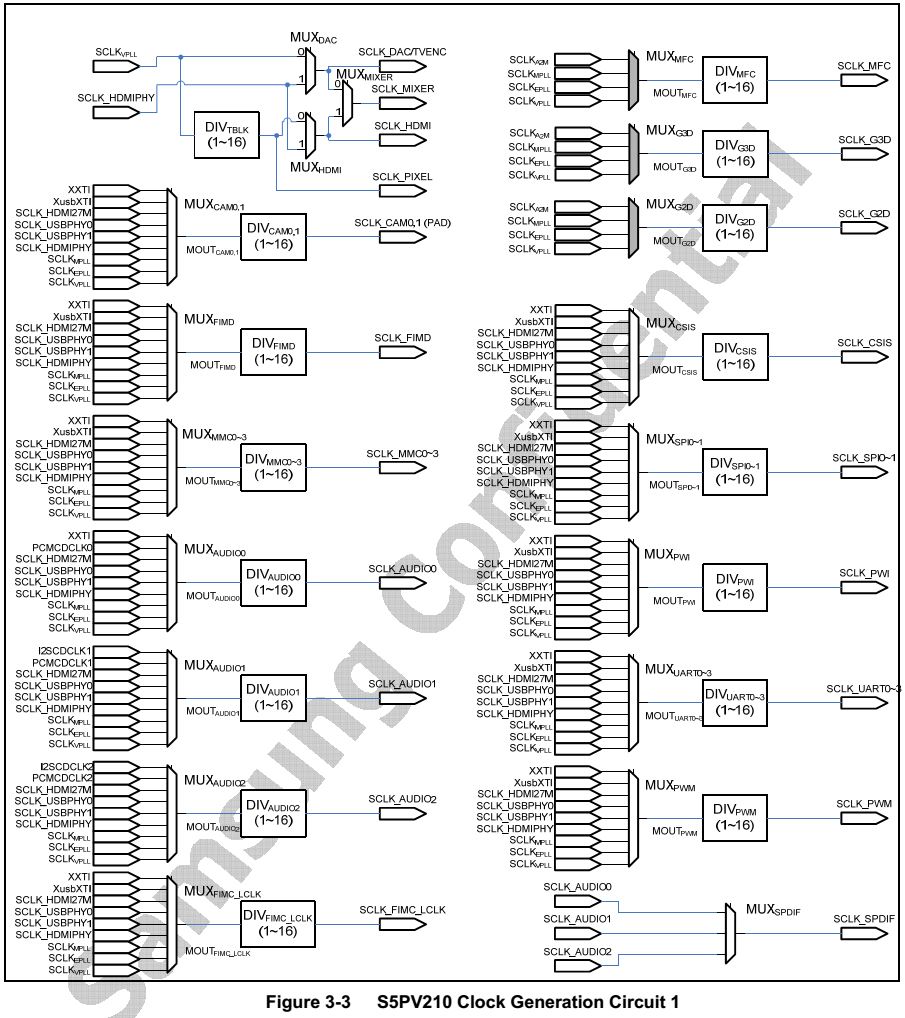

Smart210外接的晶振频率(简称 Fin)为 24MHz,通过锁相环电路PLL倍频提高系统时钟频率。 S5PV210 共有 4 个倍频器,即 PLL, 包括 APLL(供 MSYS 使用),MPLL(供 DSYS 使用),EPLL(供 PSYS 使用),VPLL(供 video 相关的时钟使用)。 3 大类时钟 domain中,可以使用不同的分频,使其给不同部件输出所需要的时钟,各类时钟的关系如下图:

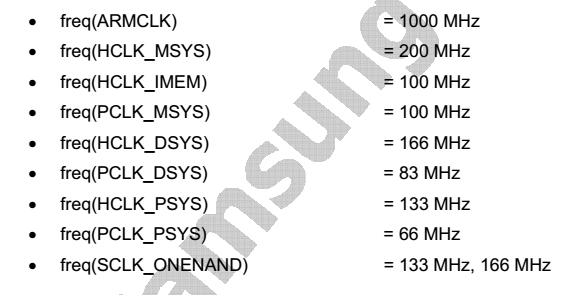

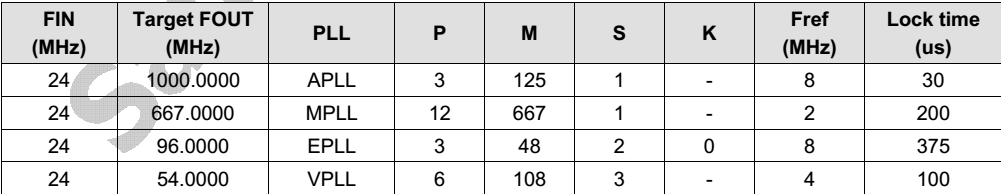

三星S5PV210推荐的时钟设置参考值如下:

时钟产生原理图:

三、时钟控制寄存器

XPLL_LOCK:控制PLL锁定周期XPLL_CON:打开、关闭PLL电路,设置倍频参数

CLK_SRCX:设置时钟源

CLK_SRC_MASX:时钟源选择通道设置,默认打开

CLK_DIVX:分频器参数设置

CLK_GATE_XXX:时钟控制

CLK_DIV_STATX:查看分频器状态

CLK_MUX_STATX:查看mux状态

四、时钟设置

时钟设置流程:1、设置各种时钟开关,暂时关闭PLL2、设置APLL/MPLL/EPLL/EPLL锁相环时间

三星推荐0x00000FFF,设置最大值0x0000FFFF

3、设置PLL倍频参数

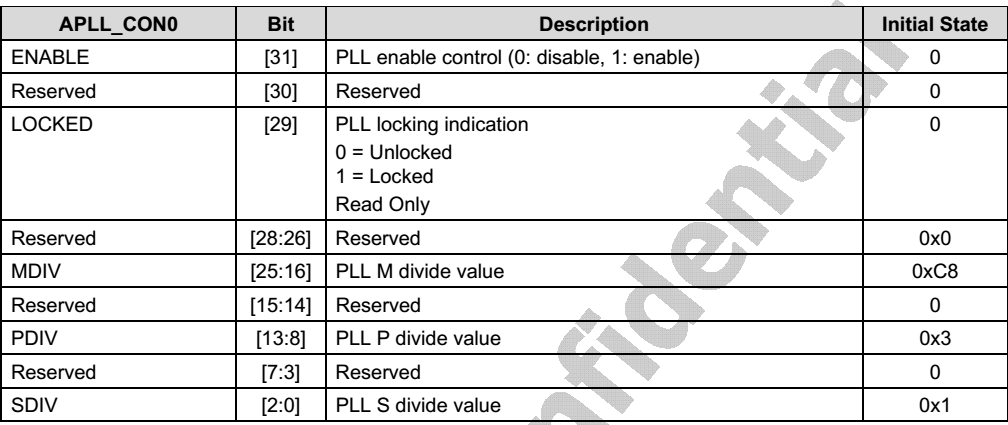

设置APLL_CON寄存器设置如下:

FOUT = MDIV X FIN / (PDIV × 2^(SDIV-1))

MPLL、EPLL、VPLL类似

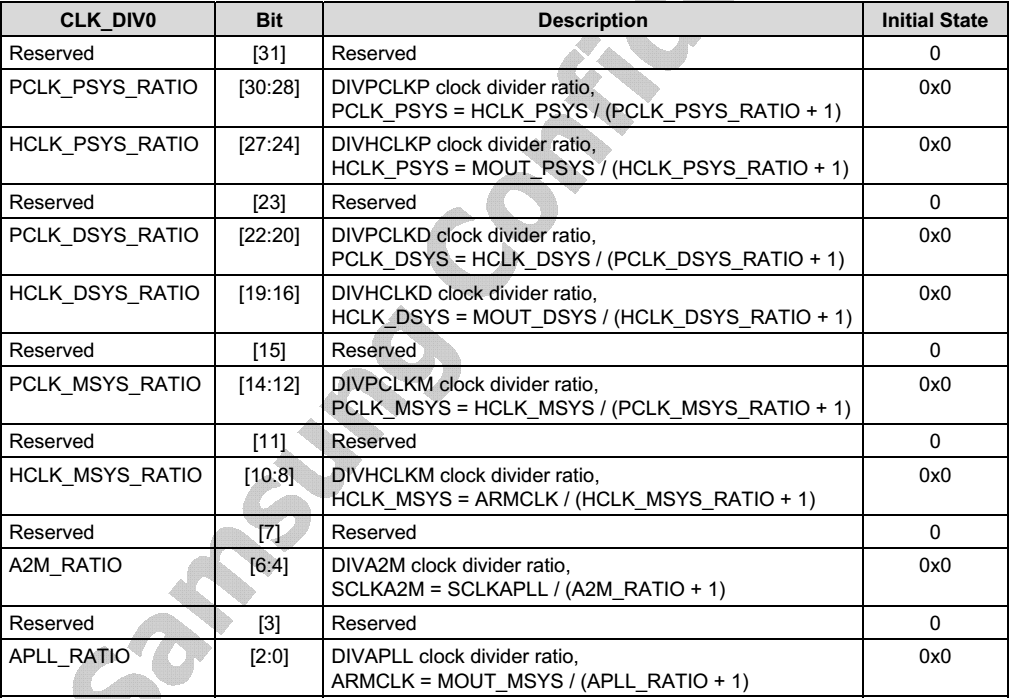

4、设置分频参数设置CLK_DIV0寄存器

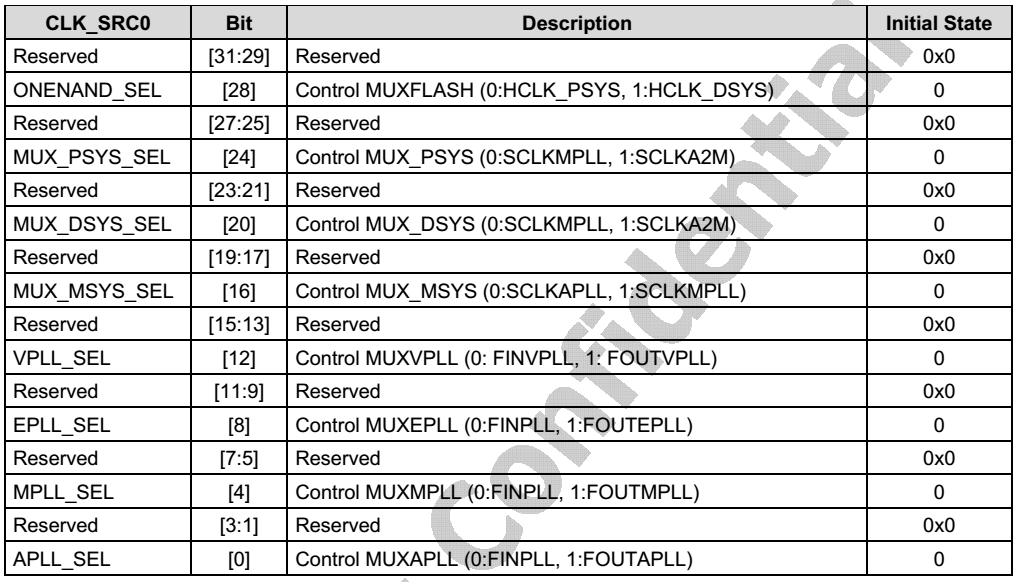

5、选择各种时钟源,打开PLL结合时钟产生的原理图,设置CLK_SRC0寄存器

clock_init源码:

// 时钟控制器基地址

#define ELFIN_CLOCK_POWER_BASE 0xE0100000

// 时钟相关的寄存器相对时钟控制器基地址的偏移值

#define APLL_LOCK_OFFSET 0x00

#define MPLL_LOCK_OFFSET 0x08

#define APLL_CON0_OFFSET 0x100

#define APLL_CON1_OFFSET 0x104

#define MPLL_CON_OFFSET 0x108

#define CLK_SRC0_OFFSET 0x200

#define CLK_SRC1_OFFSET 0x204

#define CLK_SRC2_OFFSET 0x208

#define CLK_SRC3_OFFSET 0x20c

#define CLK_SRC4_OFFSET 0x210

#define CLK_SRC5_OFFSET 0x214

#define CLK_SRC6_OFFSET 0x218

#define CLK_SRC_MASK0_OFFSET 0x280

#define CLK_SRC_MASK1_OFFSET 0x284

#define CLK_DIV0_OFFSET 0x300

#define CLK_DIV1_OFFSET 0x304

#define CLK_DIV2_OFFSET 0x308

#define CLK_DIV3_OFFSET 0x30c

#define CLK_DIV4_OFFSET 0x310

#define CLK_DIV5_OFFSET 0x314

#define CLK_DIV6_OFFSET 0x318

#define CLK_DIV7_OFFSET 0x31c

#define CLK_DIV0_MASK 0x7fffffff

#define APLL_MDIV 0x7d

#define APLL_PDIV 0x3

#define APLL_SDIV 0x1

#define MPLL_MDIV 0x29b

#define MPLL_PDIV 0xc

#define MPLL_SDIV 0x1

#define set_pll(mdiv, pdiv, sdiv) (1<<31 | mdiv<<16 | pdiv<<8 | sdiv)

#define APLL_VAL set_pll(APLL_MDIV,APLL_PDIV,APLL_SDIV)

#define MPLL_VAL set_pll(MPLL_MDIV,MPLL_PDIV,MPLL_SDIV)

.global clock_init

clock_init:

ldr r0, =ELFIN_CLOCK_POWER_BASE

// 1 设置各种时钟开关,暂时不使用PLL

ldr r1, =0x0

// 芯片手册P378 寄存器CLK_SRC:Select clock source 0 (Main)

str r1, [r0, #CLK_SRC0_OFFSET]

// 2 设置锁定时间,使用默认值即可

// 设置PLL后,时钟从Fin提升到目标频率时,需要一定的时间,即锁定时间

ldr r1,=0x0000FFFF

str r1,[r0, #APLL_LOCK_OFFSET]

str r1, [r0, #MPLL_LOCK_OFFSET]

// 3 设置PLL

// FOUT = MDIV*FIN/(PDIV*2^(SDIV-1))=0x7d*24/(0x3*2^(1-1))=1000 MHz

ldr r1, =APLL_VAL

str r1, [r0, #APLL_CON0_OFFSET]

// FOUT = MDIV*FIN/(PDIV*2^SDIV)=0x29b*24/(0xc*2^1)= 667 MHz

ldr r1, =MPLL_VAL

str r1, [r0, #MPLL_CON_OFFSET]

// 4 设置分频

// 清bit[0~31]

ldr r1, [r0, #CLK_DIV0_OFFSET]

ldr r2, =CLK_DIV0_MASK

bic r1, r1, r2

ldr r2, =0x14131440//对照CLK_DIV0寄存器分析

orr r1, r1, r2

str r1, [r0, #CLK_DIV0_OFFSET]

// 5 设置各种时钟开关,使用PLL

ldr r1, [r0, #CLK_SRC0_OFFSET]

ldr r2, =0x10001111

orr r1, r1, r2

str r1, [r0, #CLK_SRC0_OFFSET]

mov pc, lr

本文出自 “生命不息,奋斗不止” 博客,请务必保留此出处http://9291927.blog.51cto.com/9281927/1786916

相关文章推荐

- 【裸机开发笔记】6410的系统时钟设置(上)---6410时钟控制逻辑框架分析

- 嵌入式Linux裸机开发(二)——S5PV210启动过程分析

- 嵌入式Linux裸机开发(二)——S5PV210启动过程分析

- 【裸机开发笔记】6410的系统时钟设置(上)---6410时钟控制逻辑框架分

- 【裸机开发笔记】6410的系统时钟设置(下)---几个常用函数的C源码。

- 【裸机开发笔记】6410的系统时钟设置(中)---相关寄存器介绍

- 【裸机开发笔记】6410的系统时钟设置(下)---几个常用函数的C源码。

- 嵌入式Linux裸机开发(六)——S5PV210时钟系统

- 嵌入式Linux裸机开发(九)——S5PV210定时器

- 嵌入式Linux裸机开发(八)——S5PV210中断处理流程

- 《嵌入式linux应用程序开发完全手册》系统时钟和定时器学习笔记

- 八.ARM裸机学习之S5PV210的时钟系统1(原理概念及框图分析)

- 【裸机开发笔记】6410的系统时钟设置(中)---相关寄存器介绍

- S5PV210 系列(裸机八)之 时钟系统

- 嵌入式linux系统开发概述之一----Bootloader

- 嵌入式linux开发 x6818挂载nfs文件系统

- 按照S5PV210的官方手册使用C语言配置系统时钟--实例分析

- Exynos4412裸机开发 —— RTC 实时时钟单元

- 嵌入式Linux系统软件开发

- S5PV210的时钟系统简介