Verilog中同步复位,异步复位,异步复位同步释放

2017-03-09 12:59

357 查看

简介

在实际的工程中选择复位策略之前必须考虑许多设计方面的问题,如使用同步复位或者异步复位或者异步复位同步释放(Asynchronous Reset Synchronous Release或者Synchronized Asynchronous Reset),以及是否每一个触发器都需要进行复位。复位的基本目的是使器件进入到可以稳定工作的确定状态,这避免了器件在上电后进入到随机状态导致跑飞了。在实际设计过程中,设计者必须选择最适合于设计本身的复位方式。

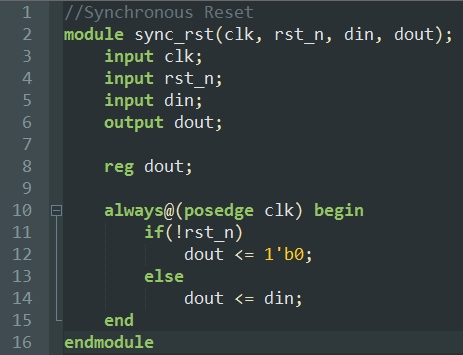

同步复位

同步复位就是指复位信号只有在时钟上升沿到来时,才能有效。同步复位RTL代码:

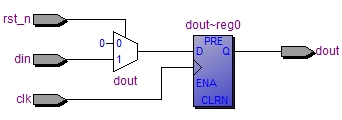

综合后的RTL图如下:

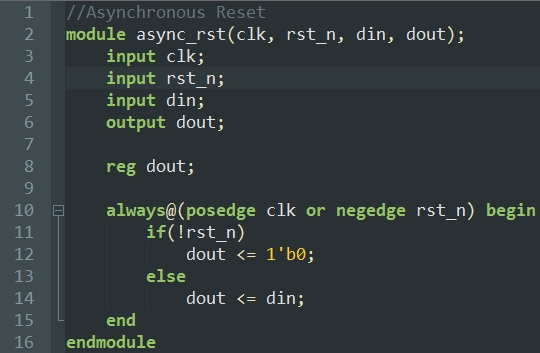

异步复位

异步复位是指无论时钟沿是否到来,只要复位信号有效,就对系统进行复位。异步复位RTL代码:

综合后的RTL图如下:

同步复位与异步复位的优缺点

同步复位的优点:

一般能够确保电路是百分之百同步的。

确保复位只发生在有效时钟沿,可以作为过滤掉毛刺的手段。

同步复位的缺点:

复位信号的有效时长必须大于时钟周期,才能真正被系统识别并完成复位。同时还要考虑如:时钟偏移、组合逻辑路径延时、复位延时等因素。

由于大多数的厂商目标库内的触发器都只有异步复位端口,采用同步复位的话,就会耗费较多的逻辑资源。

异步复位优点:

异步复位信号识别方便,而且可以很方便的使用全局复位。

由于大多数的厂商目标库内的触发器都有异步复位端口,可以节约逻辑资源。

异步复位缺点:

复位信号容易受到毛刺的影响。

复位结束时刻恰在亚稳态窗口内时,无法决定现在的复位状态是1还是0,会导致亚稳态。

异步复位同步释放

使用异步复位同步释放就可以消除上述缺点。所谓异步复位,同步释放就是在复位信号到来的时候不受时钟信号的同步,而是在复位信号释放的时候受到时钟信号的同步。异步复位同步释放的原理图和代码如下:

相关文章推荐

- [转]同步复位,异步复位以及异步复位同步释放

- FPGA同步复位,异步复位以及异步复位同步释放实例分析

- FPGA同步复位,异步复位以及异步复位同步释放实例分析

- Verilog中异步复位,同步释放

- 三种复位方式: 同步复位、异步复位、异步复位同步释放

- FPGA:同步复位,异步复位以及异步复位同步释放

- 同步复位,异步复位以及异步复位同步释放(转载)

- 同步复位与异步复位——异步复位同步释放

- 【Verilog】 同步复位和异步复位比较 async vs. sync

- 异步复位、同步释放

- 异步复位同步释放---关于复位的问题

- 老生常谈-----异步复位 同步释放

- FPGA基础之异步复位和同步释放电路的详细解释

- 如何复位———异步复位,同步释放的方式,而且复位信号低电平有效(转)

- 同步复位与异步复位-异步复位和同步复位区别.

- 经典设计整理之二——————异步复位,同步释放

- FPGA基础之异步复位和同步释放电路的详细解释

- 为什么要异步复位,同步释放

- FPGA基础-异步复位,同步释放

- 异步复位同步释放