关于 FPGA设计, 时序报告的重要性。

2016-10-20 09:27

197 查看

经常看到文档上讲, 一定要把时序报告 跑过去,才可以出货。一直不以为然。

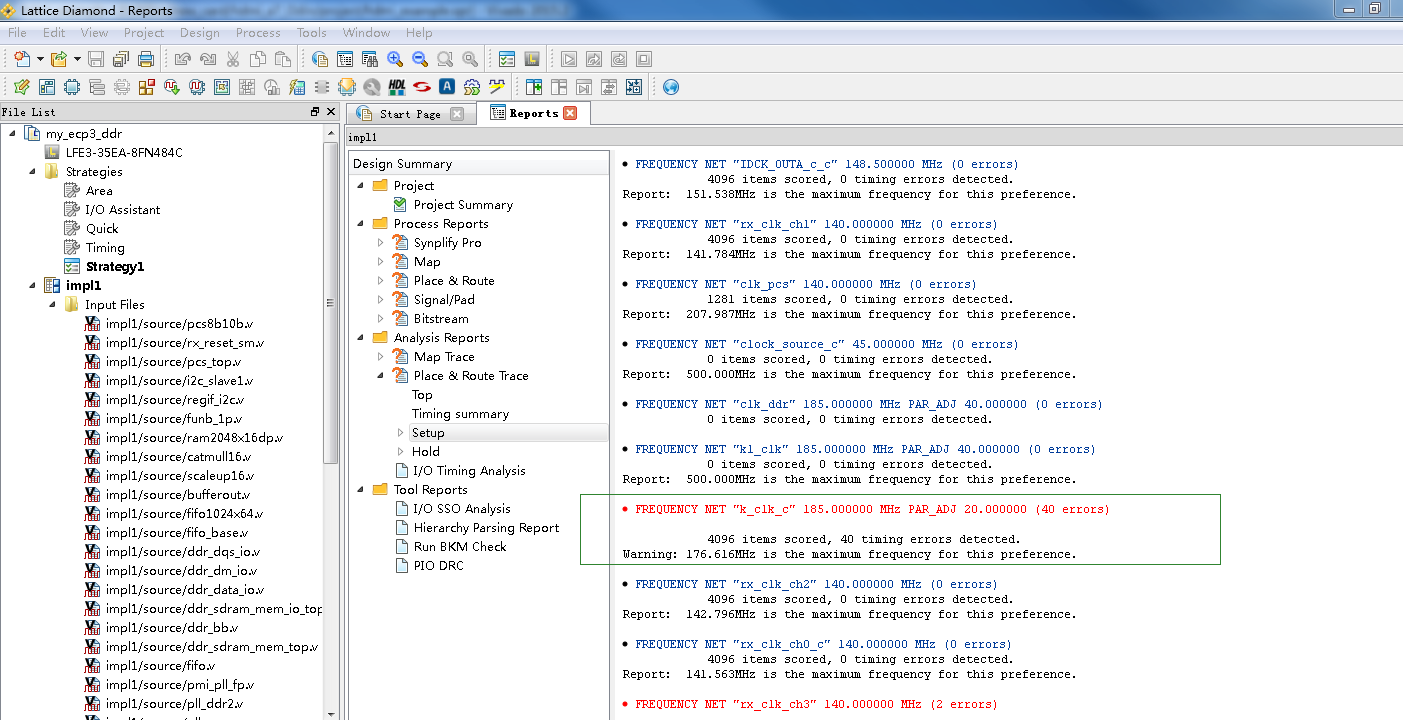

项目上用的 lattice 的 ecp3-35,esmt的ddr. 之前 用 了一年多,一直没有没有问题。 最近新贴的一批板子, 在运行10天左右,经常会出现DDR读写错误。现象如下:

一开始怀疑是 DDR的问题,然后就想作手改板。换成DDR3.

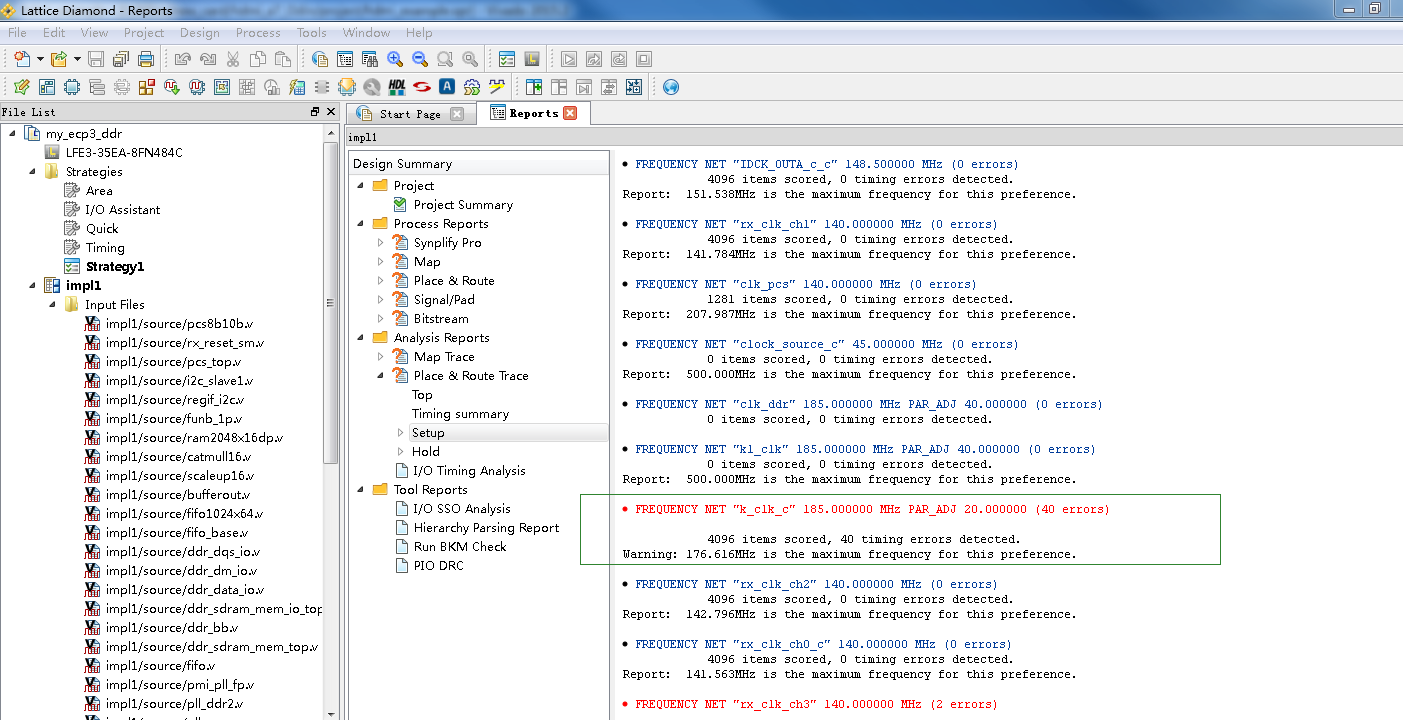

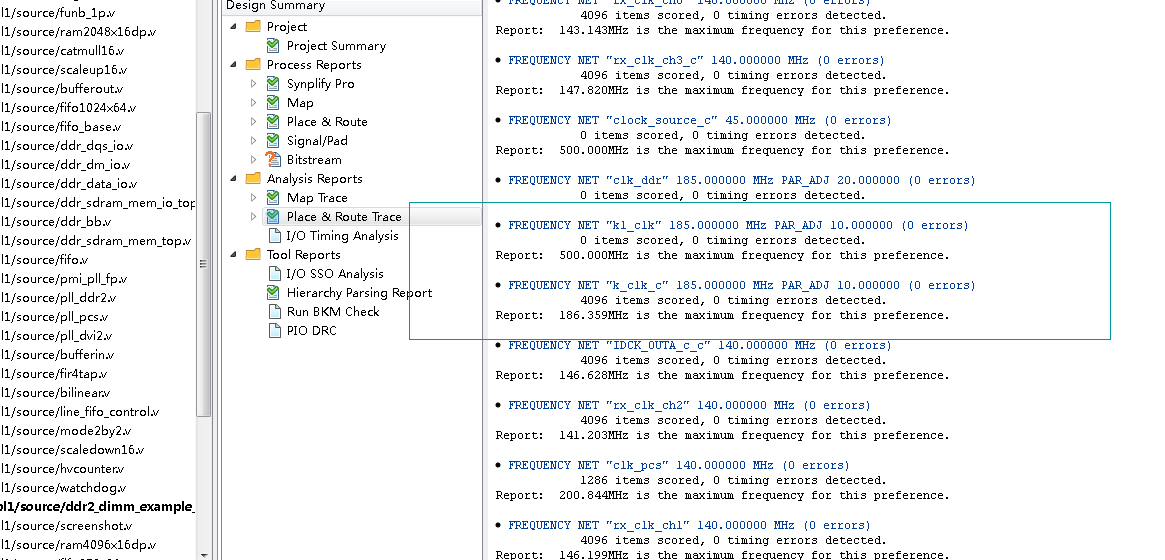

因为 ddr相关的时序报告,一直没有过去。所以一直比较担心。因为 跑到185Mhz,确实也不容易。所以就没管它。

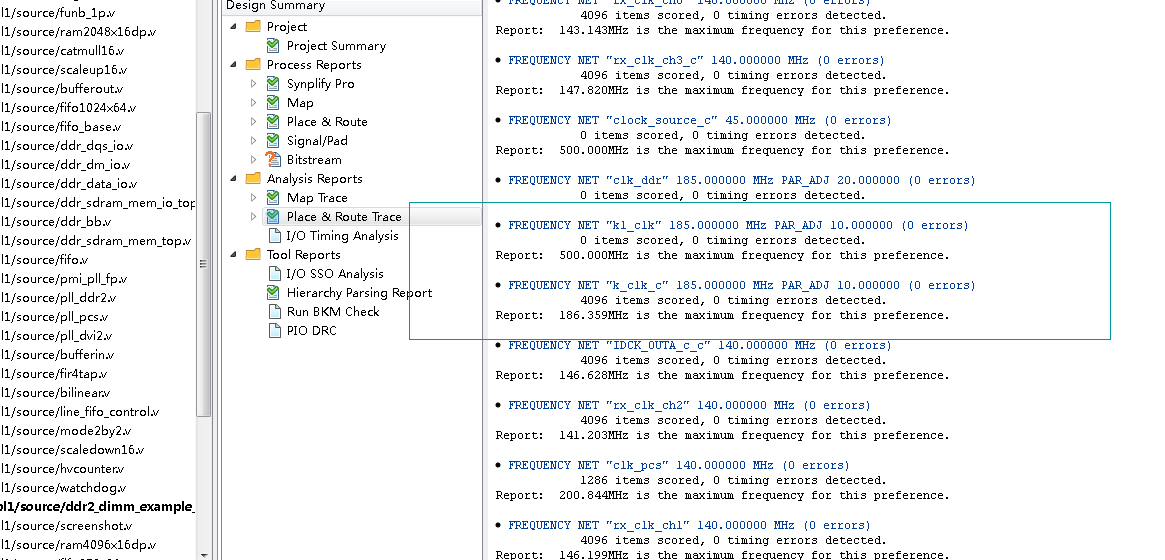

这次就作手改时序报告, 花了好长时间,终于把时序跑过了。

在项目上运行了20天,还没有问题。应该算是 解决了。

崩溃ing。。。。。。。。

又出问题了。我断定必然不是 FPGA代码的问题,于是让硬件工程师 量了量 电压参数, 发现 DDR的参考电压1.8v比 要求的参考电压偏高。 我也是醉了,硬件工程师改了改电阻的阻值, 于是就好了。

总结: 一、 在FPGA设计中, 约束一定要做好, 一定要覆盖所有的路径, 时序报告要通过。切记。。

二、出现 没有规律的随机问题, 基本上可以怀疑是硬件设计的问题, 最应该先做的事情,应该是 检查是不是电源问题 或者 芯片的电压参数之类的。

项目上用的 lattice 的 ecp3-35,esmt的ddr. 之前 用 了一年多,一直没有没有问题。 最近新贴的一批板子, 在运行10天左右,经常会出现DDR读写错误。现象如下:

一开始怀疑是 DDR的问题,然后就想作手改板。换成DDR3.

因为 ddr相关的时序报告,一直没有过去。所以一直比较担心。因为 跑到185Mhz,确实也不容易。所以就没管它。

这次就作手改时序报告, 花了好长时间,终于把时序跑过了。

在项目上运行了20天,还没有问题。应该算是 解决了。

崩溃ing。。。。。。。。

又出问题了。我断定必然不是 FPGA代码的问题,于是让硬件工程师 量了量 电压参数, 发现 DDR的参考电压1.8v比 要求的参考电压偏高。 我也是醉了,硬件工程师改了改电阻的阻值, 于是就好了。

总结: 一、 在FPGA设计中, 约束一定要做好, 一定要覆盖所有的路径, 时序报告要通过。切记。。

二、出现 没有规律的随机问题, 基本上可以怀疑是硬件设计的问题, 最应该先做的事情,应该是 检查是不是电源问题 或者 芯片的电压参数之类的。

相关文章推荐

- FPGA关于时序报告的问题

- 关于 FPGA 和 外部芯片接口时序设计

- 关于 FPGA 和 外部芯片接口时序设计

- 关于FPGA设计仿真和硬件实测不一致问题

- 关于FPGA设计16位乘法器的两…

- 关于FPGA内部双口RAM的时序总结:

- 《C++第六周实验报告3-1》---设计平面坐标点类,计算两点之间距离、到原点距离、关于坐标轴和原点的对称点等

- 静态时序分析在高速FPGA设计中的应用

- 【转载】如何在FPGA设计环境中添加加时序约束

- FPGA 设计中的流量,时滞,时序

- 在FPGA设计环境中加时序约束

- 关于原型设计的重要性

- 关于设计器的预研报告

- 关于FPGA逻辑设计的21个小贴士

- 关于FPGA逻辑设计的21个小贴士

- 关于FPGA设计16位乘法器的两…

- (转)如何在FPGA设计环境中加时序约束

- 如何实现复杂FPGA设计的时序收敛

- 【转】FPGA高级设计之时序分析和收敛

- 关于FPGA设计仿真和硬件实测不一致问题的讨论