FIFO结构与实现

2016-04-14 23:03

337 查看

大家好!好久不见,前一段时间出差没有来得及更新Blog,小小的愧疚一下。今天,主要介绍的是Xilinx 7 Series FIFO的结构,以及代码实现。

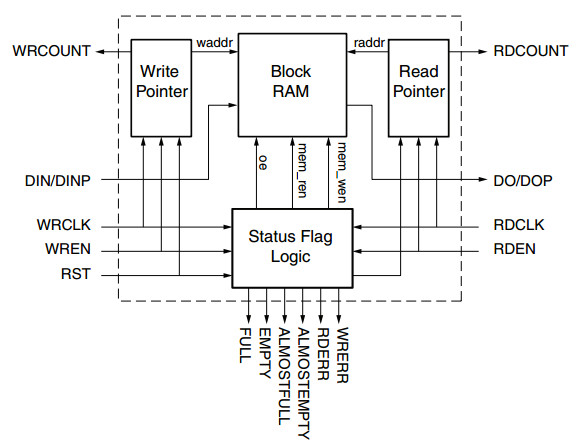

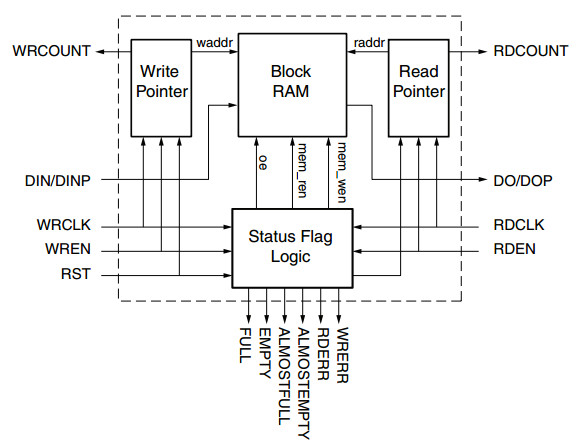

FIFO的结构如下图所示,分为状态标志产生模块、写指针模块、双端口Ram以及读指针模块。

本文先介绍一下同步FIFO的实现方式,next time详细介绍异步FIFO。其中,同步FIFO的状态标志产生模块,主要根据写/读的指针与设定的深度/Almost Full/Almost Empty进行比较,来产生Full/Afull/Empty/Aempty的标志信号,并在FIFO出现Full和Empty时对写/读进行保护。满标志信号产生代码如下:

空标志产生代码如下:

同理与以上full和empty的产生过程,afull和aempty只需要改变left的判断数值就可以了。

若full和empty的时候,则需要对写和读进行保护,代码如下:

Left状态产生代码如下:

写/读指针产生模块代码:

同步FIFO的实现较为简洁,也比较理解。异步FIFO不同与同步FIFO的时,读/写端口的时钟不同,其内部比较产生状态信号的指针不同,他是将二进制指针转化为格雷码指针,然后进行比对,下一篇bolg会进行详细介绍。

FIFO的结构如下图所示,分为状态标志产生模块、写指针模块、双端口Ram以及读指针模块。

本文先介绍一下同步FIFO的实现方式,next time详细介绍异步FIFO。其中,同步FIFO的状态标志产生模块,主要根据写/读的指针与设定的深度/Almost Full/Almost Empty进行比较,来产生Full/Afull/Empty/Aempty的标志信号,并在FIFO出现Full和Empty时对写/读进行保护。满标志信号产生代码如下:

always @(posedge clk or posedge rst) if (rst) full <= 1'b0; else case(winc,rinc) 2'b10 : full <= (left == C_DEP - 1) ? 1'b1 : 1'b0; 2'b01 : full <= (left == C_DEP) ? 1'b0 : 1'b1; default : full <= full; endcase

空标志产生代码如下:

always @(posedge clk or posedge rst) if (rst) empty <= 1'b0; else case(winc,rinc) 2'b01 : empty <= (left == 1) ? 1'b1 : 1'b0; 2'b10 : empty <= (left == 0) ? 1'b0 : 1'b1; default : empty <= empty; endcase

同理与以上full和empty的产生过程,afull和aempty只需要改变left的判断数值就可以了。

若full和empty的时候,则需要对写和读进行保护,代码如下:

winc = wr_en && !full; rinc = rd_en && !empty;

Left状态产生代码如下:

always @(posedge clk or posedge rst)

if (rst)

left <= {C_PW{1'b0}}:

else

case(winc,rinc)

2'b10 : left <= left + 1'b1;

2'b01 : left <= left - 1'b1;

default : left <= left;

endcase写/读指针产生模块代码:

always @(posedge clk or posedge rst)

if (rst)

wr_pointer <= {C_PW{1'b0}};

else if (winc)

wr_pointer <= wr_pointer + 1'b1;

always @(posedge clk or posedge rst)

if (rst)

rd_pointer <= {C_PW{1'b0}};

else if (rinc)

rd_pointer <= rd_pointer + 1'b1;同步FIFO的实现较为简洁,也比较理解。异步FIFO不同与同步FIFO的时,读/写端口的时钟不同,其内部比较产生状态信号的指针不同,他是将二进制指针转化为格雷码指针,然后进行比对,下一篇bolg会进行详细介绍。

相关文章推荐

- 《FPGA嵌入式项目开发实战》

- 关于FPGA中的Logic Cells, Logic Slices, Configurable Logic Blocks and Gates

- DSP多网口开发板

- Utilities Zynq in a PL only configuration

- Linux C 编程----有名管道FIFO

- Linux C 编程----有名管道FIFO,程序更新

- ARM11 S3C6410系列教程之二:串口

- shell 命名管道,进程间通信

- ARM+FPGA核心板

- DSP+ARM+FPGA核心板

- 基于VHDL的按键扫描程序

- Xilinx FPFA中LUT4_L 元件的使用

- ISE 综合面积报告分析

- 深圳嵌入式培训 修练软硬件之功 高薪一路相伴

- FPGA点灯

- 深圳视晶无线技术有限公司 狗血经历

- TMS320F28335学习SPI模块总结笔记

- 卫星导航同步时的环路更新时间架构

- 载波同步环路的带宽与信噪比相关问题

- 一只老鸟嵌入式工程师的血泪史!