汇编学习1

2016-04-03 16:20

183 查看

汇编器:汇编语言 –>机器语言

连接器:把汇编器创建的多个单独文件连接成可执行程序

汇编语言和机器语言一一对应

左高右低。

整数存储

字节Byte:8位

字word:2字节,2Byte。16位

双字doubleword:4字节。32位

八字节:8字节。64位

补码

一个数的补码就是它的相反数(一个数与它的补码相加和为0),

求补码:取反加一

字符存储

ASCII, 用低7位,最高位创建私有字符

ANSI字符集,256字符,后128特殊字符

Unicode标准,:UTF-8, UTF-16, UTF-32

ASCII字符串

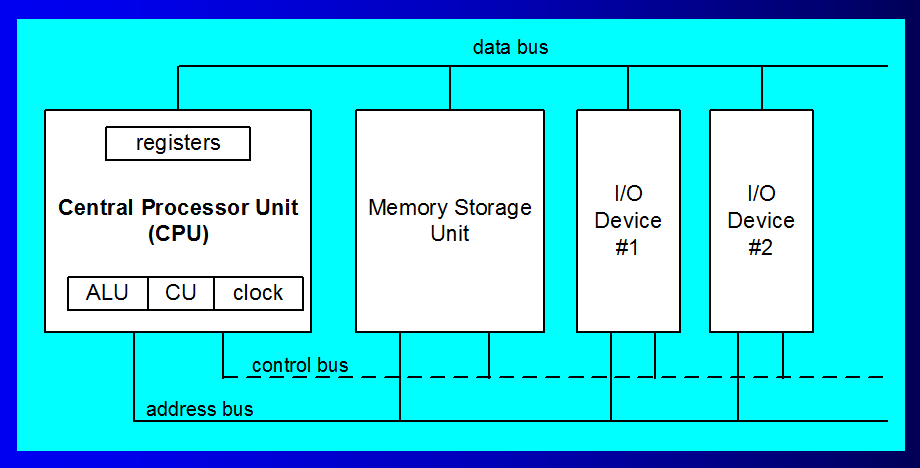

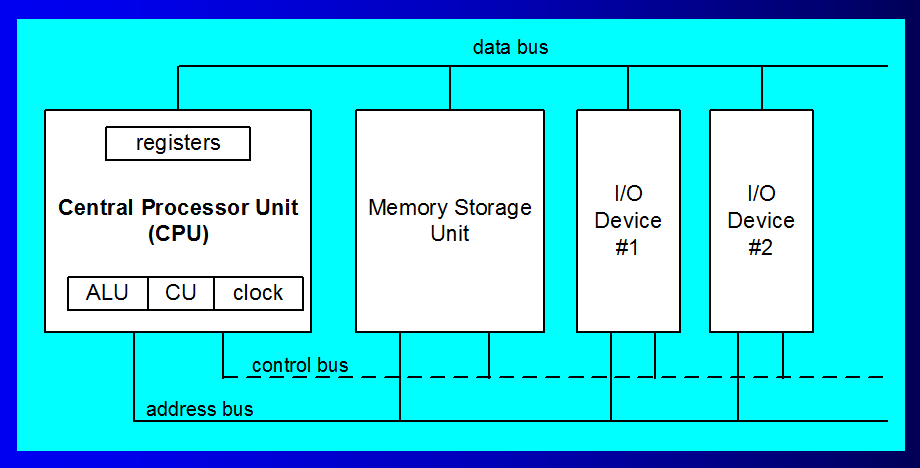

2. 微机结构:

clock:时钟用于CPU的内部操作和其他系统部件的同步

Cu:控制单元协调执行机器指令时各个步骤的次序

ALU:算术逻辑单元执行算术运算和逻辑运算

mem stor unit:内存存储单元存放指令和数据

总线:传送数据,并行线

数据总线:CPU内存间传送指令和数据

控制总线:用二进制信号同步连接到系统总线上的所有设备的动作

地址总线:如果当前指令要在CPU和内存间传送数据,地址总线上保持着指令和数据的地址

时钟:固定废品率产生脉冲,一个完整时间脉冲(两个下降沿间间隔)所需要的时间是 机器周期 (机器指令使用的最基本的时间单位

3. 指令周期

单条机器指令的执行可以被分解为一系列的独立操作,这些操作构成指令执行的一个周期

程序开始执行前必须首先装入 内存,指令指针 包含要执行的下一条指令的地址, 指令队列 存放若干条将要执行的指令,

三个步骤:

1.取指,控制单元从 指令队列 中取得指令并递增指令指针(EIP)的值,指令指针也称为程序计数器

2.解码,控制单元对指令解码,把输入操作数传递给ALU,并向算术逻辑单元发送信号指明要执行的操作

*取操作数(额外步骤),控制单元从内存中读操作数,复制到内部寄存器中

3.执行,算术逻辑单元执行指令,送出运算输出结果,更新反应处理器状态的状态标志

*存储输出操作数(额外),存储数据到内存中。

4. 流水线

指令执行 每一步 占用 一个 时钟周期, 但处理器可以并行执行其他步骤。

Intel 486 6级流水线:

总线接口单元BIU:访问存储器提供输入输出

代码预取单元:从BIU接收机器指令并将其插入称为指令队列的存储区域

指令解码单元:对预取队列中的机器指令进行解码,将他们翻译为微代码

执行单元:执行指令解码单元产生的微代码

分段部件:把逻辑地址转换为线性地址并进行保护检查

分页部件:把线性地址转换为物理地址,进行页保护检查

n*k模型:

k+(n-1)模型:

k + n 模型:超标量流水线

5. 内存读取

步骤由cpu内部时钟控制

周期1:内存操作数的地址被放到地址总线ADDR上

周期2:读取线(RD)设为低(0),通知存储器要读取一个值

周期3:cpu等待一个周期,给存储器时间响应。这个时钟周期内,内存控制器把数据放在数据线

(DATA) 上。

周期4:读取线(RD)变为一,通知cpu在数据总线(DATA)上读取数据

保护模式

程序被赋予了独立的内存区域(称为段),处理器阻止程序访问分配段之外的其他内存

虚拟8086模式

(保护模式的特例)在保护模式下,执行多个虚拟8086任务,即在 安全的多任务环境下运行实地址模式的软件 ,即使一个如 MS-DOS 程序崩溃或试图向系统内存写入数据,也不会影响同时运行的其他程序

实地址模式

实地址模式实现了 Intel 8086 处理器的程序设计环境,可用于运行那些需要直接访问系统内存和硬件设备的MS-DOS 程序。* 实地址模式下运行的程序可能导致操纵系统挂起 *

系统管理模式

2. 基本执行环境

1. 地址空间

保护模式下,IA-32最高可访问4GB内存,32位无符号整数寻址上限。(32-bit address)

实地址程序只能访问1MB内存(20-bit address)

保护模式下虚拟8086模式运行多个程序,每个程序都能访问独立 1MB内存区域(20-bit address)

2. 寄存器

还有更多的寄存器之后会学习到

3. 历史

Intel 8086:16位寄存器16位数据总线 1MB内存

Intel 8088 :8位数据总线,其余同上

Intel 80286: 24位地址,16MB内存

IA-32系列:

Intel 386 : 32位寄存器,32位地址总线,32位外部数据通道, 每个程序4GB线性地址空间

Intel 486:流水线技术,同时处理多条指令

奔腾:32位地址,64位内部数据通道

奔腾4,Xeon

4. CISC RISC

CISC:

高级运算,微代码解释器,复杂指令

RISC:

精简指令,少,硬件直接解码执行

20位地址线,访问1MB内存,

如何用8086的16位寄存器存放20位的地址

分段内存方案:

所有内存被分为多个64kb区域,这些区域称为段

所以,实际地址等于 16位段的基地址加上16位的偏移地址

注意:每个段在被表示时省略了最后一个0,C000实际上是从C0000开始的段

如:80250h = 8000:0250

08F1:0100 = 08F1h * 10h + 0100h = 09010h

保护模式

每个程序可寻址4GB内存,0~FFFFFFFF

平坦分段模式

基址,界限,段描述符,全局描述符表GDT, 0040*1000=00040000

10000*1000=10000000

多段模式

局部描述符表LDT,基址,界限计算同上

分页 (IA-32)

段分割为多页,

一页:4096字节

分页机制允许同时运行的程序使用的总内存 远大于计算机的物理内存,

所有页的集合合称虚拟内存

分页机制(使用后备磁盘存储)

一个程序越依赖分页机制,运行也可能越慢

补:

1.EFLAGS扩展标志,

2.FPU浮点单元:高速浮点算数运算

3.视频适配器:视频控制器+视频显示存储器(显存)

4.存储器:

连接器:把汇编器创建的多个单独文件连接成可执行程序

汇编语言和机器语言一一对应

1.数位进制

二进制左高右低。

整数存储

字节Byte:8位

字word:2字节,2Byte。16位

双字doubleword:4字节。32位

八字节:8字节。64位

补码

一个数的补码就是它的相反数(一个数与它的补码相加和为0),

求补码:取反加一

字符存储

ASCII, 用低7位,最高位创建私有字符

ANSI字符集,256字符,后128特殊字符

Unicode标准,:UTF-8, UTF-16, UTF-32

ASCII字符串

2.处理器

1. IA-32:始于803862. 微机结构:

clock:时钟用于CPU的内部操作和其他系统部件的同步

Cu:控制单元协调执行机器指令时各个步骤的次序

ALU:算术逻辑单元执行算术运算和逻辑运算

mem stor unit:内存存储单元存放指令和数据

总线:传送数据,并行线

数据总线:CPU内存间传送指令和数据

控制总线:用二进制信号同步连接到系统总线上的所有设备的动作

地址总线:如果当前指令要在CPU和内存间传送数据,地址总线上保持着指令和数据的地址

时钟:固定废品率产生脉冲,一个完整时间脉冲(两个下降沿间间隔)所需要的时间是 机器周期 (机器指令使用的最基本的时间单位

3. 指令周期

单条机器指令的执行可以被分解为一系列的独立操作,这些操作构成指令执行的一个周期

程序开始执行前必须首先装入 内存,指令指针 包含要执行的下一条指令的地址, 指令队列 存放若干条将要执行的指令,

三个步骤:

1.取指,控制单元从 指令队列 中取得指令并递增指令指针(EIP)的值,指令指针也称为程序计数器

2.解码,控制单元对指令解码,把输入操作数传递给ALU,并向算术逻辑单元发送信号指明要执行的操作

*取操作数(额外步骤),控制单元从内存中读操作数,复制到内部寄存器中

3.执行,算术逻辑单元执行指令,送出运算输出结果,更新反应处理器状态的状态标志

*存储输出操作数(额外),存储数据到内存中。

4. 流水线

指令执行 每一步 占用 一个 时钟周期, 但处理器可以并行执行其他步骤。

Intel 486 6级流水线:

总线接口单元BIU:访问存储器提供输入输出

代码预取单元:从BIU接收机器指令并将其插入称为指令队列的存储区域

指令解码单元:对预取队列中的机器指令进行解码,将他们翻译为微代码

执行单元:执行指令解码单元产生的微代码

分段部件:把逻辑地址转换为线性地址并进行保护检查

分页部件:把线性地址转换为物理地址,进行页保护检查

n*k模型:

k+(n-1)模型:

k + n 模型:超标量流水线

5. 内存读取

步骤由cpu内部时钟控制

周期1:内存操作数的地址被放到地址总线ADDR上

周期2:读取线(RD)设为低(0),通知存储器要读取一个值

周期3:cpu等待一个周期,给存储器时间响应。这个时钟周期内,内存控制器把数据放在数据线

(DATA) 上。

周期4:读取线(RD)变为一,通知cpu在数据总线(DATA)上读取数据

3.IA-32体系结构

1. 操作模式保护模式

程序被赋予了独立的内存区域(称为段),处理器阻止程序访问分配段之外的其他内存

虚拟8086模式

(保护模式的特例)在保护模式下,执行多个虚拟8086任务,即在 安全的多任务环境下运行实地址模式的软件 ,即使一个如 MS-DOS 程序崩溃或试图向系统内存写入数据,也不会影响同时运行的其他程序

实地址模式

实地址模式实现了 Intel 8086 处理器的程序设计环境,可用于运行那些需要直接访问系统内存和硬件设备的MS-DOS 程序。* 实地址模式下运行的程序可能导致操纵系统挂起 *

系统管理模式

2. 基本执行环境

1. 地址空间

保护模式下,IA-32最高可访问4GB内存,32位无符号整数寻址上限。(32-bit address)

实地址程序只能访问1MB内存(20-bit address)

保护模式下虚拟8086模式运行多个程序,每个程序都能访问独立 1MB内存区域(20-bit address)

2. 寄存器

还有更多的寄存器之后会学习到

3. 历史

Intel 8086:16位寄存器16位数据总线 1MB内存

Intel 8088 :8位数据总线,其余同上

Intel 80286: 24位地址,16MB内存

IA-32系列:

Intel 386 : 32位寄存器,32位地址总线,32位外部数据通道, 每个程序4GB线性地址空间

Intel 486:流水线技术,同时处理多条指令

奔腾:32位地址,64位内部数据通道

奔腾4,Xeon

4. CISC RISC

CISC:

高级运算,微代码解释器,复杂指令

RISC:

精简指令,少,硬件直接解码执行

4.IA-32内存管理

实模式20位地址线,访问1MB内存,

如何用8086的16位寄存器存放20位的地址

分段内存方案:

所有内存被分为多个64kb区域,这些区域称为段

所以,实际地址等于 16位段的基地址加上16位的偏移地址

注意:每个段在被表示时省略了最后一个0,C000实际上是从C0000开始的段

如:80250h = 8000:0250

08F1:0100 = 08F1h * 10h + 0100h = 09010h

保护模式

每个程序可寻址4GB内存,0~FFFFFFFF

平坦分段模式

基址,界限,段描述符,全局描述符表GDT, 0040*1000=00040000

10000*1000=10000000

多段模式

局部描述符表LDT,基址,界限计算同上

分页 (IA-32)

段分割为多页,

一页:4096字节

分页机制允许同时运行的程序使用的总内存 远大于计算机的物理内存,

所有页的集合合称虚拟内存

分页机制(使用后备磁盘存储)

一个程序越依赖分页机制,运行也可能越慢

补:

1.EFLAGS扩展标志,

2.FPU浮点单元:高速浮点算数运算

3.视频适配器:视频控制器+视频显示存储器(显存)

4.存储器:

相关文章推荐

- liunx 用户,群组和权限

- 服务器架构--------iis与Apache共存搭建(都可以使用域名访问,而不带后面的:80,90等)

- from __future__ import absolute_import的作用

- Android中的Semaphore

- hdu1007 Quoit Design【平面最近点对+分治】

- 设计模式 - 动态代理

- RxJava-创建Observable操作符

- UVA5135 Mining Your Own Business ( 无向图双连通分量)

- 在centos7 或 RHEL 7上使用yum测试zabbix 2.4

- HDU 4812 D Tree 点分治

- fzu 2122 又见LKity

- 97 等价交换(贪心-2)

- 计算机网络overview-2

- 最小堆最大堆的详细解读

- 为什么开通博客

- Git托管代码

- 深入浅出 RPC - 深入篇

- JAVA虚拟机-JVM性能调优(五)

- jquery 点击元素以外任意地方隐藏该元素的方法

- 概率论与数量统计(二)1___ 随机事件与概率