使用verilog实现模块级联

2016-03-19 00:00

1521 查看

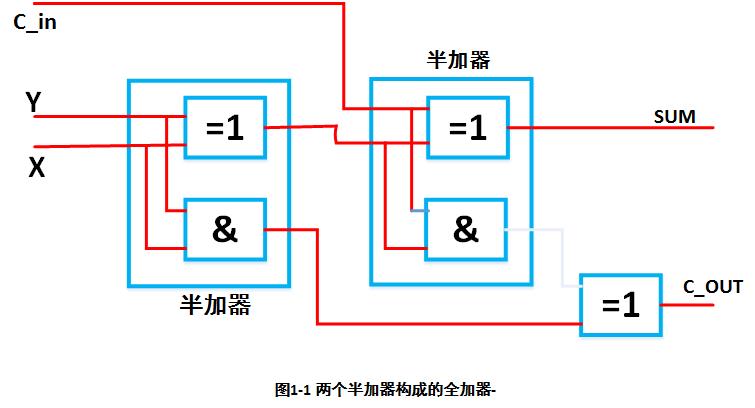

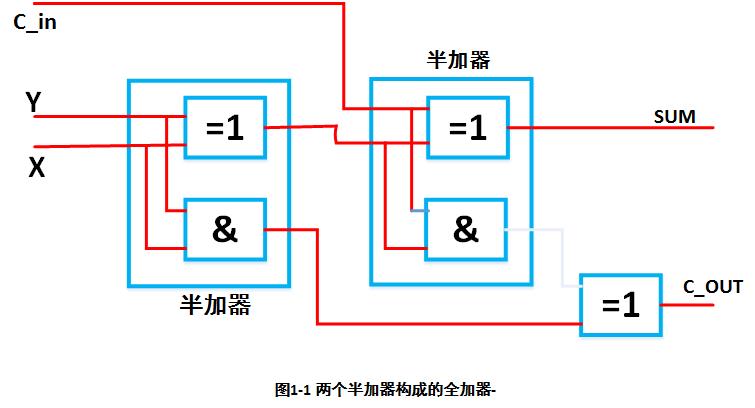

摘要: 本文介绍两个半加器级联成为一个全家器的过程,加深对模块级联的理解!

一个verilog程序可以包含多个模块,以满足一个复杂的程序设计。调用多个模块是通过端口关联来进行实现的,这种调用实际上是 一种硬件电路的嵌入,调用的方式是模块实例化,其中端口关联有两种方式:一种是位置关联,一种是名称关联,形式为“.端口名(变量名)“,实现端口与变量的关联。下面通过两个半加器来实现一个全加器来加以说明调用的方式:

moudle HalfAdd(X,Y,SUM,C_out);

input X,Y;

output SUM,C_out;

xor u_xor(SUM,X,Y);

and u_and(C_out,X,Y);

endmoudle

moudle FullAdd(X,Y,C_in,SUM,C_out);

input X,Y;

output C_in,Sum,C_out;

wire HalfAdd_A_SUM;

wire HalfAdd_A_COUT;

wire HalfAdd_B_COUT;

or u_or(C_out,HalfAdd_A_COUT,HalfAdd_B_COUT);

HalfAdd u_HalfAdd_A(.X(X),.Y(Y),.SUM(HalfAdd_A_SUM),.C_out(HalfAdd_A_COUT));

HalfAdd u_HalfAdd_B(.X(X),.Y(Half_A_SUM),.SUM(SUM),C_out(HalfAdd_B_COUT)));

endmoudle

一个verilog程序可以包含多个模块,以满足一个复杂的程序设计。调用多个模块是通过端口关联来进行实现的,这种调用实际上是 一种硬件电路的嵌入,调用的方式是模块实例化,其中端口关联有两种方式:一种是位置关联,一种是名称关联,形式为“.端口名(变量名)“,实现端口与变量的关联。下面通过两个半加器来实现一个全加器来加以说明调用的方式:

moudle HalfAdd(X,Y,SUM,C_out);

input X,Y;

output SUM,C_out;

xor u_xor(SUM,X,Y);

and u_and(C_out,X,Y);

endmoudle

moudle FullAdd(X,Y,C_in,SUM,C_out);

input X,Y;

output C_in,Sum,C_out;

wire HalfAdd_A_SUM;

wire HalfAdd_A_COUT;

wire HalfAdd_B_COUT;

or u_or(C_out,HalfAdd_A_COUT,HalfAdd_B_COUT);

HalfAdd u_HalfAdd_A(.X(X),.Y(Y),.SUM(HalfAdd_A_SUM),.C_out(HalfAdd_A_COUT));

HalfAdd u_HalfAdd_B(.X(X),.Y(Half_A_SUM),.SUM(SUM),C_out(HalfAdd_B_COUT)));

endmoudle

相关文章推荐

- substr 的用法

- 文件上传中临时文件的清除和上传进度的展示

- 今天闲着没事敲了几个简单的框架

- PHP Date()函数详细参数

- ThinkPHP IF标签用法笔记

- 加盟美石记韩式拌饭 收获一份美味的事业

- 尚品宫韩式烧烤 无忧致富好项目

- Sql server安装时出现找不到vc_red.msi错误

- Android 从setContentView谈Activity界面的加载过程

- Centos7安装Scrapy过程

- _过程_函数_触发器_游标

- 某公司希捷硬盘严重物理坏道的数据恢复

- linux下MySQL的备份与还原

- 什么是HTTP 1.1代理?

- HTTP请求方法 之 OPTIONS (zz)

- 使用ajax跨域withCredentials的作用

- 跨域资源共享(CORS)安全性浅析

- HTML5安全风险详析之一:CORS攻击

- CORS(跨域资源共享) 的配置

- CSRF简单介绍及利用方法