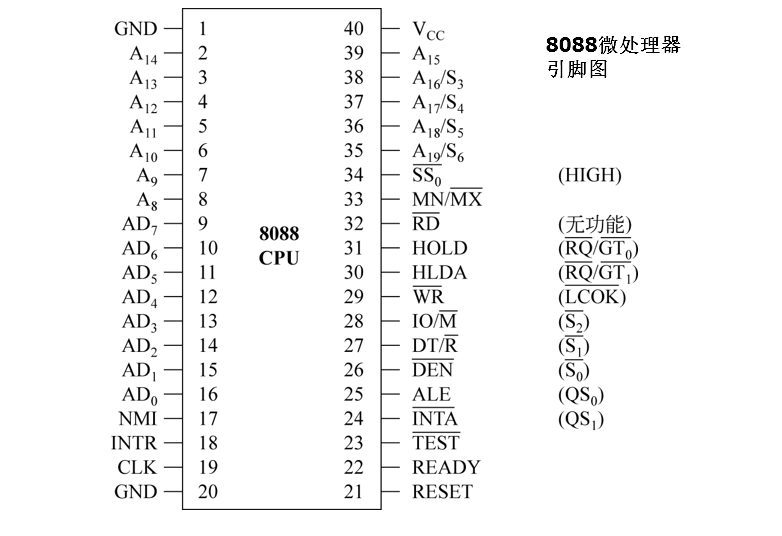

8088微处理器引脚

2016-03-05 19:56

169 查看

最小模式下

1、AD0—AD7:低8位地址和低8位数据信号分时复用。在传送地址信号时为单向,传送数据信号时为双向。

2、A8—A15 :8位地址信号

3、A16–A19:高4位地址信号,与状态信号分时复用。

4、SS0与IO/M、DT/R决定了当前的总线周期的状态(见附录B.1)

5、S6 (与A19复用)恒为0

6、S5 (与A18复用)表示IF的状态

7、S3(与A16复用)与S4(与A17复用)组合表示当前正在使用的段寄存器

8、WR: 写信号;

9、RD: 读信号;

10、IO/M:为“0”表示访问内存;为“1”表示访问接口;

11、DEN: 低电平有效时,允许进行读/写操作;

12、DT/R:数据收发器的传送方向控制;

13、ALE:地址锁存信号;

14、INTR:可屏蔽中断请求输入端

15、NMI: 非屏蔽中断请求输入端

16、INTA:中断响应输出端

17、HOLD:总线保持请求信号输入端。当CPU

以外的其他设备要求占用总线时,

通过该引脚向CPU发出请求。

18、HLDA:总线保持响应信号输出端。CPU对

HOLD信号的响应信号。

19、Vcc:5v电源输入引脚。

20、GND:地线。

21、TEST:测试信号输入引脚。当CPU执行wait指令时,每5个时钟周期将对引脚进行测试,为低电平时结束等待。

22、RESET:复位信号。指令队列清空;CS为0FFFFH,其余寄存器为0.

23、CLK:时钟信号输入引脚。

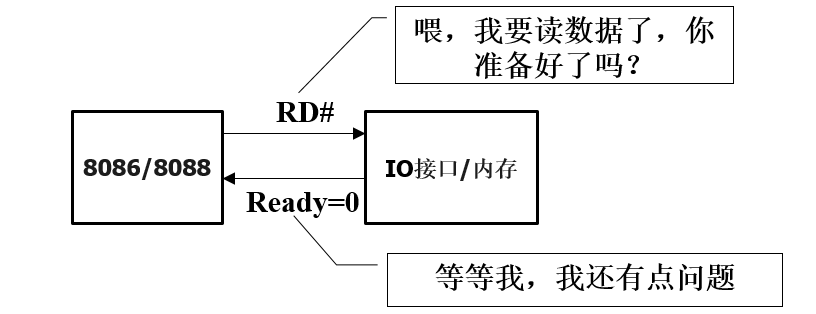

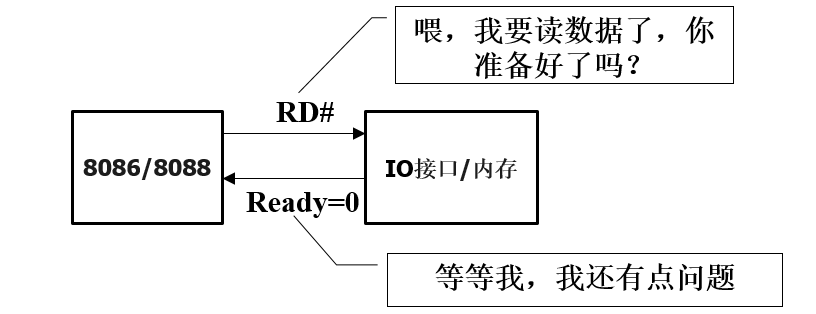

24、ready:外部同步控制输入信号,高电平有效,8088与内存/外设之间在一个总线周期内的时钟配合信号

最大模式下

25、S0,S1,S2代表总线周期状态信号(输出、三态),CPU并不直接向外界提供全部控制信号,而由S0,S1,S2 通过Intel 8288总线控制器提供

26、 RQ/GT0,,RQ/GT1 : 总线请求(输入)/总线请求允许信号(输出)(双向、均为低电平有效)

27、LOCK : 总线封锁信号(输出、三态、低电平有效)

28、QS0,QS1 指令队列状态信号(输出)

29、HIGH 始终为高电平

8088和8086的区别

1:数据总线宽度不同

8088的外部数据总线宽度是8位,8086为16位。

2:访问存储器和输入输出控制信号含义不同

8088——IO/M=0表示访问内存;

8086——IO/M=1表示访问内存。

3:其他部分引线功能的区别

在8086中SS0引脚改为BHE,以适应16位的数据宽度

1、AD0—AD7:低8位地址和低8位数据信号分时复用。在传送地址信号时为单向,传送数据信号时为双向。

2、A8—A15 :8位地址信号

3、A16–A19:高4位地址信号,与状态信号分时复用。

4、SS0与IO/M、DT/R决定了当前的总线周期的状态(见附录B.1)

5、S6 (与A19复用)恒为0

6、S5 (与A18复用)表示IF的状态

7、S3(与A16复用)与S4(与A17复用)组合表示当前正在使用的段寄存器

| s4 | s3 | 当前正在使用的寄存器 |

|---|---|---|

| 0 | 0 | ES |

| 0 | 1 | SS |

| 1 | 0 | CS或者未使用任何寄存器 |

| 1 | 1 | DS |

9、RD: 读信号;

10、IO/M:为“0”表示访问内存;为“1”表示访问接口;

11、DEN: 低电平有效时,允许进行读/写操作;

13、ALE:地址锁存信号;

14、INTR:可屏蔽中断请求输入端

15、NMI: 非屏蔽中断请求输入端

16、INTA:中断响应输出端

17、HOLD:总线保持请求信号输入端。当CPU

以外的其他设备要求占用总线时,

通过该引脚向CPU发出请求。

18、HLDA:总线保持响应信号输出端。CPU对

HOLD信号的响应信号。

19、Vcc:5v电源输入引脚。

20、GND:地线。

21、TEST:测试信号输入引脚。当CPU执行wait指令时,每5个时钟周期将对引脚进行测试,为低电平时结束等待。

22、RESET:复位信号。指令队列清空;CS为0FFFFH,其余寄存器为0.

23、CLK:时钟信号输入引脚。

24、ready:外部同步控制输入信号,高电平有效,8088与内存/外设之间在一个总线周期内的时钟配合信号

最大模式下

25、S0,S1,S2代表总线周期状态信号(输出、三态),CPU并不直接向外界提供全部控制信号,而由S0,S1,S2 通过Intel 8288总线控制器提供

26、 RQ/GT0,,RQ/GT1 : 总线请求(输入)/总线请求允许信号(输出)(双向、均为低电平有效)

27、LOCK : 总线封锁信号(输出、三态、低电平有效)

28、QS0,QS1 指令队列状态信号(输出)

29、HIGH 始终为高电平

8088和8086的区别

1:数据总线宽度不同

8088的外部数据总线宽度是8位,8086为16位。

2:访问存储器和输入输出控制信号含义不同

8088——IO/M=0表示访问内存;

8086——IO/M=1表示访问内存。

3:其他部分引线功能的区别

在8086中SS0引脚改为BHE,以适应16位的数据宽度

相关文章推荐

- 《Linux内核分析》第二课笔记

- Java连接Mysql数据库警告:Establishing SSL connection without server's identity verification is not recommend

- Android 6.0删除Apache HttpClient相关类的解决方法

- [Leetcode]-Remove Duplicates from Sorted Array

- xinu在vbox上,使用debian8,并在上面进行xinu编程

- 在Linux最小系统上编译运行第一个helloworld程序

- 掌握DEBUG 基本命令及其功能

- 钱币兑换问题

- iOS Runloop学习

- 【项目 2 - 就拿胖子说事】

- Android中的享元模式

- 如何新建gitHub帐号并与自己电脑进行关联

- IOS学习资源收集--开发UI控件相关

- AI制作牙膏笔刷文字

- PHP正则表达式

- 上机题目(初级)- 鼠标控制小球(Java)

- 太毒的文件操作错误

- 运行Android studio 模板报错

- An ant's story

- 【深入了解cocos2d-x 3.x】定时器(scheduler)的使用和原理探究(3)