SDRAM 学习笔记(三)

2016-01-20 15:27

447 查看

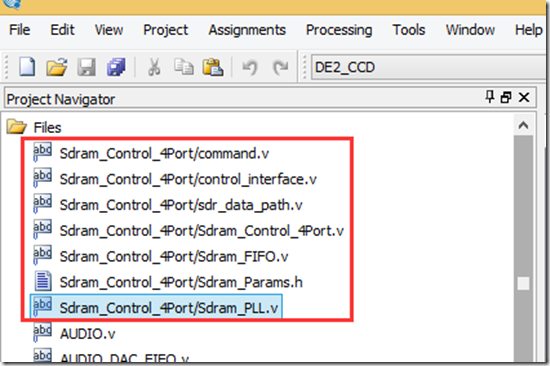

上图是terasic公司提供的SDRAM控制器,大部分已经封装好,我们需要修改其中部分代码,以此来实现我们自己需要的功能。

1.PLL时钟设定

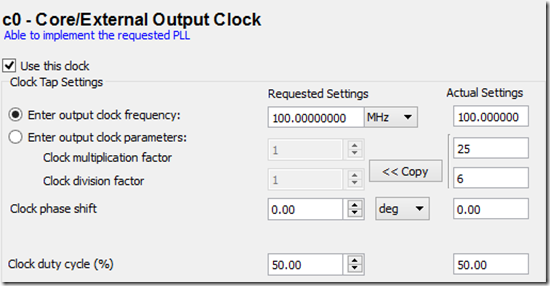

首先上面的sdram_pll.v中产生上一篇博客所需要的“驱动时钟”和“控制时钟”,这两个时钟由于PCB走线延时,两个时钟会有一定的时间差,一般会设定在-3ns ~ 1ns之间。如下图所示:

上图是对SDRAM的PLL进行的更改,这个时钟差设定多少没有严格规定,可以先设定一个值,读取出图像进行调试,看图像是否帧错位或者图像显示不正确等原因,多是由于PLL没有配置好所导致,可以修改此部分进行修改,重新设定。

2.SDRAM_parameter.h 参数设置

之前在VGA显示一篇博客中,就用到了这种思想,就是将常用的参数设定在一个.h文件或者.v文件,然后利用 `include "Sdram_Params.h"加载进来即可。

在此模块中,我们需要将常用到的一些参数设置好,主要用到以下一些参数:

(1) SDRAM parameter.h

笔者使用H57V2562GTR和H57V641620E系列,再此以H57V2562GTR为例。

//==================================================

//address space parameters

// 4M x 4 x 16bit = (8192 x 512)x 4 x 16bit = 256Mbit 注意,8192和512分别为行数和列数。

//行和列的地址,行是12位的,列是8位的,所以会用到这样的乘积。

//宏定义的参数

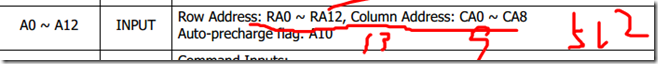

‘define ROWSIZE 13 //行的宽度在一个bank中

‘define COLSIZE 9 //列的宽度在一个bank中

‘define DSIZE 16 //width of data bus to SDRAM 16bit SDRAM data

‘define BANKSIZE 2 //4 banks in one SDRAM

//所利用宏定义的参数

‘define COLSTART 0

‘define ROWSTART ‘COLSIZE

‘define BANKSTART ‘COLSIZE + ‘ROWSIZE

‘define ASIZE ‘ROWSIZE + ‘ COLSIZE + ’ BANKSIZE

//==================================

//上述是对SDRAM的位宽,行宽,列宽,行起始,列起始,bank数,进行设置。已经最大限度参数化,对

//于同一类hynix这一部分所需要更改的只需更改ROWSIZE和COLSIZE以及DSIZE即可。

//==================================================

(2) 按照SDRAM的驱动流程,那么接下来应该是先200us的SDRAM的稳定启动。

INIT_PER = 200us / T = 200 x 10^3ns / (1000/CLK) = 200 x CLK;

其中CLK为xxMHz的驱动时钟频率,已经转换为ns状态下,所以为1000/clk。以上是计算出来的是延时计 数,就是一开始上电之后,先有一个200us的延时。

比如驱动时钟频率为100MHz,则INIT_PRE = 20000;

比如驱动时钟频率为133MHz,则INIT_PRE = 26600;

//==================================================

(3) 预刷新计数的宏定义

存储器上面的手册的信息是64ms必须完成所有逻辑单元的更新,主要是希望保证SDRAM数据不丢失的前提下,尽可能提高SDRAM的有效带宽,因此设置64ms为刷新间隔上限。

行刷新周期时间 = 64ms / 每个bank的行数.

例如,如果有4096行,则行刷新周期为 64ms / 4096 = 15.625us。

例如,如果有8192行,则行刷新周期为 64ms / 8192 = 7.8125us。

所以REF_PER = 15.625us / (1000/CLK) =15.625 x 10^3 ns / (1000/CLK) = 15.625 x CLK (对应有4096行)

REF_PER = 7.8125us / (1000/CLK) =7.8125 x 10^3 ns / (1000/CLK) = 7.8125x CLK (对应有8192行)

只要至少在预刷新的时间内刷新一次即可,若是有小数部分,可以取最大的整数,忽略小数部分,取最大的整数。

如4096行采用100MHz 时钟频率进行驱动,则15.625 x 100 = 1562/1563均可。

//==================================================

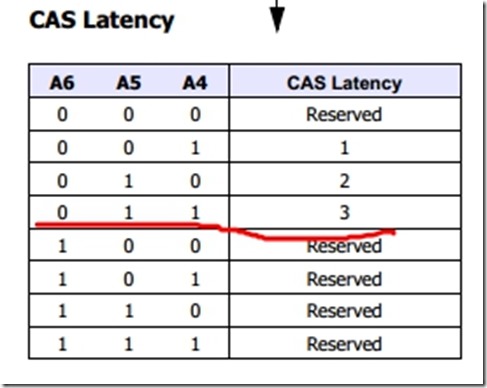

(4) SC_CL潜伏期延时的宏定义

SC_CL为SDRAM列选通命令的潜伏期延时设定,手册规定为2或者3;潜伏期的延时大小直接关系到SDRAM的最高运行速率,因此一般选择3。

定义SC_CL的宏后,会映射到SDR_CL的宏上,这个直接关系到最终的潜伏期选择,

parameter SDR_CL = (SC_CL == 2)? 3’b10 : 3’b11;

//==================================================

(5) SC_RCD数据读取延时定义

保持默认值3

//==================================================

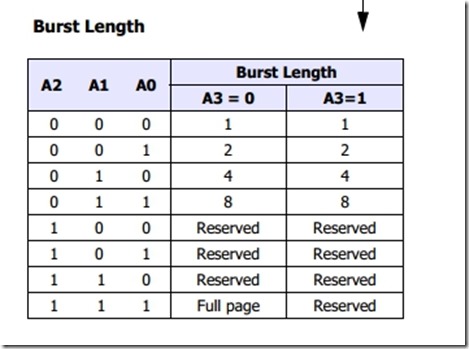

(6) SC_PM突发长度命令宏定义

这里采用了全页突发读/写操作,因此直接设置为A2A1A0 = 1 1 1;

为了便于其他模式修改:通过宏定义选择突发读写长度:

parameter SC_BL = 1;

//SDRAM parameter

parameter SDR_BL = (SC_PM == 1)? 3’b111: //page 256

(SC_BL == 1)? 3’b000: //1

(SC_BL == 2)? 3’b001: //2

(SC_BL == 4)? 3’b010: //4

3’b011; //8

//==================================================

(7) 突发顺序/交错读/写宏定义

一般在视频流的操作中采用顺序读/写,这里的宏定义如下:

parameter SDR_BT = 1’b0 ; // 顺序读/写 A3 = 0

// 1’b1; // 交错读/写 A3 = 1;

以上就是所有SDRAM所需要设定的参数。

//==================================================

//下面是terasic 公司的SDRAM参数设置。

// Address Space Parameters

`define ROWSTART 8

`define ROWSIZE 12

`define COLSTART 0

`define COLSIZE 8

`define BANKSTART 20

`define BANKSIZE 2

// Address and Data Bus Sizes

`define ASIZE 23 // total address width of the SDRAM

`define DSIZE 16 // Width of data bus to SDRAMS

//parameter INIT_PER = 100; // For Simulation

// Controller Parameter

//////////// 133 MHz ///////////////

/*

parameter INIT_PER = 32000;

parameter REF_PER = 1536;

parameter SC_CL = 3;

parameter SC_RCD = 3;

parameter SC_RRD = 7;

parameter SC_PM = 1;

parameter SC_BL = 1;

*/

///////////////////////////////////////

//////////// 100 MHz ///////////////

parameter INIT_PER = 24000;

parameter REF_PER = 1024;

parameter SC_CL = 3;

parameter SC_RCD = 3;

parameter SC_RRD = 7;

parameter SC_PM = 1;

parameter SC_BL = 1;

///////////////////////////////////////

//////////// 50 MHz ///////////////

/*

parameter INIT_PER = 12000;

parameter REF_PER = 512;

parameter SC_CL = 3;

parameter SC_RCD = 3;

parameter SC_RRD = 7;

parameter SC_PM = 1;

parameter SC_BL = 1;

*/

///////////////////////////////////////

// SDRAM Parameter

parameter SDR_BL = (SC_PM == 1)? 3'b111 :

(SC_BL == 1)? 3'b000 :

(SC_BL == 2)? 3'b001 :

(SC_BL == 4)? 3'b010 :

3'b011 ;

parameter SDR_BT = 1'b0; // Sequential

// 1'b1: // Interteave

parameter SDR_CL = (SC_CL == 2)? 3'b10:3'b11;

//=======================================

//优化上述各参数如下所示:

// Address and Data Bus Sizes

//(1M * 4) * 16Bit =(4096 * 256) * 4 * 16Bit = 64MBit

`define ROWSIZE 12 //Rows width in one bank

`define COLSIZE 8 //Column width in one bank

`define DSIZE 16 //16Bit SDRAM data

`define BANKSIZE 2 //4 Banks in one SDRAM

`define ASIZE `COLSIZE + `ROWSIZE + `BANKSIZE //SDRAM Total address

// Address Space Parameters -> The new code addres: {Bank, Row, Column}

`define COLSTART 0

`define ROWSTART `COLSIZE

`define BANKSTART `COLSIZE + `ROWSIZE

//上述将rowstart和bankstart进行了参数化,只需修改有限几个参数即可。

//---------------------------------------

//SDRAM Init paramter setting

//`define ROW4096_133MHz

//`define ROW4096_125MHz

`define ROW4096_100MHz

//`define ROW8192_133MHz

//`define ROW8192_125MHz

//`define ROW8192_100MHz

//利用命令`define…….`ifdef …….`endif 结构来实现对模式的选择,可以方便的修改。

`ifdef ROW4096_133MHz

// Controller Parameter for 4096 Rows @ 133MHz

parameter INIT_PER = 16'd26600; //200 * 133

parameter REF_PER = 16'd2078; //15.625*133 = 2078.125

parameter SC_CL = 3;

parameter SC_RCD = 3;

parameter SC_PM = 1;

parameter SC_BL = 1;

`endif

`ifdef ROW4096_125MHz

// Controller Parameter for 4096 Rows @ 125MHz

parameter INIT_PER = 16'd25000; //200 * 125

parameter REF_PER = 16'd1953; //15.625*125 = 1953.125

parameter SC_CL = 3;

parameter SC_RCD = 3;

parameter SC_PM = 1;

parameter SC_BL = 1;

`endif

`ifdef ROW4096_100MHz

// Controller Parameter for 4096 Rows @ 100MHz

parameter INIT_PER = 16'd20000; //200 * 100

parameter REF_PER = 16'd1562; //15.625*100 = 1562.5

parameter SC_CL = 3;

parameter SC_RCD = 3;

parameter SC_PM = 1;

parameter SC_BL = 1;

`endif

`ifdef ROW8192_133MHz

// Controller Parameter for 8192 Rows @ 133MHz

parameter INIT_PER = 16'd26600; //200 * 133

parameter REF_PER = 16'd1039; //7.8125*133 = 1039.0625;

parameter SC_CL = 3;

parameter SC_RCD = 3;

parameter SC_PM = 1;

parameter SC_BL = 1;

`endif

`ifdef ROW8192_125MHz

// Controller Parameter for 8192 Rows @ 125MHz

parameter INIT_PER = 16'd25000; //200 * 125

parameter REF_PER = 16'd976; //7.8125*125 = 976.5625

parameter SC_CL = 3;

parameter SC_RCD = 3;

parameter SC_PM = 1;

parameter SC_BL = 1;

`endif

`ifdef ROW8192_100MHz

// Controller Parameter for 8192 Rows @ 100MHz

parameter INIT_PER = 16'd20000; //200 * 100

parameter REF_PER = 16'd781; //7.8125*100 = 781.25

parameter SC_CL = 3;

parameter SC_RCD = 3;

parameter SC_PM = 1;

parameter SC_BL = 1;

`endif

//-----------------------------------------------------------

// SDRAM Parameter

parameter SDR_BL = (SC_PM == 1)? 3'b111 : //Page 256

(SC_BL == 1)? 3'b000 : //1

(SC_BL == 2)? 3'b001 : //2

(SC_BL == 4)? 3'b010 : //4

3'b011 ; //8

parameter SDR_BT = 1'b0; // Sequential

// 1'b1: // Interteave

parameter SDR_CL = (SC_CL == 2)? 3'b10:

3'b11;

上述就定义完成了SDRAM初始化以及模式配置所需要的各寄存器参数,上述的配置正确与否直接决定了输出的数据和运行速率。

//=======================================================================

更多详细的资料下载可以登录笔者百度网盘:

网址:http://pan.baidu.com/s/1bnwLaqF

密码:fgtb

//=======================================================================

相关文章推荐

- 原始js调用 选中事件

- 按enter 进行搜索 enter提交表单

- 程序员:如何接手垃圾代码?

- 关于WEB Service&WCF&WebApi实现身份验证之WebApi篇

- 验证码

- js模拟键盘或遥控器操作(加强版)

- CI框架学习总结

- == 和 eqalus() 的区别

- 十、WorldWindJava+自定义渲染类

- SSH关于公钥认证Permission denied (publickey……的问题

- java中的各种数据类型在内存中存储的方式

- PHP之Phalcon支持(安装与配置)

- TP 学习之 session 方法的学习

- 序列化的概念以及分类

- C++移位运算符详解

- ArrayList用法

- 手动ecache处理

- I.MX6 默认打开 USB adb

- phpstorm使用教程

- 92、QOS区分式服务配置实验之分类&标记