PowerPC MMU机制读书笔记

2016-01-14 20:01

519 查看

PowerPC mmu编程模型读书笔记

通常,地址转换是通过段寄存器(SR)和页表进行内存映射的。段信息将有效地址转换为一个临时的虚拟地址,而页表把虚拟地址转换为实际物理地址。

地址转换缓存TLB是用来保存最近使用的页的地址的。虽然他们的特性不是由操作系统环境里指定,但是通常来讲他们还是和操作系统的软件环境有关。

段信息存在SR寄存器里。块地址转换(BAT)基址一个软件控制的数组,他们存的是块地址,块可以看做是连续的许多页。BAT数据的入口存在了几对BAT寄存器中,他们都是SPR。

部分MMU的信息还和MSR寄存器里面的某几位值有关。

有个术语叫需求页(demand page),意思是页面只有在他们被程序执行过程中用到的时才从外存(硬盘)加载到内存中去。

有效地址按256M进行分段(segments),或者按照128K-256M分块(blocks)。段再细分成很多(4K大小的)页面。每一个段或者页面都有一个操作系统产生的地址描述符(descriptor,一般作为page table entry (PTE) or BAT array entry)。

除了第四个放页表,其他的都是固定的地址,具体的起始位置由MSR[IP]位决定。

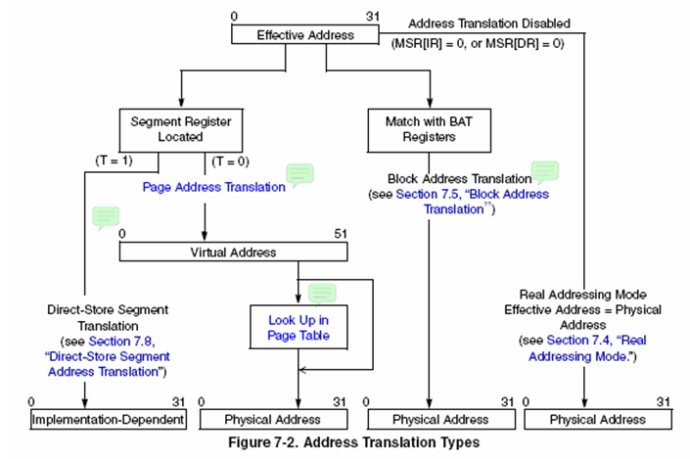

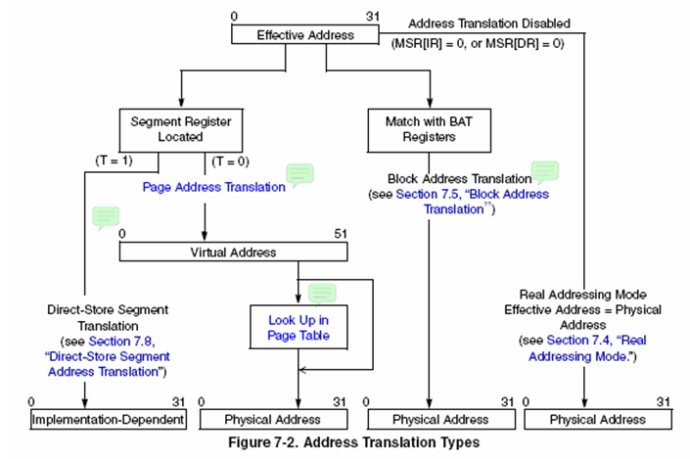

从图上能看出来的是两个流程:

1. 通过SRs,TLB,页表查询逻辑得到PA

2. 根据BAT得到PA

顺序和优先级的的话这个图里可能还看不出来,接下去看。

• Page address translation—translates the page frame address for a4-Kbyte page size

• Block address translation—translates the block number for blocksthat range from 128 Kbytes to

256 Mbytes

• Real addressing mode address translation—when address translationis disabled, the physical

address is identical to the effectiveaddress.

支持下面三种地址转换模式:

l 页地址转换,转换4K大小的页框地址。

l 块地址转换,转换大小为128K-256M的块的块号。

l 实地址模式,就是没有地址转换,物理地址和有效地址一致。

这一节有提到,If an effective address matches the correspondingBAT register field, the information in the BAT register is used to generate thephysical address; in this case, the results of the page translation (occurringin parallel) are ignored. Note that a matching

BAT array entry always takesprecedence over a translation provided by the SR (even if the segment is adirect-store segment).也就是说,有效地址的转换是并行的,如果找BAT寄存器能转成物理地址,那么并行的SR的线就会被忽略,匹配BAT数组的入口总是发生在SR提供的转换前,BAT的优先级高于SR。

MSR[IR]和MSR[DR]是否置为0决定了相关的指令地址转换或者数据地址转换是不是实地址模式(也就是没有地址转换)。

MMU提供8种保护选项。

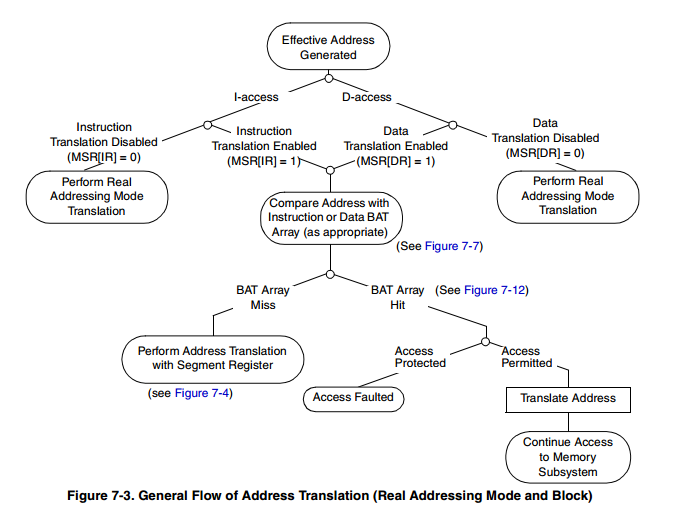

总流程图

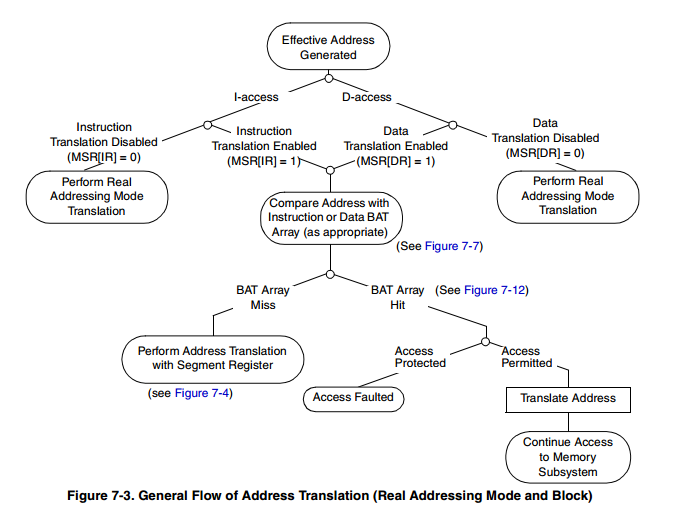

BAT方式转换流程图

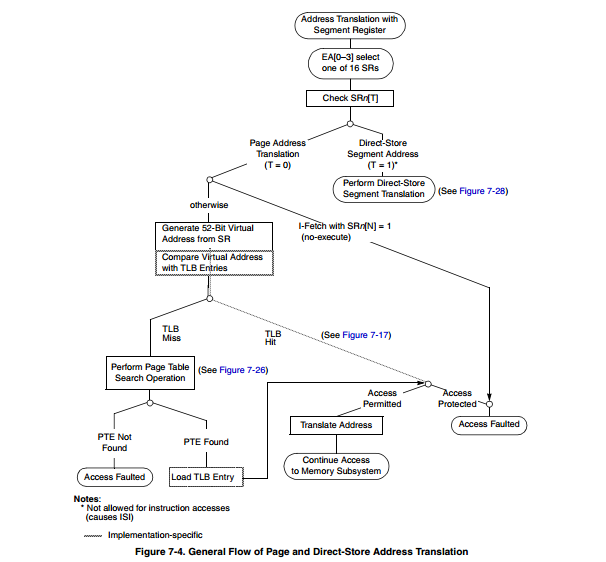

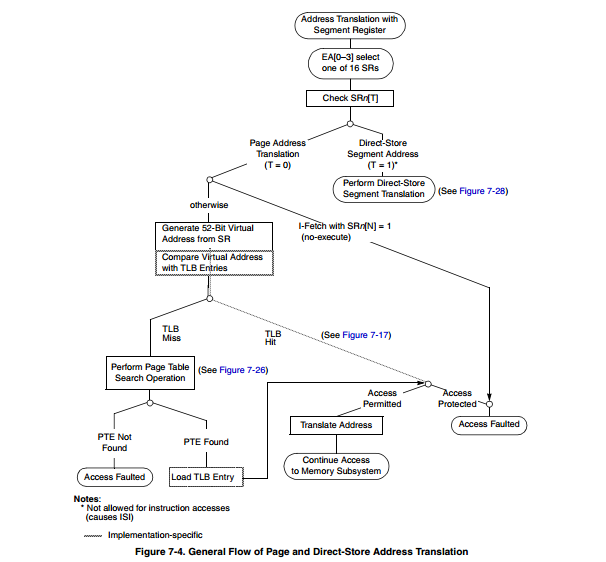

SR-》查页表(hash表)的方式流程图

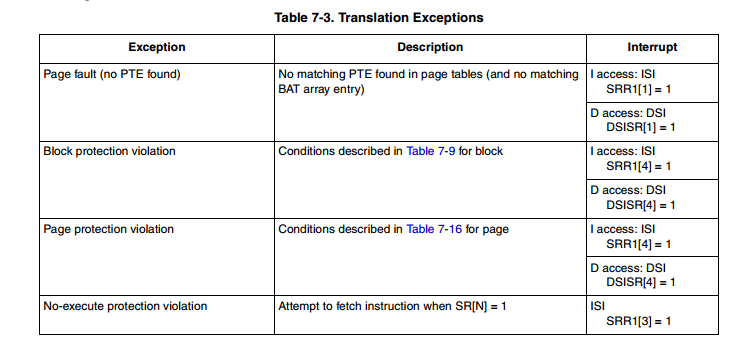

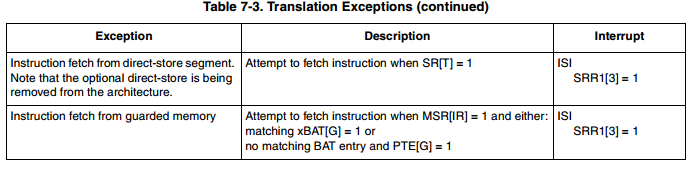

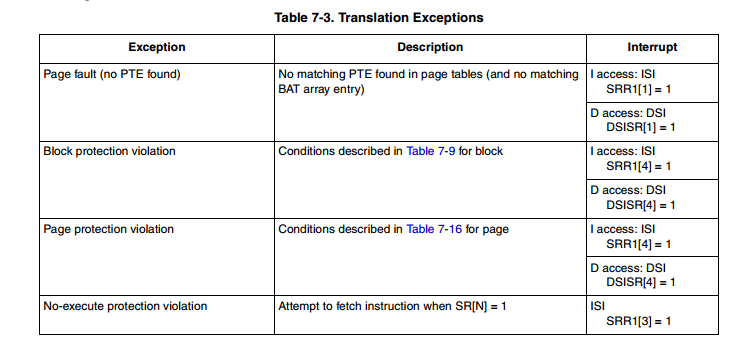

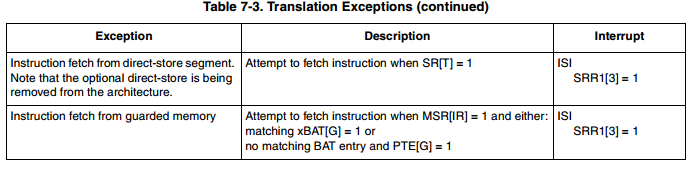

会导致地址转换异常(translation exception)的原因有:

l There is no valid entry in the page table for the page specified bythe effective address (and SR) and there is no valid BAT translation.(页表查询失败同时BAT转换失败)

l There is no valid SR and there is no valid BATtranslation.(SR查询失败同时BAT查询失败)

l An address translation is found but the accessis not allowed by the memory protection mechanism.(转换有效但是存取被内存保护地址阻止)

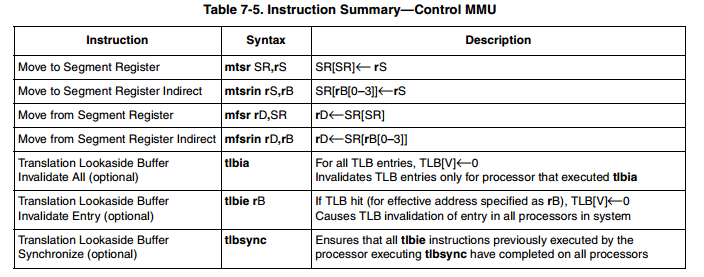

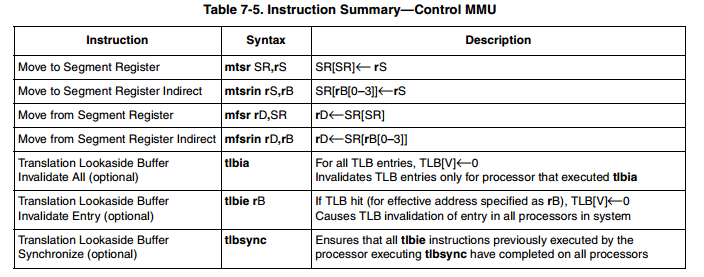

涉及到的指令如上表。这里注意一下mtsr这条指令,他的SR这里是一个数,不是一个寄存器。在写汇编的过程中之前给SR赋值的汇编函数里用的是mtsr R3,R4 的方式(R3,R4都是参数),之前以为因为R3,R4都是参数,所以会正确。但是因为宏定义里面R3其实就是3,所以在这里相当于不断的给SR[3]在赋值,而不是在给SR[R3]赋值……实际应该用mtsrin这条指令。

所以看汇编指令的时候一定要注意,他的描述里面是[Register]还是[数]。

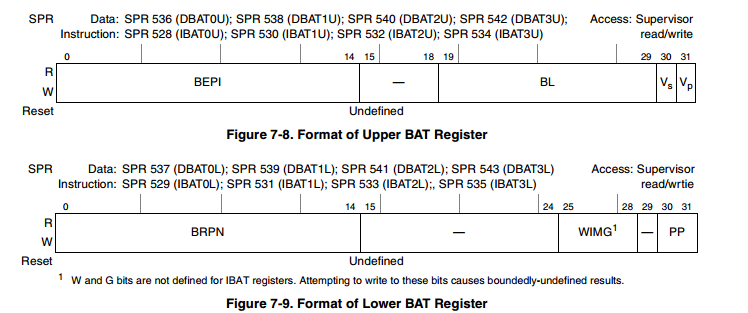

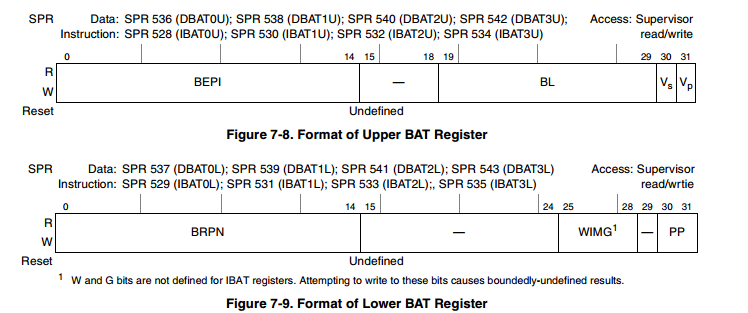

BAT的upper寄存器和lower寄存器格式如下:

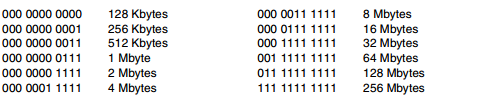

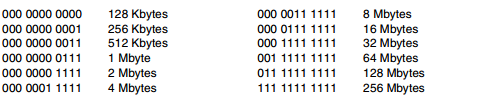

块大小和块起始地址由BL和BRPN定义。BEPI用来做匹配。Vs和Vp决定工作模式,当MSR[PR]=0看Vs是否为1决定是否为supervisor mode,MSR[PR]=1,看Vp是否为1决定是否为User Mode. BL决定的长度如下:

WIMG的含义:

Memory/cache access mode bits

W Write-through

I Caching-inhibited

M Memory coherence

G Guarded

但是其实在IBAT只能改IM,WG的修改可能会导致边界没有定义(boundedly-undefined)结果。

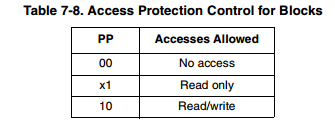

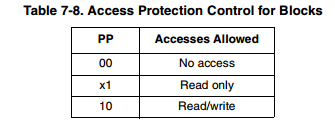

PP位用来进行判定块内存的保护:

For data accesses, a DSI is generated andDSISR[4] is set.

For instruction accesses, an ISI is generatedand SRR1[4] is set.

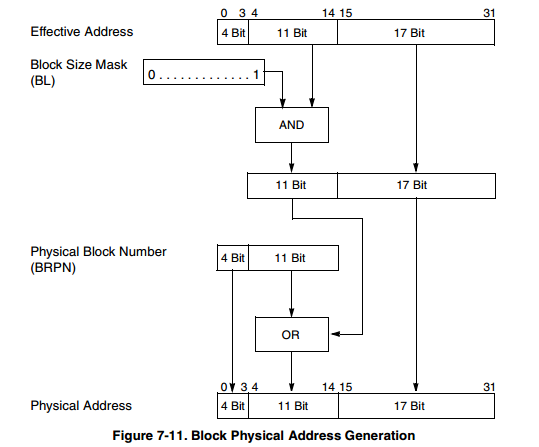

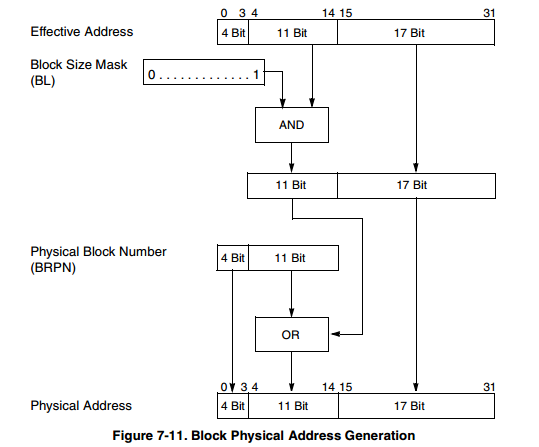

物理地址的产生:

首先和BEPI比较,然后:

PA ={BRPN[0:3],BRPN[4:14]|((EA[4:14])&BL),EA[15:31]} (逗号表示连接)

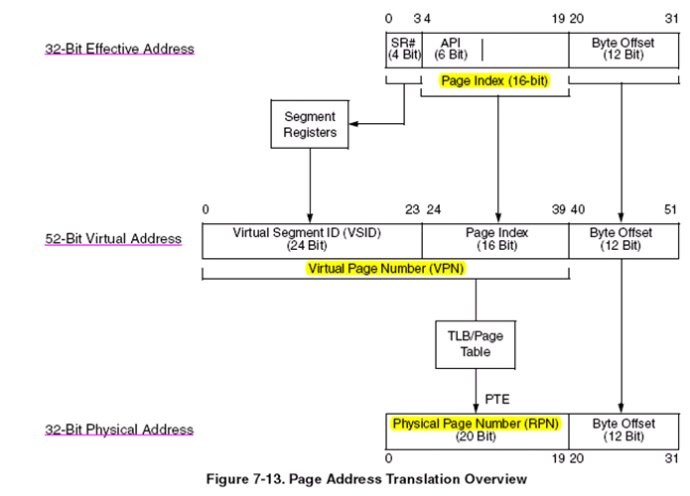

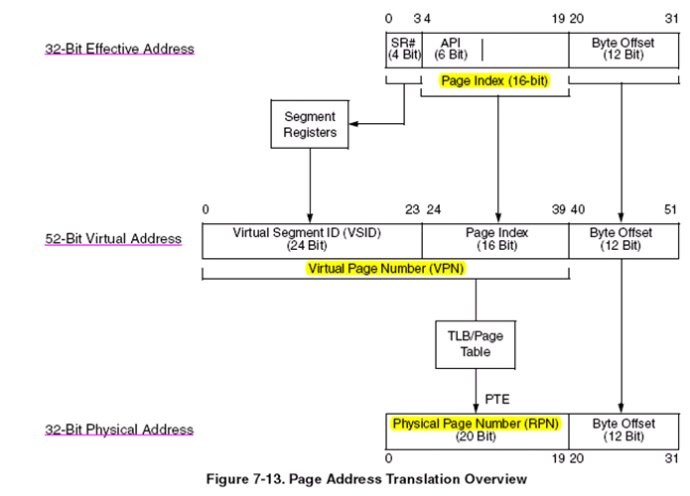

项目实际过程中是不需要52位虚拟地址的,所以SRn里面的VSID就是n,这样就能保证EA得到的VSID和他的前4位是一样的值,这样,EA就等于VA了。

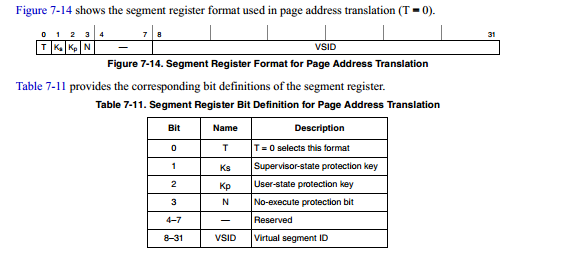

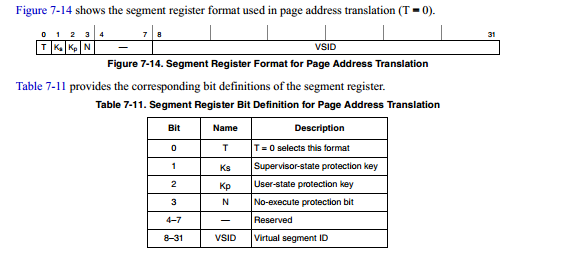

SR寄存器组成:

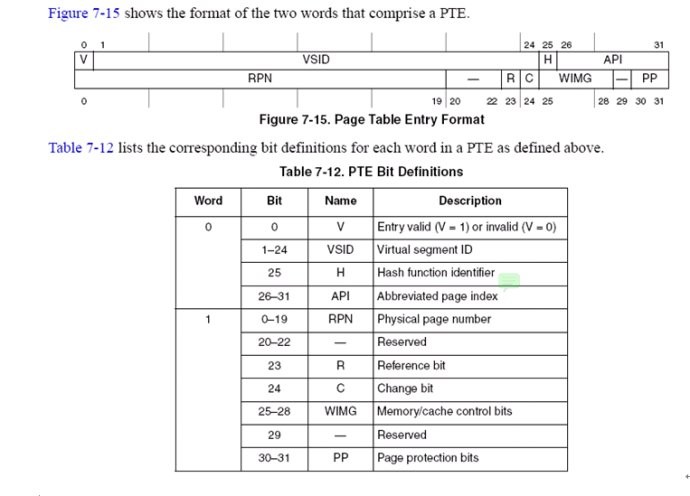

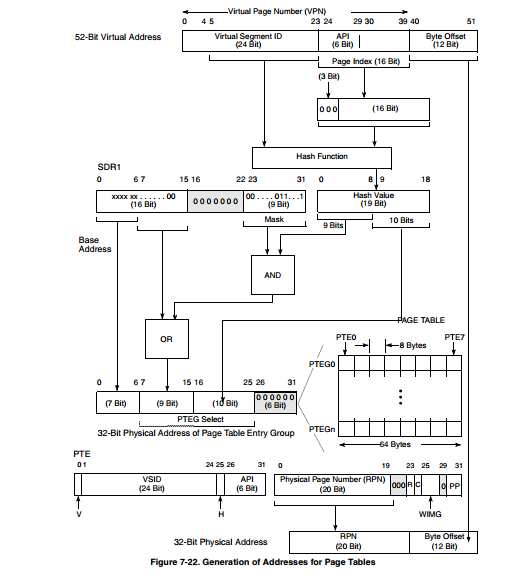

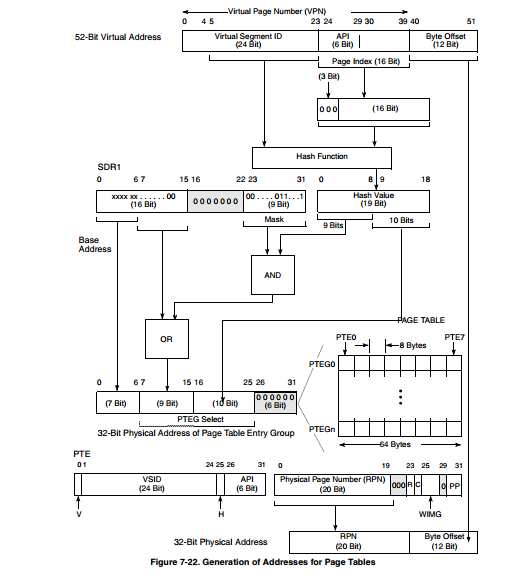

这里借鉴一下别人的总结:由52位的虚拟地址VA转化成32位的物理地址

这一步骤比较复杂,本步骤也分为三个小步:

第一个小步:先由52位的虚拟地址(VA)找到页表项组(PTEGs)的地址;

第二个小步:再从页表项组(PTEGs)中逐个查找,从而找到页表项(PTE)的地址;

第三个小步:最后从PTE中取出RPN和和字节偏移地址(Byte Offset)拼接,构成32位的物理地址,具体过程如下:

由52位的虚拟地址VA找到页表项组(PTEGs)的地址

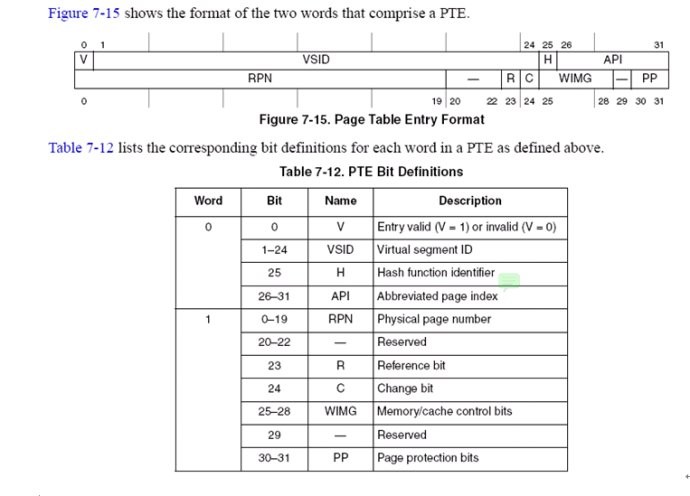

解释一下,PowerPC构架中的页表由页表项组(PTEGs)构成的,而每个PTEGs又是由PTE构成的,每个PTE有8个字节。

由hash表查找PTE的过程:

结合本项目实际来看的话:

PowerPC750(可能其他的PowerPC也是这样)指定的方式是必须存在一张hash表,找物理地址也是用hash表里的PTE,因此PTEs实际用的时候其实是用存放在hash表里面的,跟我们单纯理解的PTEs存放在二级页表里面的方式还不太一样(但是缺页中断填充hash表的PTEs却又来自于两级页表)

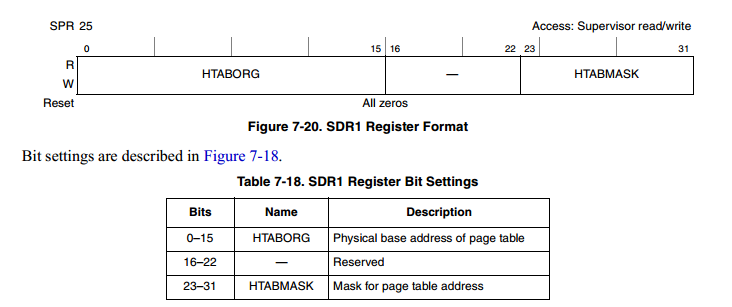

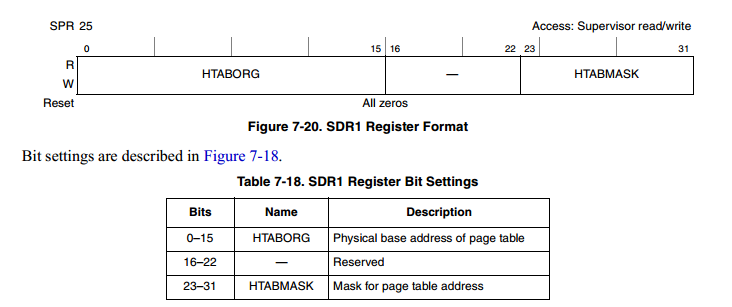

上图中有个SDR1寄存器,他是用来指示PTEGs的地址的,PTEG就是存放PTEs的组,一个组存放8个PTE,每个PTE的大小是8Bytes。通过Hash函数选中PTEG,然后根据API选择具体的某个PTE。PTE形象点结构如下:

一个SDR1的寄存器的组织结构如下:

注意虽然0-15位都是指示地址的,但是有可能不会全部用到,要由HTABMASK(这个到时候会和hash函数得到的值,也就是主哈希和次哈希进行按位与运算)决定,具体如下:

这里有个规定,一般来讲hash表里面的PTEGs的个数,不能小于物理内存页框数的一半。因为hash表太小的话,冲突的概率太大了。

这里还有个值得注意的地方就是:当一个中断产生的时候,MMU会自动关闭,如果你在中断处理的过程中保存上下文的栈是建立在虚拟地址空间内的话,那么要在保存上下文之前手动打开一下MMU。

其他的问题,暂时就还没有了。以后有MMU的问题,会继续添加在这个之后。

1概览

PowerPC中的地址分为三类:有效地址EA,是在代码和指令里面使用的;虚拟地址VA,可以看成是中间的转换地址;物理地址PA,实际的真正的内存中的地址。通常,地址转换是通过段寄存器(SR)和页表进行内存映射的。段信息将有效地址转换为一个临时的虚拟地址,而页表把虚拟地址转换为实际物理地址。

地址转换缓存TLB是用来保存最近使用的页的地址的。虽然他们的特性不是由操作系统环境里指定,但是通常来讲他们还是和操作系统的软件环境有关。

段信息存在SR寄存器里。块地址转换(BAT)基址一个软件控制的数组,他们存的是块地址,块可以看做是连续的许多页。BAT数据的入口存在了几对BAT寄存器中,他们都是SPR。

部分MMU的信息还和MSR寄存器里面的某几位值有关。

有个术语叫需求页(demand page),意思是页面只有在他们被程序执行过程中用到的时才从外存(硬盘)加载到内存中去。

2MMU概览

4G有效地址空间,52位的虚拟地址长度(可能在实际编程的时候不用这么多),最多32位的实际地址长度。有效地址按256M进行分段(segments),或者按照128K-256M分块(blocks)。段再细分成很多(4K大小的)页面。每一个段或者页面都有一个操作系统产生的地址描述符(descriptor,一般作为page table entry (PTE) or BAT array entry)。

3内存编址

一个程序在执行load,store,branch或者缓存指令和取下一条指令时,用的内存地址是处理器计算出的逻辑地址(有效地址,EA)。EA会根据这章所讲的过程,转换成一个物理地址,然后内存子系统使用这个物理地址进行存取。3.1 预定义物理内存位置(直译)

有四个物理内存映射使用是预先定义好的。如下表

除了第四个放页表,其他的都是固定的地址,具体的起始位置由MSR[IP]位决定。

3.2 MMU组织结构

从图上能看出来的是两个流程:

1. 通过SRs,TLB,页表查询逻辑得到PA

2. 根据BAT得到PA

顺序和优先级的的话这个图里可能还看不出来,接下去看。

3.3 地址转换机制

The following types of address translationare supported:• Page address translation—translates the page frame address for a4-Kbyte page size

• Block address translation—translates the block number for blocksthat range from 128 Kbytes to

256 Mbytes

• Real addressing mode address translation—when address translationis disabled, the physical

address is identical to the effectiveaddress.

支持下面三种地址转换模式:

l 页地址转换,转换4K大小的页框地址。

l 块地址转换,转换大小为128K-256M的块的块号。

l 实地址模式,就是没有地址转换,物理地址和有效地址一致。

这一节有提到,If an effective address matches the correspondingBAT register field, the information in the BAT register is used to generate thephysical address; in this case, the results of the page translation (occurringin parallel) are ignored. Note that a matching

BAT array entry always takesprecedence over a translation provided by the SR (even if the segment is adirect-store segment).也就是说,有效地址的转换是并行的,如果找BAT寄存器能转成物理地址,那么并行的SR的线就会被忽略,匹配BAT数组的入口总是发生在SR提供的转换前,BAT的优先级高于SR。

MSR[IR]和MSR[DR]是否置为0决定了相关的指令地址转换或者数据地址转换是不是实地址模式(也就是没有地址转换)。

3.4 内存保护工具

MMU提供8种保护选项。

3.5 页历史信息

让操作系统可以换页到内存的时候把哪页写回到硬盘中。3.6 MMU地址转换流程

总流程图

BAT方式转换流程图

SR-》查页表(hash表)的方式流程图

会导致地址转换异常(translation exception)的原因有:

l There is no valid entry in the page table for the page specified bythe effective address (and SR) and there is no valid BAT translation.(页表查询失败同时BAT转换失败)

l There is no valid SR and there is no valid BATtranslation.(SR查询失败同时BAT查询失败)

l An address translation is found but the accessis not allowed by the memory protection mechanism.(转换有效但是存取被内存保护地址阻止)

3.7 MMU控制相关指令

涉及到的指令如上表。这里注意一下mtsr这条指令,他的SR这里是一个数,不是一个寄存器。在写汇编的过程中之前给SR赋值的汇编函数里用的是mtsr R3,R4 的方式(R3,R4都是参数),之前以为因为R3,R4都是参数,所以会正确。但是因为宏定义里面R3其实就是3,所以在这里相当于不断的给SR[3]在赋值,而不是在给SR[R3]赋值……实际应该用mtsrin这条指令。

所以看汇编指令的时候一定要注意,他的描述里面是[Register]还是[数]。

3.8 BAT映射相关

打开BAT的先决条件是MSR[IR] and/or MSR[DR]=1;BAT映射优先级高于SR寄存器查找的方式。BAT的upper寄存器和lower寄存器格式如下:

块大小和块起始地址由BL和BRPN定义。BEPI用来做匹配。Vs和Vp决定工作模式,当MSR[PR]=0看Vs是否为1决定是否为supervisor mode,MSR[PR]=1,看Vp是否为1决定是否为User Mode. BL决定的长度如下:

WIMG的含义:

Memory/cache access mode bits

W Write-through

I Caching-inhibited

M Memory coherence

G Guarded

但是其实在IBAT只能改IM,WG的修改可能会导致边界没有定义(boundedly-undefined)结果。

PP位用来进行判定块内存的保护:

For data accesses, a DSI is generated andDSISR[4] is set.

For instruction accesses, an ISI is generatedand SRR1[4] is set.

物理地址的产生:

首先和BEPI比较,然后:

PA ={BRPN[0:3],BRPN[4:14]|((EA[4:14])&BL),EA[15:31]} (逗号表示连接)

3.9 段模式映射相关

盗图一张:

项目实际过程中是不需要52位虚拟地址的,所以SRn里面的VSID就是n,这样就能保证EA得到的VSID和他的前4位是一样的值,这样,EA就等于VA了。

SR寄存器组成:

这里借鉴一下别人的总结:由52位的虚拟地址VA转化成32位的物理地址

这一步骤比较复杂,本步骤也分为三个小步:

第一个小步:先由52位的虚拟地址(VA)找到页表项组(PTEGs)的地址;

第二个小步:再从页表项组(PTEGs)中逐个查找,从而找到页表项(PTE)的地址;

第三个小步:最后从PTE中取出RPN和和字节偏移地址(Byte Offset)拼接,构成32位的物理地址,具体过程如下:

由52位的虚拟地址VA找到页表项组(PTEGs)的地址

解释一下,PowerPC构架中的页表由页表项组(PTEGs)构成的,而每个PTEGs又是由PTE构成的,每个PTE有8个字节。

由hash表查找PTE的过程:

结合本项目实际来看的话:

PowerPC750(可能其他的PowerPC也是这样)指定的方式是必须存在一张hash表,找物理地址也是用hash表里的PTE,因此PTEs实际用的时候其实是用存放在hash表里面的,跟我们单纯理解的PTEs存放在二级页表里面的方式还不太一样(但是缺页中断填充hash表的PTEs却又来自于两级页表)

上图中有个SDR1寄存器,他是用来指示PTEGs的地址的,PTEG就是存放PTEs的组,一个组存放8个PTE,每个PTE的大小是8Bytes。通过Hash函数选中PTEG,然后根据API选择具体的某个PTE。PTE形象点结构如下:

一个SDR1的寄存器的组织结构如下:

注意虽然0-15位都是指示地址的,但是有可能不会全部用到,要由HTABMASK(这个到时候会和hash函数得到的值,也就是主哈希和次哈希进行按位与运算)决定,具体如下:

这里有个规定,一般来讲hash表里面的PTEGs的个数,不能小于物理内存页框数的一半。因为hash表太小的话,冲突的概率太大了。

这里还有个值得注意的地方就是:当一个中断产生的时候,MMU会自动关闭,如果你在中断处理的过程中保存上下文的栈是建立在虚拟地址空间内的话,那么要在保存上下文之前手动打开一下MMU。

其他的问题,暂时就还没有了。以后有MMU的问题,会继续添加在这个之后。

相关文章推荐

- 常用第三方库

- html5 canvas 画布基础

- 如何让一张图片填满整个页面

- 透过OOP-Klass模型来看实例变量与类变量的存储

- 如何使rdlc报表的表头在每一页都显示

- 重磅!从单层感知器到深度学习以及深度学习必知的框架

- C++预定义字符函数

- JAVA开发中遇到的jdk配置正确但是tomcat服务器启动时一闪而过

- Node.js 搭建mqttServer 及 mqttClient

- Windows下Redis的安装使用

- android初接触之activity2

- [转载]项目风险管理七种武器-长生剑

- php 数组操作

- Cookie/Session机制详解

- CXF bus interceptor配置

- Tomcat 配置 HTTPS双向认证

- 限制SSH访问源,禁止4A之外的地址跳转访问

- 网线水晶头接法

- 在scroll下面固定Button的方法

- Linux下媒体文件播放问题