[原创][FPGA]时钟分频之奇分频(5分频)

2015-12-10 14:42

232 查看

0. 简介

有时在基本模块的设计中常常会使用到时钟分频,时钟的偶分频相对与奇分频比较简单,但是奇分频的理念想透彻后也是十分简单的,这里就把奇分频做一个记录。1. 奇分频

其实现很简单,主要为使用两个计数模块分别计数,得到两个波形进行基本与或操作完成。直接贴出代码部分如下。module div_freq( iCLK, iRST_n, oCLK ); input wire iCLK; input wire iRST_n; output oCLK; parameter N = 4'd5; reg clk_p; reg [3:0] cnt_p; always @ (posedge iCLK or negedge iRST_n) begin if (!iRST_n) cnt_p <= 4'd0; else if (cnt_p == N - 1) cnt_p <= 4'd0; else cnt_p <= cnt_p + 1'b1; end always @ (posedge iCLK or negedge iRST_n) begin if (!iRST_n) clk_p <= 1'b0; else if (cnt_p == (N - 1) / 2) clk_p <= ~clk_p; else if (cnt_p == N - 1) clk_p <= ~clk_p; else clk_p <= clk_p; end reg clk_n; reg [3:0] cnt_n; always @ (negedge iCLK or negedge iRST_n) begin if (!iRST_n) cnt_n <= 4'd0; else if (cnt_n == N - 1) cnt_n <= 4'd0; else cnt_n <= cnt_n + 1'b1; end always @ (negedge iCLK or negedge iRST_n) begin if (!iRST_n) clk_n <= 1'b0; else if (cnt_n == (N - 1) / 2) clk_n <= ~clk_n; else if (cnt_n == N - 1) clk_n <= ~clk_n; else clk_n <= clk_n; end assign oCLK = clk_p | clk_n; endmodule

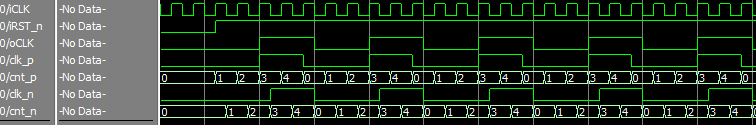

modelsim仿真结果如下图

相关文章推荐

- ThreadLocal理解

- credentials 中的validator和encoding

- 指定文件压缩并提交到SVN

- iOS中UITextField的字数限制

- 欢迎使用CSDN-markdown编辑器

- ntpclent

- Java---布局管理代码简单使用(解答)

- leetcode:206 Reverse Linked List-每日编程第十四题

- 递归与迭代的区别

- ios 设计模式

- Eclipse 未开始 【Ubuntu】

- 编译 Android 版本的 Opus 音频编解码库的方法

- wix xslt for adding node

- lucene 索引过程

- SDUT 数据结构实验之查找五:平方之哈希表

- ClassCastException: android.widget.ImageView cannot be cast to android.widget.TextView

- eclipse快捷键

- android绑定远程服务以及android接口定义语言(aidl)

- appcan 主窗口和frame窗口通信

- 关于返回Return的一些困惑:”for(){return;}是否退出循环?“