makefile简单多文件编译

2015-09-20 22:50

323 查看

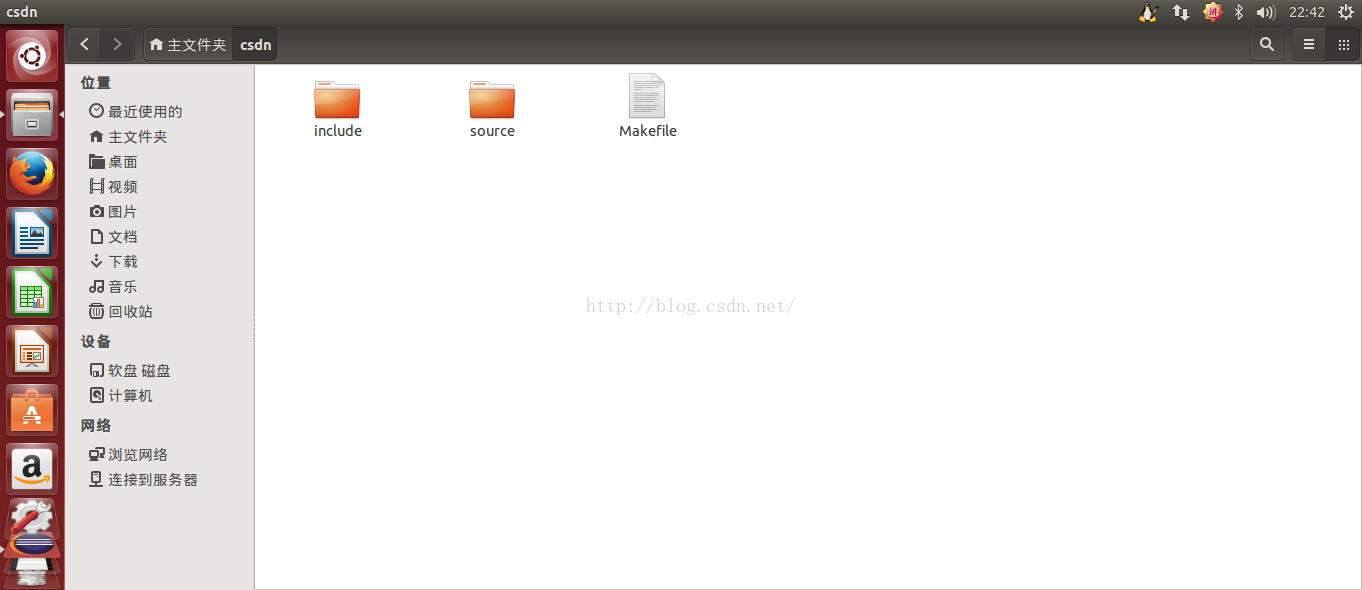

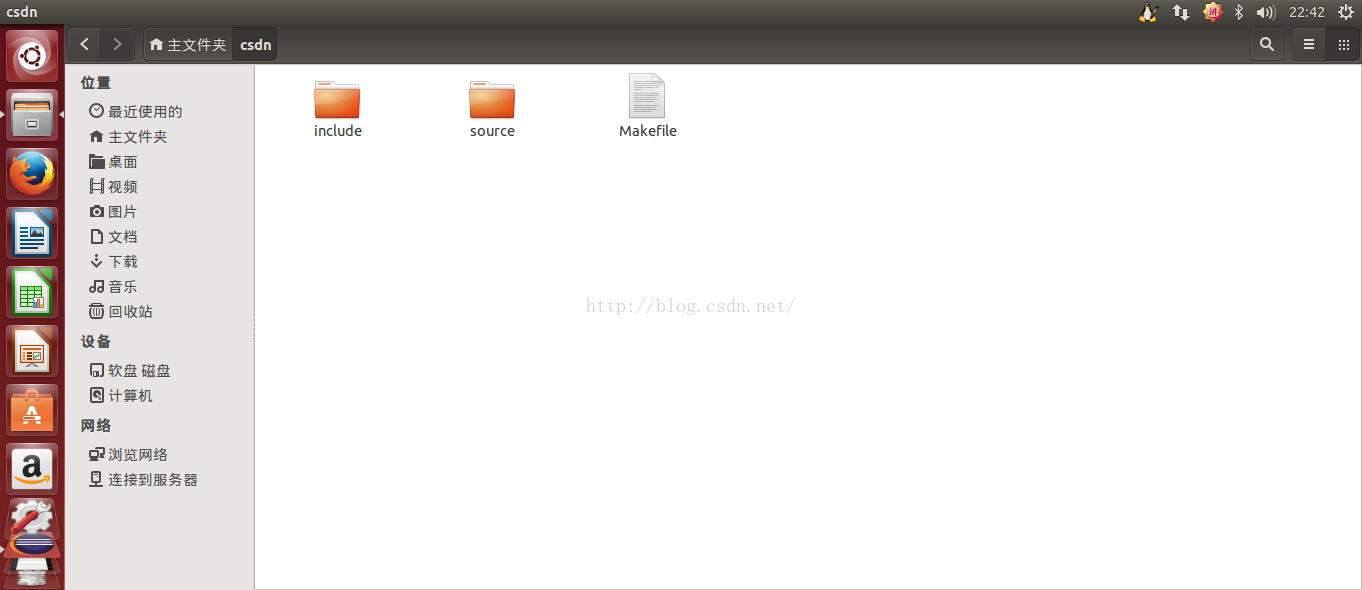

假设源文件和Makefile的存放如下图:

Makefile文件可以这样编写:

OBJS_DIR = obj

CPP_SRCS += $(wildcard source/*.cpp)

OBJS += $(patsubst %.cpp,${OBJS_DIR}/%.o,$(notdir ${CPP_SRCS}))

CPP_DEPS += $(patsubst %.cpp,${OBJS_DIR}/%.d,$(notdir ${CPP_SRCS}))

INCLUDE +=-I./include

# Each subdirectory must supply rules for building sources it contributes

${OBJS_DIR}/%.o: ./source/%.cpp

@echo 'Building file: $<'

@echo 'Invoking: GCC C++ Compiler'

g++ $(INCLUDE) -O0 -g3 -Wall -c -fmessage-length=0 -o "$@" "$<" -lpthread

@echo 'Finished building: $<'

@echo ' '

例子使用的是G++编译器,使用时替换为自己使用的编译器即可。

Makefile文件可以这样编写:

OBJS_DIR = obj

CPP_SRCS += $(wildcard source/*.cpp)

OBJS += $(patsubst %.cpp,${OBJS_DIR}/%.o,$(notdir ${CPP_SRCS}))

CPP_DEPS += $(patsubst %.cpp,${OBJS_DIR}/%.d,$(notdir ${CPP_SRCS}))

INCLUDE +=-I./include

# Each subdirectory must supply rules for building sources it contributes

${OBJS_DIR}/%.o: ./source/%.cpp

@echo 'Building file: $<'

@echo 'Invoking: GCC C++ Compiler'

g++ $(INCLUDE) -O0 -g3 -Wall -c -fmessage-length=0 -o "$@" "$<" -lpthread

@echo 'Finished building: $<'

@echo ' '

例子使用的是G++编译器,使用时替换为自己使用的编译器即可。

相关文章推荐

- Google chrome 安装包双击无任何反应

- android Flag启动模式

- Android 进程通信-- Binder机制

- HelloJSP!——内置对象编程题

- 树莓派B+上手小记--使用HDMI线连接显示器

- SpringMVC 自定义拦截器使用

- Java 加密算法

- 1_TwoSum

- Linux 高可用(HA)集群之keepalived 推荐

- 进程间通信IPC

- HDU 5464 Clarke and problem(DP 01背包)

- java超时跳出iframe框架

- WCF服务部署到IIS7.5

- Ros Navigation基础

- Tomcat源码分析-- 一次完整请求的里里外外

- Android--shape-指定图形的corners、gradient、padding、size、solid、stroke属性

- mantis的安装

- 深入理解Android View(转)

- 两道有趣的面试题(转)

- JVM 基础 VM运行机制