Digilent GENESYS vertex5开发板实现调用AC97(LM4550芯片)IP和LCD1602的使用

2012-08-15 19:04

761 查看

本文参考官方资料:– EDK Concepts, Tools, and Techniques http://www.xilinx.com/support/documentation/sw_manuals/edk_ctt.pdf

和http://www.digilentinc.com/Data/Products/GENESYS/Genesys_bsb_design.zip

以及http://www.digilentinc.com/Data/Products/GENESYS/Genesys_Ip_Cores.zip

最终实现效果:在Genesys开发板上实现语音的采集和播放,并由LCD1602和leds显示语音的状态,对语音的控制由方向按键实现。

使用环境:Xilinx ISE 11.4 (主要是用XPS和SDK)、Windows XP Professional SP3、Digilent GENESYS 开发板

具体过程:

一.搭建硬件平台:(这一步比较复杂)

1.使用XPS的BSB(Base System Builder)搭建单核系统(具体参见Genesys_bsb_design.zip),满足如下条件:

– Use 64KB BRAM (Look at Slide 17 in Genesys_BSB_Guide)

– Set “HARD_ETHERNET_MAC” to use DMA and Interrupt (Look at Slide 18 in Genesys_BSB_Guide)

– Set both UART core types to xps_uart16650 (Look at Slide 19 in Genesys_BSB_Guide)

– Enable both instruction and data cache memory (recommended)

2.加入所需要的IP。

(由于本来只打算使用AC97和LCD的IP,考虑到高低速外设总线分开,还需要一个PLB v4.6的IP,故就只加了这三个IP,但在后面的编译过程中遇到了解决不了的问题,因为对于新加入的PLBv4.6总线来说,还需要一个PLBV46 to PLBV46 Bridge 来与PLB总线连接,对于外围外设的管理,还需要一个EPC(External

Peripheral Control)和Utility Bus Split来完成最终的操作)

因此,除AC97外需要加入五个IP,如下图:(AC97的IP需要在创建BSB时就加入Genesys BSB support文件支持,或者在Project->Project Options->Project Peripheral Repository Search Path里面加入xxx\Digilent_Genesys_BSB_Support\lib这样的支持文件,才能引入官方编译好的AC97

IP)(该支持文件可以在官网下载到)

其中,加入General Purpose IP后将其改名为Char_LCD(如下图),加入PLBv4.6总线IP后将其改名为mb_plb_1(如下图),接下来更改PLB总线设置,如下图,将低速设备如Char_LCD、DIP_Switchs_8Bits、Leds_8Bits、Push_Button_7Bits、RS232_Uart_0、RS232_Uart_1连接到mb_plb_1,至于PLB

bridge其MPLB连接到mb_plb_1,SPLB连接到mb_plb,设置DDR2_SDRAM的参数如下图所示:

接下来对新加入的IP进行配置,首先配置DDR2_SDRAM,如下图,对其四个port进行设置

接下来配置Char_LCD,由于LCD1602有11个GPIO口通信(8位数据、两位读写控制位Wr、Rd,和一位数据命令选择位cd)所以数据位宽11位,如下图:

接下来生成新加入IP的地址,在Address选项卡里面点击Generate Address即可,如下图:

然后配置xps_epc,设置外设的数量,及各种相应时间,如下图:

配置util_bus_split_0 ,如下图:

3.设置IP的端口连接。

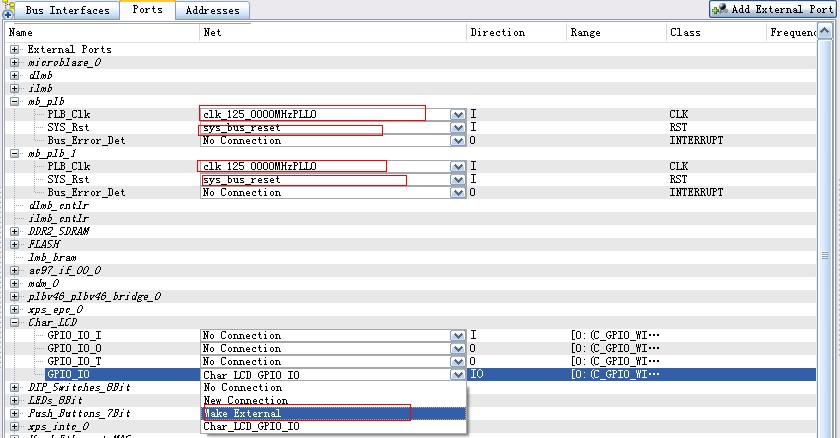

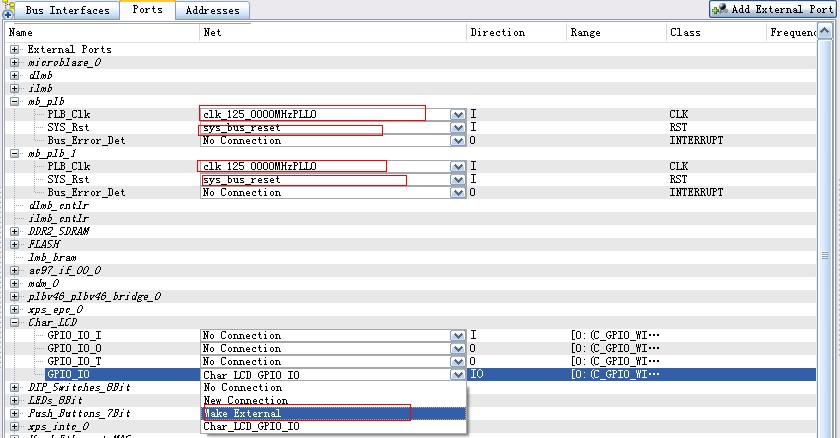

首先进入System Assembly View的Port视图:设置两个mb_plb总线的时钟和复位接口,在将Char_LCD的IO口使用Make external外扩出来(与实际的LCD1602连接),如下图:

接下来就会在External Ports里面看到外扩出来的Char_LCD_GPIO_IO,如下图:

用同样的方法,将xps_epc和ac97都外扩出来,如下图:

(外扩的时候,注意观察External Ports里面是不是都有对应的端口出现,有的时候会出现__NOC__(该ISE版本的bug,以后版本没有该问题),此时需要再在刚刚那个Make External的地方选择New Connection,就会出现对应名字的端口,手动将__NOC__的地方改为相应端口名即可)

其中,xps_epc_0的PRH_Addr的xps_epc_0_PRH_Addr_split是Make External后手动修改的名字

对应的External Ports截图如下:(其中xps_epc_0_PRH_Addr以及后面的xps_epc_0_PRH_Addr,[0:1]都是手动修改得到的)

然后修改程序复位时钟为25M,将总线分割的IP的端口手动连到刚刚手动改动的端口上,如下图

至此,外扩端口以及结束,然后添加用户约束文件(管脚约束),复制下载到的Genesys_ip_cores_UCF_SDK /data/Genesys_ip_cores.ucf里面的与相应IP相连的管脚到Project视图里面的UCF File Data/system.ucf里面即可。

编译:“Hardware->Generate Bitstream” 30~60 分钟

“Software->“Generate Libraries and BSPs” “ Build All User Applications”

“Device Configuration” -> “Download Bitstream” 下载后可以从开发板的串口看到测试程序的输入信息(串口:9600,8,n,1)

二.在SDK里面实现具体用户应用程序。

“Project” -> “Export Hardware Design to SDK” 选择Export and Launch SDK

对于出现的“Workspace Launcher”对话框,输入当前所创建的工程文件夹下面的SDK文件夹的路径,如果没有出现该对话框,可用“File” -> “Switch Workspace”更改当前路径。

之后,SDK会自动搜索Hardware Specification File,如果提示未找到,可用当前工程文件夹的EDK/EDK_export中找到system.xml文件。

从XPS将硬件平台导入正常后会在Project视图里面看到microblaze_0的硬件平台,需要构建自己的软件平台,选择“File”->"New"->"Software Platform",输入软件平台名称,选择standalone模式(没有操作系统),Finish即可。

然后新建一个C工程,“File”->"New"->"Managed Make C Application Project",输入工程名,选择刚刚生成的软件平台,选择一个空模板,Finnish即可。

由于官网例程已经自带了示例程序,可以直接导入,“File”->"Import..."->"File System",输入下载到的例程路径,..\Genesys_ip_cores_UCF_SDK\SDK\SDK_Workspace\Audio_Demo,全部选择需要导入到的示例src文件即可。系统会自动编译新加入的文件。

测试:a.下载硬件文件“Tools” -> “Program FPGA” -> “Save and Program”

b.运行elf文件。在Project视图里展开新工程,找到.elf文件,右击它选择“Run as” -> “Run on hardware”或者“Debug

as” -> “Debug on hardware”即可运行或调试工程。

c.对于示例程序,LCD会提示当前状态,通过SW0来选择语音输入(0-mic输入,1-线路输入),通过方向按键来控制AC97的操作:Up-录音5秒

Down-播音5秒 (此时LED均会提示录音时间) Left-做耳机1kHz方波 Right-有耳机1kHz方波 Center-两个耳机1kHz方波

和http://www.digilentinc.com/Data/Products/GENESYS/Genesys_bsb_design.zip

以及http://www.digilentinc.com/Data/Products/GENESYS/Genesys_Ip_Cores.zip

最终实现效果:在Genesys开发板上实现语音的采集和播放,并由LCD1602和leds显示语音的状态,对语音的控制由方向按键实现。

使用环境:Xilinx ISE 11.4 (主要是用XPS和SDK)、Windows XP Professional SP3、Digilent GENESYS 开发板

具体过程:

一.搭建硬件平台:(这一步比较复杂)

1.使用XPS的BSB(Base System Builder)搭建单核系统(具体参见Genesys_bsb_design.zip),满足如下条件:

– Use 64KB BRAM (Look at Slide 17 in Genesys_BSB_Guide)

– Set “HARD_ETHERNET_MAC” to use DMA and Interrupt (Look at Slide 18 in Genesys_BSB_Guide)

– Set both UART core types to xps_uart16650 (Look at Slide 19 in Genesys_BSB_Guide)

– Enable both instruction and data cache memory (recommended)

2.加入所需要的IP。

(由于本来只打算使用AC97和LCD的IP,考虑到高低速外设总线分开,还需要一个PLB v4.6的IP,故就只加了这三个IP,但在后面的编译过程中遇到了解决不了的问题,因为对于新加入的PLBv4.6总线来说,还需要一个PLBV46 to PLBV46 Bridge 来与PLB总线连接,对于外围外设的管理,还需要一个EPC(External

Peripheral Control)和Utility Bus Split来完成最终的操作)

因此,除AC97外需要加入五个IP,如下图:(AC97的IP需要在创建BSB时就加入Genesys BSB support文件支持,或者在Project->Project Options->Project Peripheral Repository Search Path里面加入xxx\Digilent_Genesys_BSB_Support\lib这样的支持文件,才能引入官方编译好的AC97

IP)(该支持文件可以在官网下载到)

其中,加入General Purpose IP后将其改名为Char_LCD(如下图),加入PLBv4.6总线IP后将其改名为mb_plb_1(如下图),接下来更改PLB总线设置,如下图,将低速设备如Char_LCD、DIP_Switchs_8Bits、Leds_8Bits、Push_Button_7Bits、RS232_Uart_0、RS232_Uart_1连接到mb_plb_1,至于PLB

bridge其MPLB连接到mb_plb_1,SPLB连接到mb_plb,设置DDR2_SDRAM的参数如下图所示:

接下来对新加入的IP进行配置,首先配置DDR2_SDRAM,如下图,对其四个port进行设置

接下来配置Char_LCD,由于LCD1602有11个GPIO口通信(8位数据、两位读写控制位Wr、Rd,和一位数据命令选择位cd)所以数据位宽11位,如下图:

接下来生成新加入IP的地址,在Address选项卡里面点击Generate Address即可,如下图:

然后配置xps_epc,设置外设的数量,及各种相应时间,如下图:

配置util_bus_split_0 ,如下图:

3.设置IP的端口连接。

首先进入System Assembly View的Port视图:设置两个mb_plb总线的时钟和复位接口,在将Char_LCD的IO口使用Make external外扩出来(与实际的LCD1602连接),如下图:

接下来就会在External Ports里面看到外扩出来的Char_LCD_GPIO_IO,如下图:

用同样的方法,将xps_epc和ac97都外扩出来,如下图:

(外扩的时候,注意观察External Ports里面是不是都有对应的端口出现,有的时候会出现__NOC__(该ISE版本的bug,以后版本没有该问题),此时需要再在刚刚那个Make External的地方选择New Connection,就会出现对应名字的端口,手动将__NOC__的地方改为相应端口名即可)

其中,xps_epc_0的PRH_Addr的xps_epc_0_PRH_Addr_split是Make External后手动修改的名字

对应的External Ports截图如下:(其中xps_epc_0_PRH_Addr以及后面的xps_epc_0_PRH_Addr,[0:1]都是手动修改得到的)

然后修改程序复位时钟为25M,将总线分割的IP的端口手动连到刚刚手动改动的端口上,如下图

至此,外扩端口以及结束,然后添加用户约束文件(管脚约束),复制下载到的Genesys_ip_cores_UCF_SDK /data/Genesys_ip_cores.ucf里面的与相应IP相连的管脚到Project视图里面的UCF File Data/system.ucf里面即可。

编译:“Hardware->Generate Bitstream” 30~60 分钟

“Software->“Generate Libraries and BSPs” “ Build All User Applications”

“Device Configuration” -> “Download Bitstream” 下载后可以从开发板的串口看到测试程序的输入信息(串口:9600,8,n,1)

二.在SDK里面实现具体用户应用程序。

“Project” -> “Export Hardware Design to SDK” 选择Export and Launch SDK

对于出现的“Workspace Launcher”对话框,输入当前所创建的工程文件夹下面的SDK文件夹的路径,如果没有出现该对话框,可用“File” -> “Switch Workspace”更改当前路径。

之后,SDK会自动搜索Hardware Specification File,如果提示未找到,可用当前工程文件夹的EDK/EDK_export中找到system.xml文件。

从XPS将硬件平台导入正常后会在Project视图里面看到microblaze_0的硬件平台,需要构建自己的软件平台,选择“File”->"New"->"Software Platform",输入软件平台名称,选择standalone模式(没有操作系统),Finish即可。

然后新建一个C工程,“File”->"New"->"Managed Make C Application Project",输入工程名,选择刚刚生成的软件平台,选择一个空模板,Finnish即可。

由于官网例程已经自带了示例程序,可以直接导入,“File”->"Import..."->"File System",输入下载到的例程路径,..\Genesys_ip_cores_UCF_SDK\SDK\SDK_Workspace\Audio_Demo,全部选择需要导入到的示例src文件即可。系统会自动编译新加入的文件。

测试:a.下载硬件文件“Tools” -> “Program FPGA” -> “Save and Program”

b.运行elf文件。在Project视图里展开新工程,找到.elf文件,右击它选择“Run as” -> “Run on hardware”或者“Debug

as” -> “Debug on hardware”即可运行或调试工程。

c.对于示例程序,LCD会提示当前状态,通过SW0来选择语音输入(0-mic输入,1-线路输入),通过方向按键来控制AC97的操作:Up-录音5秒

Down-播音5秒 (此时LED均会提示录音时间) Left-做耳机1kHz方波 Right-有耳机1kHz方波 Center-两个耳机1kHz方波

相关文章推荐

- 浅析如何使用busybox的udhcpc实现开发板ip和dns自动获取

- 关于Java Web 使用Spring中使用Quartz(定时调用、实现固定时间执行), 触发定时器(执行某些任务)的实例

- 使用ftp实现pc与开发板的文件传输

- 使用IP调用https的webservice问题

- SpringCloud系列五:Ribbon 负载均衡(Ribbon 基本使用、Ribbon 负载均衡、自定义 Ribbon 配置、禁用 Eureka 实现 Ribbon 调用)

- onvif规范的实现:使用gSOAP创建SOAP调用实例

- 使用 RMI + ZooKeeper 实现远程调用框架

- 讯为iTOP4412开发板ARM-linux 使用OPENCV调用USB摄像头

- 不使用Orchestration实现Web Service调用

- 使用“事件监听/链式事件处理方式”实现window.onload同时调用多个函数

- 使用jsonp跨域调用百度js实现搜索框智能提示,并实现鼠标和键盘对弹出框里候选词的操作【附源码】

- 动态方法调用和使用通配符实现类似struts1.x的dispatchAction功能

- 安卓四大组件之二#2-使用AIDL技术实现动态调用其他app中的Service的方法

- Windows7中使用Task Scheduler调用WinScp批处理实现上传下载文件

- 使用hadoop中的RPC框架实现远程调用

- 使用boost实现c++与python的相互调用

- 使用vuex实现父组件调用子组件方法

- 面向过程就是分析出解决问题所需要的步骤,然后用函数把这些步骤一步一步实现,使用的时候一个一个依次调用就可以了;面向对象是把构成问题事务分解成各个对象,建立对象的目的不是为了完成一个步骤,而是为了描叙某个事物在整个解决问题的步骤中的行为(转)

- Dubbo实现RPC调用使用入门

- 使用nhibernate调用存储过程实现多返回值