(转):内存器件介绍之RAM篇(六)

2011-01-10 21:43

176 查看

在关于内存的前面五篇相关介绍文字中,基本上都是关于内存原理性方面的内容,下面介绍点DDR总线匹配方式和信号时序测试方面的实用内容。

♦DDR总线的匹配方式

SDRAM芯片总线使用的是3.3V LVTTL(Low Voltage Transistor-Transistor Logic)逻辑电平;

DDR芯片总线使用的是SSTL-2(Stub Series Terminated Logic 2.5V,短线串联终止逻辑)逻辑电平,I/O端口电压2.5V;

DDR2芯片总线使用的是SSTL-18(Stub Series Terminated Logic 1.8V,短线串联终止逻辑)逻辑电平,I/O端口电压1.8V;

DDR3芯片总线使用的是SSTL-15(Stub Series Terminated Logic 1.5V,短线串联终止逻辑)逻辑电平,I/O端口电压1.5V;

DDR/DDR2/DDR3总线有四种匹配方式(其实是SSTL逻辑的匹配方式):

1).串联匹配

此匹配方式不需要VTT电源,但属于非理想匹配,DDR Controller的驱动能力对接收器件波形影响很大,且电路中ISI效应明显,串联电阻视驱动能力大小调整,典型值为25ohm。

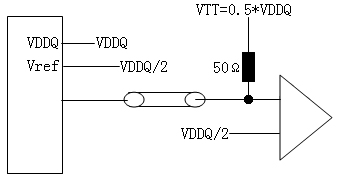

2).单端上拉匹配

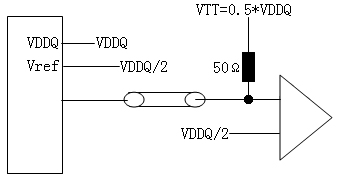

单端上拉匹配是内存条设计中最常用的匹配方式,设计中需注意要将上拉电阻靠近接收端放置。现在的简化设计中,一般不提供独立的VTT电源,而是利用两个100ohm电阻分别上拉到VDDQ和下来到地,分压得到VDDQ一半的电压,而且等效阻抗也是50ohm,效果一样。

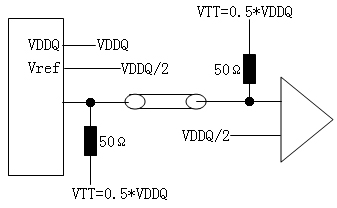

3).双端上拉匹配

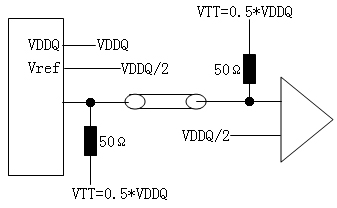

此种匹配方式常用于双向信号传输线路,并且要求BUFFER的驱动能力较强。

4).RC匹配方式

RC匹配主要用于多负载的地址、控制信号匹配,使信号平滑。

♦内存信号的时序测试(也就是SSTL逻辑电平的时序测试)

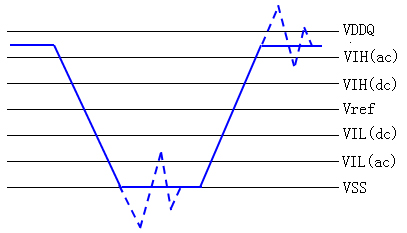

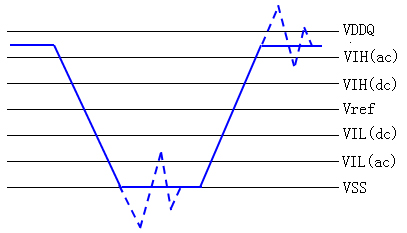

SSTL逻辑电平结构中的接口参数包括:VDDQ、VIH(ac)、VIH(dc)、Vref、VIL(dc)、VIL(ac),VSS,如下图所示。

1).VIH(ac)输入高电平交流参数:当信号向上穿越此阀值后为逻辑高电平的开始;

2).VIH(dc)输入高电平直流参数:当信号向下穿越此阀值后为逻辑高电平的结束;

3).VIL(ac)输入低电平交流参数:当信号向下穿越此阀值后为逻辑低电平的开始;

4).VIL(dc)输入低电平直流参数:向信号向上穿越此阀值后为逻辑低电平的结束。

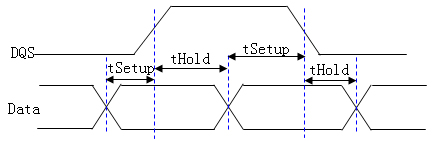

DDR地址、控制信号的建立和保持时间均参考时钟信号CK、CK#,而数据信号的建立时间和保持时间参考的却是DQS。数据信号的建立和保持时间测试方法分为以下四种情况。

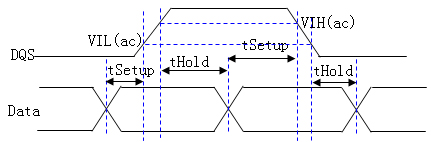

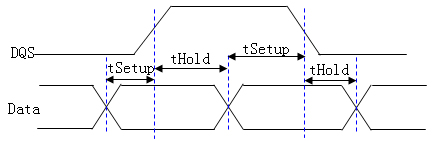

1).在理想条件下,DQS和数据的Skew rate(信号上升/下降沿电平幅度与时间的比值,反应的是信号电平跳变的速度快慢)均大于等于1V/ns。此时数据的建立时间tSetup和数据的保持时间tHold测试方法如下图所示。

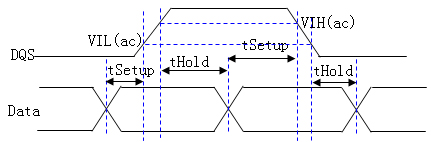

2).在非理想条件下,DQS的Skew rate小于等于1V/ns,数据信号的Skew rate大于等于1V/ns。此时数据的建立时间tSetup和数据的保持时间tHold测试方法如下图所示。

3). 在非理想条件下,数据的Skew rate小于等于1V/ns,DQS信号的Skew rate大于等于1V/ns。此时数据的建立时间tSetup和数据的保持时间tHold测试方法如下图所示。

4).在极不理想情况下,DQS和数据的Skew rate小于等于1V/ns。此时数据的建立时间tSetup和数据的保持时间tHold测试方法如下图所示。

----------------(全文完)---------------

转自:中国通信人博客 » Andy » 日志

♦DDR总线的匹配方式

SDRAM芯片总线使用的是3.3V LVTTL(Low Voltage Transistor-Transistor Logic)逻辑电平;

DDR芯片总线使用的是SSTL-2(Stub Series Terminated Logic 2.5V,短线串联终止逻辑)逻辑电平,I/O端口电压2.5V;

DDR2芯片总线使用的是SSTL-18(Stub Series Terminated Logic 1.8V,短线串联终止逻辑)逻辑电平,I/O端口电压1.8V;

DDR3芯片总线使用的是SSTL-15(Stub Series Terminated Logic 1.5V,短线串联终止逻辑)逻辑电平,I/O端口电压1.5V;

DDR/DDR2/DDR3总线有四种匹配方式(其实是SSTL逻辑的匹配方式):

1).串联匹配

此匹配方式不需要VTT电源,但属于非理想匹配,DDR Controller的驱动能力对接收器件波形影响很大,且电路中ISI效应明显,串联电阻视驱动能力大小调整,典型值为25ohm。

2).单端上拉匹配

单端上拉匹配是内存条设计中最常用的匹配方式,设计中需注意要将上拉电阻靠近接收端放置。现在的简化设计中,一般不提供独立的VTT电源,而是利用两个100ohm电阻分别上拉到VDDQ和下来到地,分压得到VDDQ一半的电压,而且等效阻抗也是50ohm,效果一样。

3).双端上拉匹配

此种匹配方式常用于双向信号传输线路,并且要求BUFFER的驱动能力较强。

4).RC匹配方式

RC匹配主要用于多负载的地址、控制信号匹配,使信号平滑。

♦内存信号的时序测试(也就是SSTL逻辑电平的时序测试)

SSTL逻辑电平结构中的接口参数包括:VDDQ、VIH(ac)、VIH(dc)、Vref、VIL(dc)、VIL(ac),VSS,如下图所示。

1).VIH(ac)输入高电平交流参数:当信号向上穿越此阀值后为逻辑高电平的开始;

2).VIH(dc)输入高电平直流参数:当信号向下穿越此阀值后为逻辑高电平的结束;

3).VIL(ac)输入低电平交流参数:当信号向下穿越此阀值后为逻辑低电平的开始;

4).VIL(dc)输入低电平直流参数:向信号向上穿越此阀值后为逻辑低电平的结束。

DDR地址、控制信号的建立和保持时间均参考时钟信号CK、CK#,而数据信号的建立时间和保持时间参考的却是DQS。数据信号的建立和保持时间测试方法分为以下四种情况。

1).在理想条件下,DQS和数据的Skew rate(信号上升/下降沿电平幅度与时间的比值,反应的是信号电平跳变的速度快慢)均大于等于1V/ns。此时数据的建立时间tSetup和数据的保持时间tHold测试方法如下图所示。

2).在非理想条件下,DQS的Skew rate小于等于1V/ns,数据信号的Skew rate大于等于1V/ns。此时数据的建立时间tSetup和数据的保持时间tHold测试方法如下图所示。

3). 在非理想条件下,数据的Skew rate小于等于1V/ns,DQS信号的Skew rate大于等于1V/ns。此时数据的建立时间tSetup和数据的保持时间tHold测试方法如下图所示。

4).在极不理想情况下,DQS和数据的Skew rate小于等于1V/ns。此时数据的建立时间tSetup和数据的保持时间tHold测试方法如下图所示。

----------------(全文完)---------------

转自:中国通信人博客 » Andy » 日志

相关文章推荐

- 内存器件介绍之RAM篇

- (转):内存器件介绍之RAM篇(一)

- (转):内存器件介绍之RAM篇(二)

- (转):内存器件介绍之RAM篇(三)

- (转):内存器件介绍之RAM篇(四)

- (转):内存器件介绍之RAM篇(五)

- Memcached 内存分配机制介绍

- Android系统匿名共享内存Ashmem(Anonymous Shared Memory)简要介绍和学习计划 (四)

- 介绍两个检测内存越界的工具pagehedap和gflags

- 内存开始1M地址的介绍

- Spark入门实战系列--10.分布式内存文件系统Tachyon介绍及安装部署

- Java提高篇—— 简单介绍Java 的内存泄漏

- RAM和ROM介绍

- IOS内存泄漏检查原理和检查工具介绍

- jvm虚拟机学习之内存区域介绍

- KVM 介绍(2):CPU 和内存虚拟化

- MySQL内存表的特性与使用介绍

- 全面介绍Windows内存管理机制及C++内存分配实例(四):内存映射文件

- Linux中Swap与Memory内存简单介绍

- Linux中Swap与Memory内存简单介绍