arm体系结构学习笔记 part1--处理器模式与寄存器

2010-12-04 22:25

495 查看

先来看看arm920t的处理器的七种模式:

ARM920T supports seven modes of operation:· User (usr): The normal ARM program execution state

· FIQ (fiq): Designed to support a data transfer or channel process

· IRQ (irq): Used for general-purpose interrupt handling

· Supervisor (svc): Protected mode for the operating system

· Abort mode (abt): Entered after a data or instruction prefetch abort

· System (sys): A privileged user mode for the operating system

· Undefined (und): Entered when an undefined instruction is executed

从上而下分别为:

*用户模式:一般ARM程序执行的模式

*快速中断模式:支持高速数据传输和通道处理

*外部中断模式:通常的中断处理

*特权模式:提供给操作系统使用的保护模式

*数据访问终止模式:数据或者指令预取失败后进入的模式

*系统模式:操作系统的特权用户模式

*未定义模式:当执行未定义指令的时候进入的模式

Mode changes can be made using the control of software, or may be brought about by external interrupts or

exception processing. Most application programs will execute in User mode. The non-user modes' known as

privileged modes-are entered in order to service interrupts or exceptions, or to access protected resources.

模式的切换可以由软件控制 也可以由外部中断或者异常处理引起。 大部分的程序都运行在用户模式。当响应中断服务,异常发生,或者访问受保护的资源时进入非用户模式即特权模式。

***既然arm920t有七种模式,那么处理器当前运行的模式如何获取?

答案是 可以通过设置cpsr的程序状态寄存器的低五位决定了处理器的当前模式

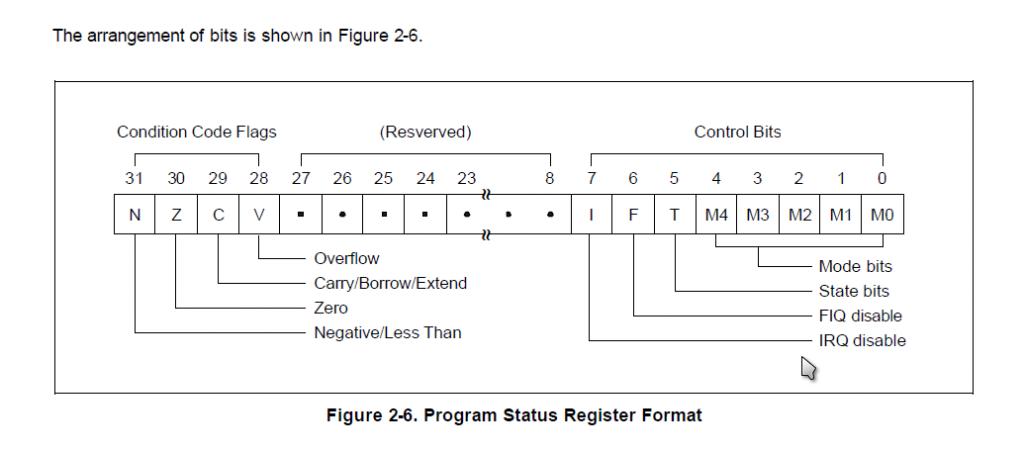

既然谈到了cpsr 那么我们就来看看cpsr寄存器:

THE PROGRAM STATUS REGISTERSThe ARM920T contains a Current Program Status Register (CPSR), plus five Saved Program Status Registers

(SPSRs) for use by exception handlers. These register's functions are:

· Hold information about the most recently performed ALU operation

· Control the enabling and disabling of interrupts

· Set the processor operating mode

cpsr程序状态寄存器的功能:

*保存逻辑运算单元ALU执行的信息

*使能或者禁止中断

*设置处理器的操作模式

再来看看cpsr各位的信息:

The N, Z, C and V bits are the condition code flags. These may be changed as a result of arithmetic and logical

operations, and may be tested to determine whether an instruction should be executed.

31-28:用于控制逻辑运算,逻辑运算完成可能会改变其中的某一位或者某几位,也可能都不变。这些位也可以作为指令执行与否的判定条件。具体就不深入写了,查看datasheet或者看看arm指令可以明白有些指令是可以带有条件控制的可选参数的。eg. beq lmain

27-8:为预留位,以后系列的处理器可能用到

I位:为IRQ中断控制位 I=1时禁止IRQ中断

F位:为FIQ中断控制位 F=1时禁止FIQ中断

T位:用来控制指令执行状态 T=0为arm指令 T=1为thumb指令

M4, M3, M2, M1 and M0 bits (M[4:0]) 模式控制位。

具体参见下图:

下面来看看如何读取cpsr的内容的代码,并作简要的分析:

代码如下 makefile就不贴了void (*show)(char *, ...)=0x33f9303c;

int main(char *argc, char **argv)

{

unsigned long cpsr;

__asm__ __volatile__(

"mrs %0, cpsr /n"

: "=r" (cpsr)

);

show("mode =0x%x/n", cpsr);

return 0;

}这里涉及到gcc内嵌汇编的知识 可以参照这篇博文先作一定的了解

http://blog.csdn.net/littlehedgehog/archive/2008/04/08/2259665.aspx

运行结果:

Fantasy >go 30000000 ## Starting application at 0x30000000 ... mode =0x600000d3 ## Application terminated, rc = 0x0

看看0x600000d3是高四位为0110 低八位为1101 0011

看看处理器模式位为低五位 10011 为svc特权模式。

T位为0表示cpu运行于arm态

F位为和I位为1表示禁止IRQ和FIQ中断

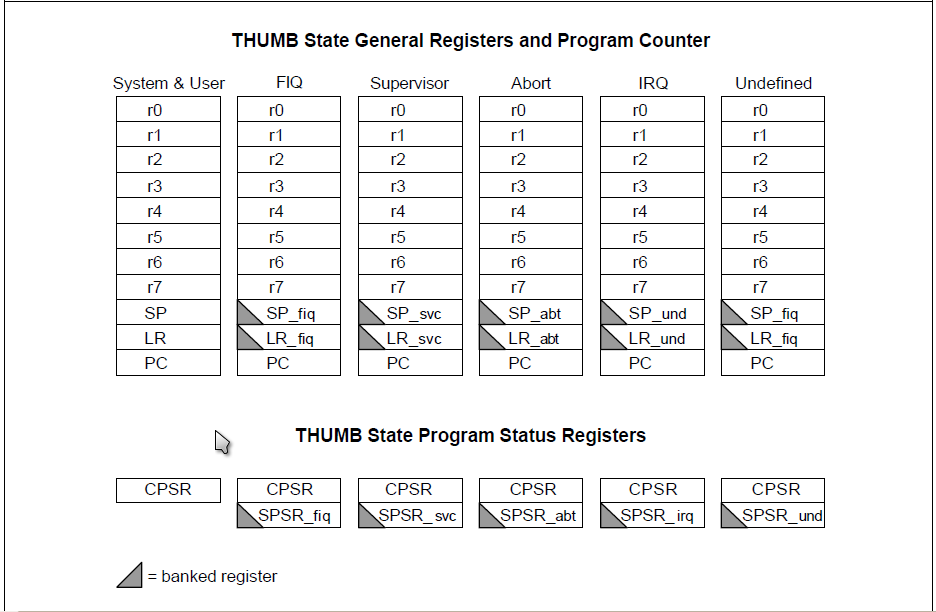

下面了解一下arm920t的寄存器内容:REGISTERS

ARM920T has a total of 37 registers - 31 general-purpose 32-bit registers and six status registers - but these cannot

all be seen at once. The processor state and operating mode decides which registers are available to the

programmer.

arm920t总共有37个寄存器--31个通用的32位寄存器和6个状态寄存器。但是这些寄存器同一时刻并不是全部可见。处理器的状态和工作模式决定了哪些寄存器对程序员是可见的。

The ARM State Register Set

In ARM state, 16 general registers and one or two status registers are visible at any one time.

在arm态,任何时候都有16个通用寄存器和一到两个状态寄存器是可见的。

见下图:

简单说一下 以用户模式和系统模式下的r14和FIQ下的R14_fiq为例 用户模式和系统模式下的r14是同一个物理寄存器 但是用户模式或者系统模式下的r14和FIQ模式下的r14是两个完全不同的物理寄存器 所以 (*^__^*) 嘻嘻…… 带左下三角的寄存器都是不同的物理寄存器 37个 有空好好数一下 嘿嘿

同理 thumb态就直接上图了 呵呵 偷懒一下

void (*show)(char *, ...)=0x33f9303c;

int main(char *argc, char **argv)

{

unsigned long cpsr;

__asm__ __volatile__(

"mrs %0, cpsr /n"

: "=r" (cpsr)

);

show("mode =0x%x/n", cpsr);

return 0;

}

相关文章推荐

- ARM&LINUX学习笔记(4)---ARM 体系结构

- 朱老师ARM裸机学习笔记(五):ARMCPU工作模式以及寄存器讲解

- 2440,学习笔记之ARM 处理器工作模式

- arm体系结构学习笔记 part4 -- 异常处理的返回

- 一份好的ARM体系结构学习笔记

- 一份好的ARM体系结构学习笔记

- ARM体系结构笔记①---(ARM的7种模式、寄存器、存储空间、指令、中断、最小系统)

- ARM裸机全集之ARM体系结构(学习笔记)

- ARM学习笔记之一:ARM体系结构

- 学习笔记:用于事件多路分离和分派的reactor体系结构模式

- 汇编学习笔记之处理器体系结构

- arm体系结构学习笔记 part2 -- 中断相关

- ARM底层学习笔记-中断体系结构

- arm体系结构学习笔记 part3 -- 异常处理机制

- ARM1176JZF-S 体系结构之寄存器和操作模式

- ARM框架学习笔记 part1 寄存器、存储空间

- ARM学习笔记--中断体系结构

- Java web学习笔记之1.程序开发体系结构

- Intel汇编语言程序设计学习-第二章 IA-32处理器体系结构-上

- 2017-2018-1 20155312 学习《深入理解计算机系统》第四章:处理器体系结构