关于FPGA软件版本兼容问题

2010-11-14 12:47

316 查看

FPGA的软件一直更新得很快,随之而来就是新版本与旧版本之间的兼容就成了一个问题。以前也听过很多关于FPGA软件版本兼容的问题,很多人都说向上兼容。一直只是听说,今天终于亲身撞墙了。

下面附上例子解说,(例子来之与萧宏森大哥的博客!链接地址:/article/6947257.html

请注意红色字体

使用環境:Quartus II 7.2 SP3 + ModelSim-Altera 6.1g

除頻器在實務中隨時會用到,如DE2只提供50MHz與27MHz的clock,如CMOS用的是25MHz,因此就必須手動作一個除頻器產生25MHz,利用計數器的基礎,就可以設計一個除頻器。

Method 1:

使用Verilog

除2的除頻器

最簡單的除頻器,還不需要到計數器就可以完成。

div2.v / Verilog (沒用到計數器)

1 /*

2 (C) OOMusou 2008 http://oomusou.cnblogs.com 3

4 Filename : div2.v

5 Compiler : Quartus II 7.2 SP3 + ModelSim-Altera 6.1g

6 Description : Demo how to write frequency divider by 2

7 Release : 07/12/2008 1.0

8 */

9

10 module div2 (

11 input clk,

12 input rst_n,

13 output reg o_clk

14 );

15

16 always@(posedge clk or negedge rst_n) begin

17 if (!rst_n)

18 o_clk <= 0;

19 else

20 o_clk <= ~o_clk;

21 end

22

23 endmodule

頻率要變一半,也就是周期要變兩倍,也就是本來一個clock的時間,變成半個clock的時間,所以每次clock正源觸發時,剛好是0變1、1變0的時機。由於除2的除頻器很簡單,所以不需要用到記數器就可完成,但更複雜的除頻器一定要用到計數器,所以我們也用計數器寫一個除2除頻器,幫助了解後,才能寫更複雜的除頻器。

下面是测试脚本:

testbench

div2_tb.v / Verilog

1 /*

2 (C) OOMusou 2008 http://oomusou.cnblogs.com 3

4 Filename : div2_tb.v

5 Compiler : Quartus II 7.2 SP3 + ModelSim-Altera 6.1g

6 Description : Demo how to write frequency divider by 2 testbench

7 Release : 07/16/2008 1.0

8 */

9 `timescale 1ns/10ps

10 module div2_tb;

11 reg clk;

12 reg rst_n;

13 wire o_clk;

14

15 div2 u0 (

16 .clk(clk),

17 .rst_n(rst_n),

18 .o_clk(o_clk)

19 );

20

21 initial begin

22 clk = 1'b1;

23 rst_n = 1'b1;

24 end

25

26 // 50MHz clk

27 always #10 clk = ~clk;

28 endmodule

march_seven`timescale 1 ns/ 1 ns//

module div_vlg_tst();

reg clk;

reg rst;

wire clk_out;

div i1 (

.clk(clk),

.clk_out(clk_out),

.rst(rst)

);

initial

begin

clk = 1'b1;

rst= 1'b1;

end

always

#10 clk =~clk;

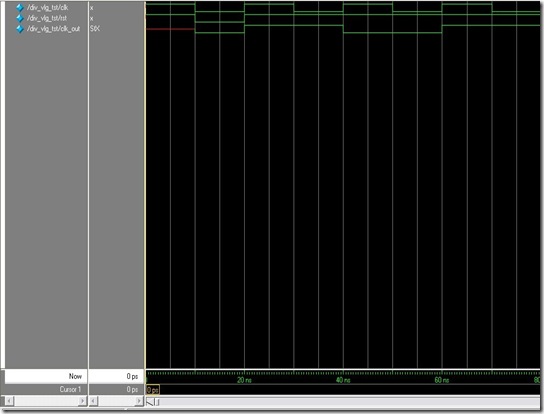

endmodule从图中可以看出,在复位信号没来之前,clk_out处于红线状态,不定态,当复位信号到来之后,clk_out就正常实现二分频了。

所以由此只能证明是版本问题,同样的代码,同样的测试文件,在不同版本中,居然出现两种输出结果。除了版本的问题我想不到别的,求解?

从这个例子中我总结一下:

1.Windows Live Writer 中插入代码的时候,没有verilog语言选择,希望以后破解的牛人加多些硬件语言支持。

2.我到现在还不知道怎样插入代码可以有代码行序号,看亚峰萧宏森前辈的代码都是有序列号的,帅呆了!求教

3.测试脚本中的第一行timescale 1 ns/ 1 ns这句话,听说将后面的改成1ns可以加快仿真速度,据我所知后面的那个是时间精度设置,至于改了之后重真的快了,我还真没觉察到!

4.还有一点不清楚的是,每次改变testbench的时候,都要重新关闭modelsim,再重新运行一下仿真。(这个比较麻烦)希望高手提供更好的方法,可以不用这么麻烦!

[/code]

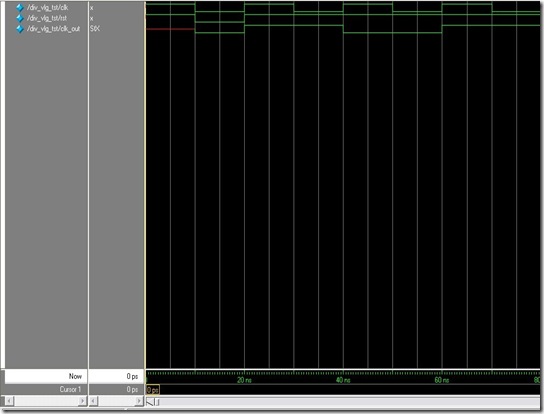

测试结果波形图:

从图中,看出clk_out一直都处于不定状态,即红线!!!

后来我把测试脚本中的rst= 1'b1;改成rst=1;#10 rst=0;#10 rst=1;

测试结果波形图:

下面附上例子解说,(例子来之与萧宏森大哥的博客!链接地址:/article/6947257.html

请注意红色字体

使用環境:Quartus II 7.2 SP3 + ModelSim-Altera 6.1g

除頻器在實務中隨時會用到,如DE2只提供50MHz與27MHz的clock,如CMOS用的是25MHz,因此就必須手動作一個除頻器產生25MHz,利用計數器的基礎,就可以設計一個除頻器。

Method 1:

使用Verilog

除2的除頻器

最簡單的除頻器,還不需要到計數器就可以完成。

div2.v / Verilog (沒用到計數器)

1 /*

2 (C) OOMusou 2008 http://oomusou.cnblogs.com 3

4 Filename : div2.v

5 Compiler : Quartus II 7.2 SP3 + ModelSim-Altera 6.1g

6 Description : Demo how to write frequency divider by 2

7 Release : 07/12/2008 1.0

8 */

9

10 module div2 (

11 input clk,

12 input rst_n,

13 output reg o_clk

14 );

15

16 always@(posedge clk or negedge rst_n) begin

17 if (!rst_n)

18 o_clk <= 0;

19 else

20 o_clk <= ~o_clk;

21 end

22

23 endmodule

頻率要變一半,也就是周期要變兩倍,也就是本來一個clock的時間,變成半個clock的時間,所以每次clock正源觸發時,剛好是0變1、1變0的時機。由於除2的除頻器很簡單,所以不需要用到記數器就可完成,但更複雜的除頻器一定要用到計數器,所以我們也用計數器寫一個除2除頻器,幫助了解後,才能寫更複雜的除頻器。

下面是测试脚本:

testbench

div2_tb.v / Verilog

1 /*

2 (C) OOMusou 2008 http://oomusou.cnblogs.com 3

4 Filename : div2_tb.v

5 Compiler : Quartus II 7.2 SP3 + ModelSim-Altera 6.1g

6 Description : Demo how to write frequency divider by 2 testbench

7 Release : 07/16/2008 1.0

8 */

9 `timescale 1ns/10ps

10 module div2_tb;

11 reg clk;

12 reg rst_n;

13 wire o_clk;

14

15 div2 u0 (

16 .clk(clk),

17 .rst_n(rst_n),

18 .o_clk(o_clk)

19 );

20

21 initial begin

22 clk = 1'b1;

23 rst_n = 1'b1;

24 end

25

26 // 50MHz clk

27 always #10 clk = ~clk;

28 endmodule

march_seven`timescale 1 ns/ 1 ns//

module div_vlg_tst();

reg clk;

reg rst;

wire clk_out;

div i1 (

.clk(clk),

.clk_out(clk_out),

.rst(rst)

);

initial

begin

clk = 1'b1;

rst= 1'b1;

end

always

#10 clk =~clk;

endmodule从图中可以看出,在复位信号没来之前,clk_out处于红线状态,不定态,当复位信号到来之后,clk_out就正常实现二分频了。

所以由此只能证明是版本问题,同样的代码,同样的测试文件,在不同版本中,居然出现两种输出结果。除了版本的问题我想不到别的,求解?

从这个例子中我总结一下:

1.Windows Live Writer 中插入代码的时候,没有verilog语言选择,希望以后破解的牛人加多些硬件语言支持。

2.我到现在还不知道怎样插入代码可以有代码行序号,看亚峰萧宏森前辈的代码都是有序列号的,帅呆了!求教

3.测试脚本中的第一行timescale 1 ns/ 1 ns这句话,听说将后面的改成1ns可以加快仿真速度,据我所知后面的那个是时间精度设置,至于改了之后重真的快了,我还真没觉察到!

4.还有一点不清楚的是,每次改变testbench的时候,都要重新关闭modelsim,再重新运行一下仿真。(这个比较麻烦)希望高手提供更好的方法,可以不用这么麻烦!

[/code]

测试结果波形图:

从图中,看出clk_out一直都处于不定状态,即红线!!!

后来我把测试脚本中的rst= 1'b1;改成rst=1;#10 rst=0;#10 rst=1;

测试结果波形图:

相关文章推荐

- 关于软件开发过程中的版本兼容问题

- 关于DevExpress2011.1.8版本和NetFramework4.5框架的不兼容问题解决方法

- 关于软件的版本控制问题

- 关于打包jre版本不兼容问题的处理

- 关于android版本兼容的一些问题

- 关于jdk的版本兼容问题

- 关于app store distribution出现的'armv7'与最小版本'3.0'不兼容的问题

- 关于Android兼容7.0系统版本的问题

- 关于Ubuntu”系统的网络服务与此版本的网络管理器不兼容“问题的解决方案

- 关于今天easyui的坑 DateGrid兼容$ref问题,版本easyui 1.2.2

- 软件启动时,出现错误-关于软件启动兼容问题汇总

- 关于Ubuntu”系统的网络服务与此版本的网络管理器不兼容“问题解决方案

- 关于eclipse当中的版本兼容问题(一点小问题的解决也需要大量的时间)

- 关于不同版本软件复用同一个脚本的问题

- 关于MSSQL的版本不兼容问题

- 关于Bugly版本兼容Android7.0 FileProvider与PhotoPicker冲突问题

- 关于IIS部署时出现“System.Data.OracleClient 需要 Oracle 客户端软件 8.1.7 或更高版本”的问题解决摘要

- 关于HTML5 Placeholder新标签低版本浏览器下不兼容的问题分析及解决办法

- 关于Scala JDK与IDEA版本兼容的问题

- 关于Fragment API版本兼容问题