基于s3c2410的YL-LCD35液晶驱动的分析

2010-01-29 17:01

197 查看

转载请注明出处

作者:小马

手上有一块2410的板子, LCD是YL-LCD35. 写一个驱动分析,为自己做一个技术笔记,供以后参考.

2410具有片内LCD控制器, 写好一个lcd的驱动,最重要的就是做好内部寄存器的配置. 2410支持STN和TFT两种LCD, 最高支持24bpp显示.

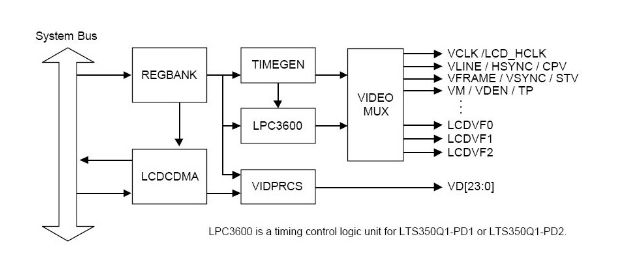

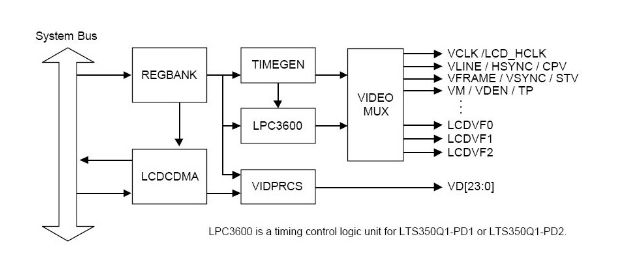

上面这幅图是2410 datasheet上截取下来的. 它是2410LCD驱动器的内部框图.

REGBANK是寄存器组. 需要开发人员手动配置的寄存器都在这里面.下面会有详细说明

LCDDMA 是LCD驱动器的专用DMA. 有了DMA就可以和外设直接交换数据,不占用CPU.

TIEMGEN 和LPC3600用来产生和时序有关的控制信号.

VIDPRCS类似于一种介于LCDDMA和外设间数据缓冲区.

从这上图也可以看出, 2410的驱动器主要做两件事: 一是产生必要的时序控制信号. 二产生视频数据信号.而这件事都是通过配置REGBANK里的寄存器完成的.

做过LCD驱动开发的人都清楚, 时序对像LCD这种慢显示器件是最重要的. 我在这里主要讲一下时序方面的配置, 其它比如数据信号,地址指针等比较简单, 看一下datasheet很容易明白. 这里不做叙述.

关于时序, 下面几个信号要介绍一下:

VCLK 是像素时钟信号,可以把它当做LCD的时钟信号.

VSYNC是帧同步信号.也就是说VSYNC每发一脉冲就有一个新的视频信号开始传送.

HSYNC是行同步信号.

VDEN数据发送使能信号.

LEND 行结束信号.

对上面几个信号有了初步的认识之后, 就可以看下面的两幅图了. 第一幅图是TFT液晶的一个典型的时序图, 第二幅图是YL-LCD35这款LCD的时序图

图1

图2

对比两幅图, DOTCLK相当于VCLK, 图2的第二行标有”1 Horizonital Period”的相当于图1的HSYNC。 同理可得到其它信号的对应关系. 在图1中, VBPD,VFPD, VSPW信号是回扫时间,这是为了兼容以前的CRT显示器而保留的(HSYNC类似). 配置好这些信号也就等于配置好VSYNC了. VCLK是由HCKL和LCDCON1寄存器决定的. 具体公式如下:

VCLK = HCLK / [(CLKVAL+1) ´ 2]

示例代码如下:

作者:小马

手上有一块2410的板子, LCD是YL-LCD35. 写一个驱动分析,为自己做一个技术笔记,供以后参考.

2410具有片内LCD控制器, 写好一个lcd的驱动,最重要的就是做好内部寄存器的配置. 2410支持STN和TFT两种LCD, 最高支持24bpp显示.

上面这幅图是2410 datasheet上截取下来的. 它是2410LCD驱动器的内部框图.

REGBANK是寄存器组. 需要开发人员手动配置的寄存器都在这里面.下面会有详细说明

LCDDMA 是LCD驱动器的专用DMA. 有了DMA就可以和外设直接交换数据,不占用CPU.

TIEMGEN 和LPC3600用来产生和时序有关的控制信号.

VIDPRCS类似于一种介于LCDDMA和外设间数据缓冲区.

从这上图也可以看出, 2410的驱动器主要做两件事: 一是产生必要的时序控制信号. 二产生视频数据信号.而这件事都是通过配置REGBANK里的寄存器完成的.

做过LCD驱动开发的人都清楚, 时序对像LCD这种慢显示器件是最重要的. 我在这里主要讲一下时序方面的配置, 其它比如数据信号,地址指针等比较简单, 看一下datasheet很容易明白. 这里不做叙述.

关于时序, 下面几个信号要介绍一下:

VCLK 是像素时钟信号,可以把它当做LCD的时钟信号.

VSYNC是帧同步信号.也就是说VSYNC每发一脉冲就有一个新的视频信号开始传送.

HSYNC是行同步信号.

VDEN数据发送使能信号.

LEND 行结束信号.

对上面几个信号有了初步的认识之后, 就可以看下面的两幅图了. 第一幅图是TFT液晶的一个典型的时序图, 第二幅图是YL-LCD35这款LCD的时序图

图1

图2

对比两幅图, DOTCLK相当于VCLK, 图2的第二行标有”1 Horizonital Period”的相当于图1的HSYNC。 同理可得到其它信号的对应关系. 在图1中, VBPD,VFPD, VSPW信号是回扫时间,这是为了兼容以前的CRT显示器而保留的(HSYNC类似). 配置好这些信号也就等于配置好VSYNC了. VCLK是由HCKL和LCDCON1寄存器决定的. 具体公式如下:

VCLK = HCLK / [(CLKVAL+1) ´ 2]

示例代码如下:

#define VBPD_320240 (4) //垂直同步信号的后肩

#define VFPD_320240 (4) //垂直同步信号的前肩

#define VSPW_320240 (4) //垂直同步信号的脉宽

#define HBPD_320240 (13) //水平同步信号的后肩

#define HFPD_320240 (4) //水平同步信号的前肩

#define HSPW_320240 (18) //水平同步信号的脉宽

rLCDCON1 = (CLKVAL_TFT_320240<<8) | (0<<7) | (3<<5) | (12<<1) | 0;

rLCDCON2 = (VBPD_320240<<24) | (LINEVAL_TFT_320240<<14) | (VFPD_320240<<6)

| (VSPW_320240);

rLCDCON3 = (HBPD_320240<<19) | (HOZVAL_TFT_320240<<8) | (HFPD_320240);

rLCDCON4 = (13<<8) | (HSPW_320240);

rLCDCON5 = (1<<11) | (1<<10) | (1<<9) | (1<<8) | (0<<7) | (0<<6)

| (1<<3) |(BSWP<<1) | (HWSWP);

相关文章推荐

- [STM8L]基于STM8L152的TAB段式LCD液晶驱动的分析 - 单片机干货 - 中国电子技术论坛 - 最好最受欢迎电子论坛!

- Linux USB HOST驱动分析(基于S3C2410)

- Nandflash 驱动深度分析(基于S3C2410)

- 基于ARM9处理器的linux-2.6.32.2操作系统内核移植手记part5.2(LCD驱动源码分析及移植之platform driver)

- Nandflash 驱动深度分析(基于S3C2410)

- 基于S3C2410的SD卡linux驱动分析一

- S3C2410 LCD驱动的移植(基于linux-2.6.15.4内核)

- 基于linux-2.6.33的液晶驱动之lcd

- S3C2410驱动分析之LCD驱动

- 基于S3C2410平台的LCD for Linux 2.6 驱动移植

- 基于s3c2410的lcd和触摸屏驱动移植

- s3c2410 LCD驱动的结构分析

- 基于S3C2410的SD卡linux驱动分析二

- s3c2410_lcd & frame buffer 驱动分析

- 基于ok6410的韦东山驱动视频简要分析--lcd驱动

- s3c2410_lcd & frame buffer 驱动分析 int __init s3c2410fb_probe(struct device *dev) { struct s3c2410f

- s3c2410_lcd & frame buffer 驱动分析 (转)

- s3c2410_lcd & frame buffer 驱动分析

- 基于ARM芯片S3C2410的TFT-LCD驱动方法

- S3C2410驱动分析的LCD驱动