Cadence ICFB 5141/IUS58 数字、混合信号仿真

2007-01-16 01:52

639 查看

[b]数字、混合信号仿真[/b]

路径设置

首先要设置路径,可以这样设置(icfb 和ius和在一起了):

setenv ic50 /tools/cadence/ic5141

setenv ius58 /opt/cadence/ius58

set LD_LIBRARY_PATH = ( $ic50/tools/lib $ic50/tools/dfII/lib $

4000

ic50/tools/tcltk/tcl8.0/lib $ic50/tools/tcltk/tk8.0/lib ${ius58}/tools/verilog/lib $ius58/tools/lib $LD_LIBRARY_PATH)

set path = ( ${ius58}/tools/verilog/bin $ius58/tools/bin $ic50/tools/bin $ic50/tools/dfII/bin $ic50/tools/dracula/bin $path )

数字仿真

步骤:

1.在icfb中建立verilog 的view,(包括模块和testbench,testbench的view名也是verilog)

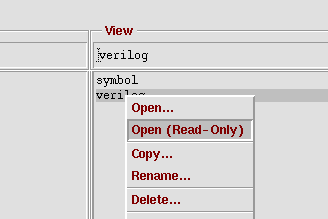

2.右键点击testbench的verilog view,选择“open(read-only)”

在verilog阅读窗的菜单上选择tools=>verilog-xl

Verilog-xl会被激活。

3.用verilog-xl仿真,试一试就会用了

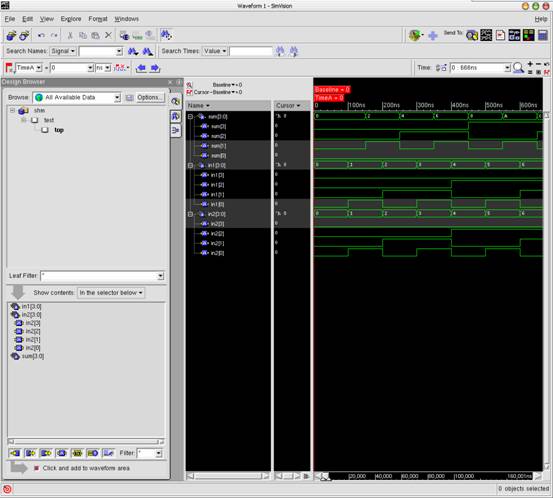

仿真完成后View Waveform的按钮会被激活,

按这个按钮,simvision打开

Simvision的文档自己找一下cdsdoc吧

混合信号仿真

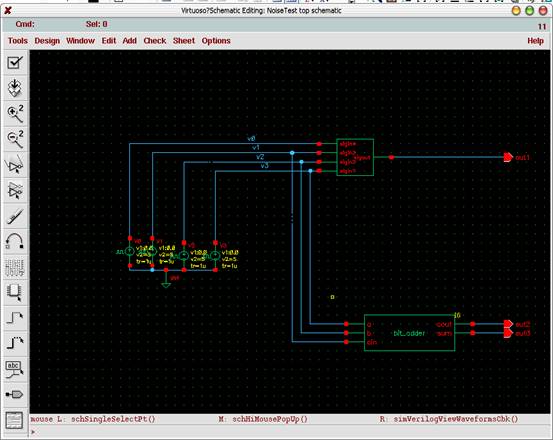

这个是cell:top的shematic,上面的模块是VerilogA的代码;下面的模块是verilog的

要对它进行混合仿真步骤:

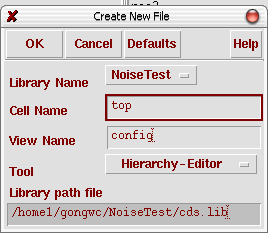

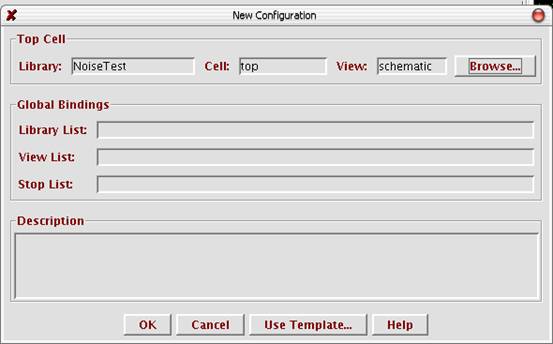

1.建立一个叫config的view

2. 选择top cell 为 top=>schematic

3. 点击“use template”按钮,选择仿真类型为spectreVerilog

一路ok下来,显示为

5.保存后关闭Hirachy Editor。重新打开config view,这时默认会打开schematic(你也可以打开Hirachy Editor编辑模块嵌套关系。)

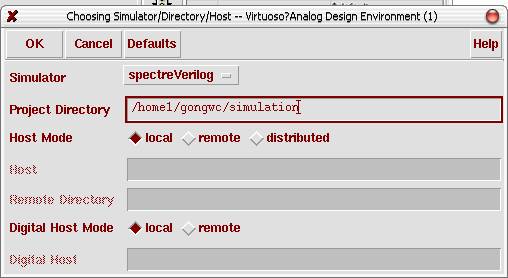

打开Analog Environment

6.选择setup=>simulator,将仿真器设置为spectreVerilog

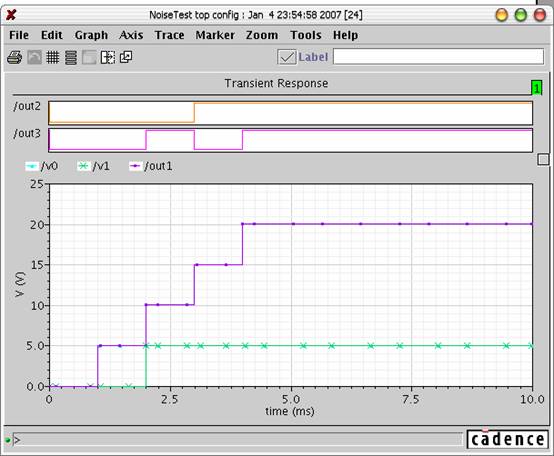

选择tran仿真,随便选几个线,输出波形如图,其中out2、out3为数字信号

数字、模拟的结果也可以分别通过result browser查看

―――――――――――――――――――

End

路径设置

首先要设置路径,可以这样设置(icfb 和ius和在一起了):

setenv ic50 /tools/cadence/ic5141

setenv ius58 /opt/cadence/ius58

set LD_LIBRARY_PATH = ( $ic50/tools/lib $ic50/tools/dfII/lib $

4000

ic50/tools/tcltk/tcl8.0/lib $ic50/tools/tcltk/tk8.0/lib ${ius58}/tools/verilog/lib $ius58/tools/lib $LD_LIBRARY_PATH)

set path = ( ${ius58}/tools/verilog/bin $ius58/tools/bin $ic50/tools/bin $ic50/tools/dfII/bin $ic50/tools/dracula/bin $path )

数字仿真

步骤:

1.在icfb中建立verilog 的view,(包括模块和testbench,testbench的view名也是verilog)

2.右键点击testbench的verilog view,选择“open(read-only)”

在verilog阅读窗的菜单上选择tools=>verilog-xl

Verilog-xl会被激活。

3.用verilog-xl仿真,试一试就会用了

仿真完成后View Waveform的按钮会被激活,

按这个按钮,simvision打开

Simvision的文档自己找一下cdsdoc吧

混合信号仿真

这个是cell:top的shematic,上面的模块是VerilogA的代码;下面的模块是verilog的

要对它进行混合仿真步骤:

1.建立一个叫config的view

2. 选择top cell 为 top=>schematic

3. 点击“use template”按钮,选择仿真类型为spectreVerilog

一路ok下来,显示为

5.保存后关闭Hirachy Editor。重新打开config view,这时默认会打开schematic(你也可以打开Hirachy Editor编辑模块嵌套关系。)

打开Analog Environment

6.选择setup=>simulator,将仿真器设置为spectreVerilog

选择tran仿真,随便选几个线,输出波形如图,其中out2、out3为数字信号

数字、模拟的结果也可以分别通过result browser查看

―――――――――――――――――――

End

相关文章推荐

- 基于Cadence_Allegro的高速PCB设计信号完整性分析与仿真

- Cadence 信号完整性(一)-- 仿真步骤4

- Cadence 信号完整性(一)-- 仿真步骤3

- Mixing digital audio 数字音频信号的混合

- Cadence 信号完整性(一)-- 仿真步骤1

- Cadence 信号完整性(一)-- 仿真步骤2

- Cadence 信号完整性(一)-- 仿真步骤3

- Excel数字、文本混合列导入SQL Server出现的问题&解决办法

- 在ASP.NET下实现数字和字符相混合的验证码(C# Code)

- 数字信号与模拟信号

- (模拟信号/数字信号)分别以(模拟信号/数字信号)中传输方式

- 《数据通信和网络》笔记--模拟信号和数字信号

- GEM5与SystemC混合仿真的实现

- ASP简单实现数字字符混合验证码

- Pandas剔除混合数据中非数字的数据

- 正则表达式:2到8个中文字符4到16个英文字符数字下划线,可混合

- 从模拟信号到数字信号

- 基于多项滤波的数字正交变换MATLAB仿真程序

- 强密码和弱密码并没有什么区别?NIST密码安全标准更新:不再建议密码要求混合大写字母、字符和数字

- 数字语音信号