计算机组成原理实验 单总线CPU设计(定长指令周期3级时序)(HUST)思路总结

计算机组成原理实验 单总线CPU设计(定长指令周期3级时序)(HUST)总结

全部任务共六关。主要涉及定长指令周期三级时序系统的设计,设计过程中比较重要的是数电知识、Logisim的组合逻辑电路分析功能和所给Excel表格的逻辑式自动生成。实验总体难度不难,操作有些麻烦,自己动手实现是挺有趣的。希望大家自己保持耐心、多多思考,顺利完成实验。

关于另一种变长指令单总线CPU的设计,可以参考

计算机组成原理实验 单总线CPU设计(变长指令周期3级时序)(HUST)思路总结

第1关 指令译码器设计

思路:利用比较器将指令字转换为译码信号。

注意:

1.指令字OP与不同信号的对应(查阅手册可知)

2.所给常量为16进制,转换时需注意

16进制:23 == 2进制: 00100011

3.SLT除对OP有要求外,对FUNC也有要求,考虑使用与门

其余只对OP有要求

第2、3关

思路:按照题目要求填表,再使用Logisim的组合逻辑电路分析功能即可。也可以直接在Logisim的组合逻辑电路分析功能填写真值表。

第4关 硬布线控制器组合逻辑单元设计

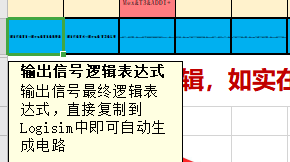

思路:同2、3,不过需要使用表达式进行Logisim的组合逻辑电路分析,表达式可以通过Excel自动生成

补充有几个比较特殊的:

注意:

1.Rs/Rt对应RegTgt

2.Excel表格默认31行(取指:4 + 计算执行:5*5)

3.填表后生成的公式直接复制表格内容(蓝色区域即是,直接右击复制,一定要点击输入)

4.此关十分考验耐心,特别是在复制填写公式阶段

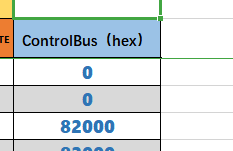

5.平台测试出错时可以通过比较ControlBus找出具体哪行出错

第5关 硬布线控制器设计

思路:按要求连接即可(比较简单,具体连接略)

注意:

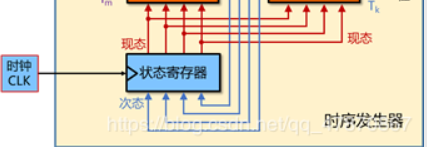

1.状态寄存器应设置为下降沿

2.状态寄存器Q端为现态输出,D端接受来自状态机的次态。

3.关于连接我再解释一下,其实连接的部件除了状态寄存器外都是前几关设计的。状态寄存器需要连接的有两个输入,一个输出。时钟CLK连en,D端接受来自状态机的次态(需加分线器),Q端输出分别连接状态机的现态和输出函数(同样需加分线器)。

4.关于状态机的输入输出注意分线器的使用

5.如果出现红线说明有连接错误

第6关 单总线CPU设计

思路:

最终联调,测试排序程序。在RAM中加载sort-5.hex程序,ctrl+k自动运行

注意:

1.最终终止条件为运行至0xbbb节拍停下,指令计数为251,注意最后一条指令是一条beq分支指令,会跳回当前指令继续执行,是死循环。

结果如图:

否则,可能前面设计出错。尤其可能是第4关 硬布线控制器组合逻辑单元设计。

2.可以调节频率以加快执行速度

- 计算机组成原理实验 单总线CPU设计(变长指令周期3级时序)(HUST)思路总结

- [置顶] [计算机组成原理][R-I-J型指令CPU设计实验总结]

- [计算机组成原理][实验十.R-I-J型指令CPU设计实验总结]

- 中山大学计算机组成原理多周期CPU实验

- 笔记|计算机组成原理运算器设计实验

- 用ModelSim、Mars和Verilog做计算机组成原理CPU实验注意事项

- 计算机组成原理课程设计实验一:验证74LS181运算和逻辑功能

- 计算机组成实验-第5章_R指令设计实现

- 计算机组成原理:时钟周期、机器周期和指令周期

- 计算机组成原理知识总结-总线

- 计算机组成原理——cpu的简单模型实验报告

- 计算机组成原理知识总结-控制器与CPU

- 计算机组成原理知识总结-指令系统

- 深入计算机组成原理(十八)建立数据通路(中):指令+运算=CPU

- 山东大学计算机组成原理实验课程设计-模型机

- 计算机组成原理实验--存储器读写与总线控制

- 华中科技进大学计算机组成原理存储器设计实验1-7

- 计算机组成原理运算器设计实验之4位快速加法器设计

- 计算机组成原理实验四:时序系统

- 计算机组成原理实验之CPU组成与指令周期实验