中断、DDR、LCD基础知识

DDR

sdram和sram区别在于,sdram的数据需要不断地刷新,以保持数据的不丢失

目前sdram技术已经发展到了第四代 分别为: SDRAM、 DDR SDRAM、 DDR2 SDRAM、 DDR3 SDRAM、 DDR4 SDRAM

关于sdram的内存大小计算,与地址线、数据线、bank线有关。比如 W9825G6KH 的 A0~A8 是列地址,一共 9 位列地址, 0~A12 是行地址,一共 13位,因此可寻址范围为: 2^9*2^13=4194304B=4MB, W9825G6KH 为 16 位宽(2 个字节),因此还需要对 4MB 进行乘 2 处理,得到 4*2=8MB,但是 W9825G6KH 一共有 4 个 BANK,所有总共是32MB。

DDR 全称是 Double Data Rate SDRAM,也就是双倍速率 SDRAM,看名字就知道 DDR的数据传输速率比 SDRAM 高 1 倍!这 1 倍的速度不是简简单单的将 CLK 提高 1 倍,SDRAM 在一个 CLK 周期传输一次数据, DDR 在一个 CLK 周期传输两次数据,也就是在上升沿和下降沿各传输一次数据,这个概念叫做预取(prefetch),相当于 DDR 的预取为 2bit,因此DDR 的速度直接加倍!

DDR2 的 IO 时钟是 DDR 的 2 倍,预取为4,因此 DDR 内核时钟依旧是 133~200MHz 的时候,总线速度就是 266~400MHz(DDR2内存每个时钟能够以4倍外部总线的速度读/写数据)。

DDR 对于硬件要求非常严格,因此微控制器中有关 DDR 的引脚都是独立的,一般没有复用功能。

根据规定,所有厂商的 DDR 芯片 IO 一摸一样,不管是引脚定义还是引脚间距,但是芯片外形大小可能不同。因此只要做好硬件,可以在不需要修改硬件 PCB 的前提下,随意的更换不同容量、不同品牌的 DDR 芯片。

中断

STM32 的中断系统主要有以下几个关键点:

①、 中断向量表。

②、 NVIC(内嵌向量中断控制器)。

③、 中断使能。

④、 中断服务函数。

概念介绍

1.中断向量表

中断向量表存放中断服务程序的入口地址或存放中断服务程序的首地址。这些中断服务程序(函数)在中断向量表中的位置是由半导体厂商定好的。当某个中断被触发以后就会自动跳转到中断向量表中对应的中断服务程序(函数)入口地址处。中断向量表在整个程序的最前面。

ARM 处理器都是从地址 0X00000000 开始运行的,但是我们学习 STM32 的时候代码是下载到 0X8000000 开始的存储区域中。由此引入了一个新的概念——中断向量表偏移,通过中断向量表偏移就可以将中断向量表存放到任意地址处

2、 中断向量控制器(NVIC、GIC)

Cortex-M 内核有个中断系统的管理机构—NVIC,Cortex-A 内核的中断管理机构不叫做NVIC,而是叫做 GIC,全称是 general interrupt controller

Cortex-A7 中断系统简介

Cortex-A7 一共有 8 个中断,而且还有一个中断向量未使用,实际只有 7 个中断。和 STM32F103 中断向量表比起来少了很多!难道一个能跑 Linux 的芯片只有这 7 个中断?这个就是 Cortex-A 和 Cotex-M 在中断向量表这一块的区别,对于 Cortex-M 内核来说,中断向量表列举出了一款芯片所有的中断向量,包括芯片外设的所有中断。对于 CotexA 内核来说并没有这么做,例如CortexA有个 IRQ 中断, Cortex-A 内核 CPU 的所有外部中断都属于这个 IQR 中断,当任意一个外部中断发生的时候都会触发 IRQ 中断。在 IRQ 中断服务函数里面就可以读取指定的寄存器来判断发生的具体是什么中断。

简单的说就是,A系列内核中断看起来很少,但是每个中断又包含了很多子中断,我们去判断寄存器就可以了。而M内核中断是全部列出来的。

当上图左侧这些中断中任意一个发生的时候 IRQ 中断都会被触发,所以我们需要在 IRQ 中断服务函数中判断究竟是左侧的哪个中断发生了,然后再做出具体的处理。

GIC控制器简介

GIC 是 ARM 公司给 Cortex-A/R 内核提供的一个中断控制器,类似 Cortex-M 内核中的NVIC。目前 GIC 有 4 个版本:V1~V4, V1 是最老的版本,已经被废弃了。 V2~V4 目前正在大量的使用。 GIC V2 是给 ARMv7-A 架构使用的,GIC V2 最多支持 8 个核的芯片。 ARM 会根据 GIC 版本的不同研发出不同的 IP 核,那些半导体厂商直接购买对应的 IP 核即可。

GIC 将众多的中断源分为分为三类:

①、 SPI(Shared Peripheral Interrupt),共享中断,顾名思义,所有 Core 共享的中断,这个是最常见的,那些外部中断都属于 SPI 中断(注意!不是 SPI 总线那个中断) 。比如按键中断、串口中断等等,这些中断所有的 Core 都可以处理,不限定特定 Core。

②、 PPI(Private Peripheral Interrupt),私有中断,我们说了 GIC 是支持多核的,每个核肯定有自己独有的中断。这些独有的中断肯定是要指定的核心处理,因此这些中断就叫做私有中断。

③、 SGI(Software-generated Interrupt),软件中断,由软件触发引起的中断,通过向寄存器GICD_SGIR 写入数据来触发,系统会使用 SGI 中断来完成多核之间的通信。

中断 ID

每一个 CPU 最多支持 1020 个中断 ID

ID0~ID15:这 16 个 ID 分配给 SGI。

ID16~ID31:这 16 个 ID 分配给 PPI。

ID32~ID1019:这 988 个 ID 分配给 SPI

LCD

1、分辨率

提起 LCD 显示器,我们都会听到 720P、 1080P、 2K 或 4K 这样的字眼;1080P 的意思就是一个 LCD 屏幕上的像素数量是1920*1080 个,也就是这个屏幕一列 1080 个像素点,一共 1920 列。同样的,分辨率不变的情况下, LCD 尺寸越小越清晰。比如我们常用的 24 寸显示器基本都是 1080P 的,而我们现在使用的 5 寸的手机基本也是 1080P 的,但是手机显示细腻程度就要比 24 寸的显示器要好很多。

2.LCD 时间参数

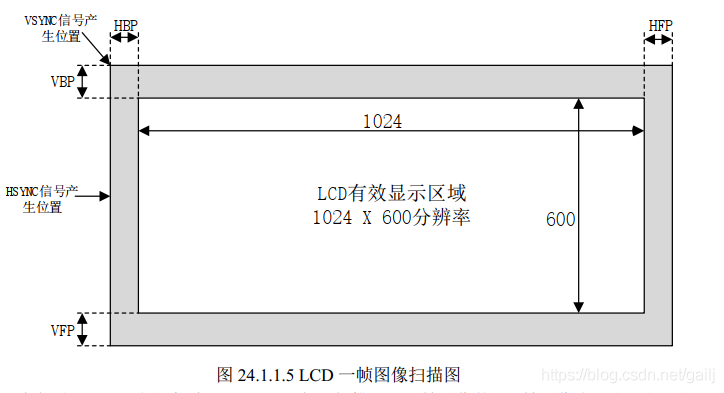

HSYNC 是水平同步信号,也叫做行同步信号,当产生此信号的话就表示开始显示新的一行了。 VSYNC 信号是垂直同步信号,也叫做帧同步信号。

当显示完一行以后会发出 HSYNC 信号,此时电子枪就会关闭,然后迅速的移动到屏幕的左边,当 HSYNC 信号结束以后就可以显示新的一行数据了,电子枪就会重新打开。在 HSYNC信号结束到电子枪重新打开之间会插入一段延时,这段延时就图 中的 HBP。当显示完一行以后就会关闭电子枪等待 HSYNC 信号产生,关闭电子枪到 HSYNC 信号产生之间会插入一段延时,这段延时就是图中的 HFP 信号。同理,当显示完一帧图像以后电子枪也会关闭,然后等到 VSYNC 信号产生,期间也会加入一段延时,这段延时就是图中的 VFP。VSYNC 信号产生,电子枪移动到左上角,当 VSYNC 信号结束以后电子枪重新打开,中间也会加入一段延时,这段延时就是图中的 VBP。

3.像素时钟(带宽)

显示一帧图像所需要的时钟数就是像素时钟。可以粗略的计算,1080P,1920*1080*60帧 大约是124MHz

4.显存

如果采用 ARGB8888 格式的话一个像素需要 4 个字节的内存来存放像素数据,那么 1024*600 分辨率就需要1024*600*4=2457600B≈2.4MB 内存。但是LCD 内部是没有内存的,所以就需要在开发板上的 DDR3 中分出一段内存作为 LCD 屏幕的显存

- Java基础知识---线程的中断

- UC/OS-II基础知识之中断

- LCD图像显示基础知识

- ARM中断基础知识

- tiny4412学习(四)之移植linux-设备树(1)设备树基础知识及GPIO中断【转】

- LCD相关基础知识

- Java并发(基础知识)—— Java中断机制

- STM基础知识-中断

- LCD基础知识

- ucosii关于PC的中断基础知识

- Java基础知识强化16:深入分析Java线程中断机制

- java基础知识回顾之java Thread类学习(十二)-- 线程中断

- lcd基础知识

- Java并发基础知识(内存栅栏+volatile+synchronized详解+java锁优化+wait notify+AbstractQueuedSynchronizer详解+线程中断)

- ARM基础知识教程(三):ARM中异常中断的种类

- QHD/qHD/FHD等LCD基础分辨率知识普及

- tiny4412学习(四)之移植linux-设备树(1)设备树基础知识及GPIO中断

- LCD 基础知识篇3

- LCD驱动程序——基础知识

- LCD的一些基础知识