Verilog与FPGA数字系统设计学习笔记(一)——EDA技术概述与fpga概述

第一章 EDA技术概述与fpga概述

本笔记是我在大三时期(2019年)学习fpga与verilog的学习笔记,在此首先感谢西北工业大学航海学院刘建国老师对我的教学与学习过程中的支持与关注,在此十分感谢!

本文仅为概述与学习笔记,仅为个人学习所用。

1 EDA技术

EDA技术,电子设计自动化缩写(Electronics Design Automation),以计算机为平台,以EDA软件工具为开发环境,以PLD器件或者ASIC专用集成电路为目标器件设计实现电路系统的一种技术。使用EDA技术,用户只进行完成硬件设计文件,其余设计由计算机完成。

- IP(Intellectual Property)核在电子设计领域得到了广泛的应用,IP核就是知识产权或知识产权模块意思,也定义为用于ASIC或FPGA中的预先设计好的电路功能模块。IP核分为软IP,固IP,硬IP。

- SoPC(System on Programmable Chip,可编程芯片系统)步入实用化阶段。

- EDA技术有了更完备的库与开发环境,开放性与标准化得以提升,使我们开发拥有较好的环境。

2 Top-down设计与IP核复用

Top-down设计:自顶而下,经过“设计-验证-修改设计-验证”,不断反复,直到达到平衡,先按照产品的相关功能需求设计出架构,在逐步分析。

Bottom-up设计:即自底向上的设计,先设计各个元件,调用设计库中的元件(如各种门电路、加法器、计数器等) ,设计组合出满足自己需要的系统。

IP核复用:IP核分为软IP,固IP,硬IP,软IP是用vhdl等硬件描述的语言描述的功能块。固IP是完成了综合的功能块。硬IP硬件设计的最终产品,比如掩膜。IP复用是指对系统中的某些模块调用设计好的IP核来实现,不用设计所有模块。

IP核具有规范的接口协议,良好的可移植性与可测试性,为系统开发提供了可靠的保证。

3 系统设计流程

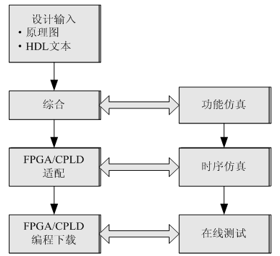

图3-1 基于fpga/cpld数字系统设计流程

- 输入:原理图输入/硬件描述语言(HDL文本输入)

- 综合:将较高层次的设计转化为较低层次的描述过程,包括:

行为综合,从算法表示,行为描述转到寄存器传输级(RTL);

逻辑综合,RTL级转化到逻辑门级(包括触发器)

版图综合/结构综合,从逻辑门表示转换到版图表示,或转换到PLD器件的配置网表表示.

综合使用的工具是综合器,可以将原理图或HDL语音描述的功能转化为电路网表的工具。如:synplify 。综合器是将硬件描述语言转化为电路网表设计文件,而编译器是将c/c++等程序文件,转化为cpu二进制代码。

- 仿真:包括功能仿真与时序仿真。

- 编程配置:把编程文件装入到PLD器件。

4 常用的EDA

图4-1 集成的FPGA/CPLD开发工具

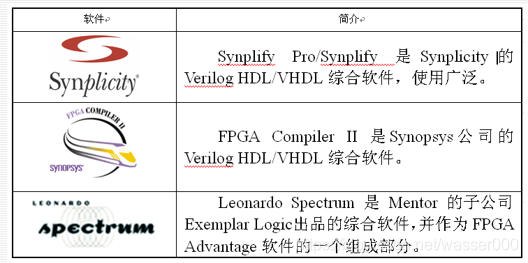

图4-2 逻辑综合器

图4-3 仿真工具

5 FPGA/CPLD概述

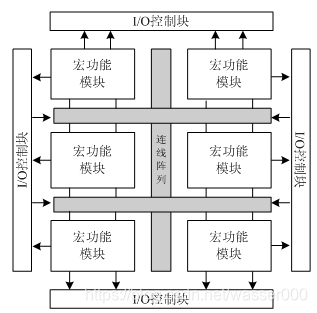

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物,作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

CPLD(Complex Programmable Logic Device),复杂可编程逻辑器件,是从PAL和GAL器件发展出来的器件,相对而言规模大,结构复杂,属于大规模集成电路范围。是一种用户根据各自需要而自行构造逻辑功能的数字集成电路。其基本设计方法是借助集成开发软件平台,用原理图、硬件描述语言等方法,生成相应的目标文件,通过下载电缆(“在系统”编程)将代码传送到目标芯片中,实现设计的数字系统。集成度与功耗均比fpga要大。

图5-1 CPLD结构(举例)

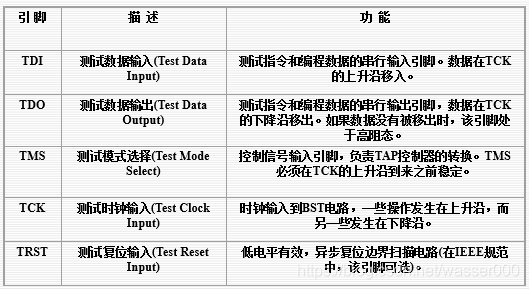

边界扫描测试技术:为了解决超大规模集成电路(VLSI)的测试问题,自1986年开始,IC领域的专家成立了“联合测试行动组”(JTAG,Joint Test Action Group),并制定出了IEEE 1149.1边界扫描测试(BST,Boundary Scan Test)技术规范。

图5-2 边界扫描技术

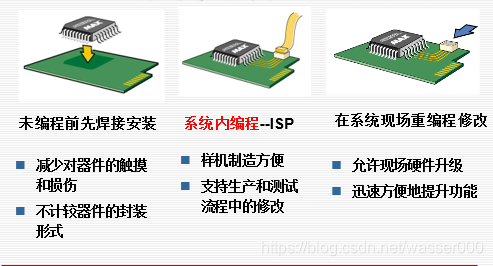

图5-3 编程与配置

F 7ff7 PGA编程时可以使用JTAG方式在线编程,JTAG(Joint Test Action Group)联合测试行动小组)是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。基本原理是在器件内部定义一个TAP(Test Access Port?测试访问口)通过专用的JTAG测试工具对进行内部节点进行测试。

标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。标准的JTAG接口是4线:TMS、 TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。

- [转]Verilog数字系统设计教程(大连理工一博士学习笔记)

- 【verilog】Verilog数字系统设计教程学习笔记(夏宇闻)《一》

- 《AIX 5L 系统管理技术》学习笔记之第一章AIX操作系统概述

- 系统分析与设计学习笔记(一)UML概述

- 操作系统精髓与设计原理学习笔记一:计算机系统概述

- RRC 25.331协议学习笔记二:系统消息概述

- 我脑残实验室Verilog学习笔记——在Xilinx ISE中运用符号设计顶层模块的方法

- 20125337——信息安全系统设计基础第五周学习笔记

- [学习笔记]UML小结以及基于领域模型的系统设计初步

- 黑马程序员_学习笔记:3) 面向对象1:概述、封装、this、static、单例设计模式

- 六、机器学习系统设计笔记之分类II情感分析

- 用verilog设计一数字钟系统

- 系统设计与架构笔记:对我新公司网站的技术架构初解

- C/C++学习笔记26:(一)C文件系统概述

- MySQL学习笔记_1_MySQL数据库管理系统概述

- 信息安全系统设计基础 第5周学习笔记

- (笔记)电路设计(十二)之高速数字系统滤波电容的设计应用

- Java核心技术学习笔记—— 卷一 第一章:Java程序设计概述

- 信息安全系统设计基础 第二周学习笔记

- 交互设计学习笔记之《如何设计帮助系统》【交互设计】