深入理解计算机系统第6章 存储器层次结构

第6章 存储器层次结构

6.1存储技术

1.以传统DRAM为例,简要介绍DRAM存储。

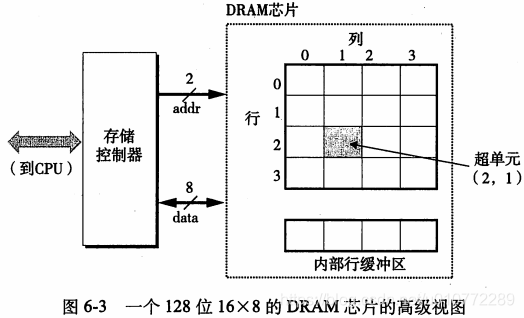

DRAM芯片中国的单元被分成d个超单元,每个超单元都有w个DRAM单元组成,总共存储了dw位信息。超单元被组织成r行c列的长方形阵列,这里rc=d。每个超单元有形如(i,j)的地址,这里i表示行,j表示列。

图6-3展示的是一个16*8的DRAM芯片的组织,有d=16个超单元,每个超单元有w=8位,r=4行,c=4列。带阴影的方框表示地址(2,1)处的超单元。信息通过外接的引脚流入和流出芯片。每个引脚携带一个1位的信号。图6-3给出了两组引脚: 8个data引脚,它们能传送一个字节到芯片或从芯片传出一个字节,以及2个addr引脚,它们携带2位的行和列超单元地址。

每个DRAM芯片被连接到某个叫做存储控制器的电路,这个电路可以一次传送w位到每个DRAM芯片或一次从每个DRAM芯片传出w位。为读出超单元(i,j)的内容,存储控制将行地址i发送到DRAM,然后是列地址j。

例如要从图6-3中16*8的DRAM中读出超单元(2,1),存储控制器发送行地址2。DRAM的响应是将行2的整个内容都拷贝到一个内部行缓冲区。接下来,存储控制器发送列地址1,DRAM的响应是从行缓冲区拷贝出单元(2,1)中的8位,并把它们发送到存储控制器。

2.访问主存

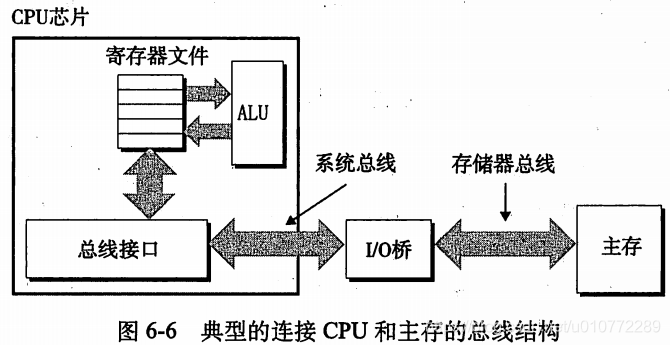

数据流通过总线在处理器和DRAM主存之间来来回回。读事务是从主存传送数据到CPU,写事务是从CPU传送数据到主存。

总线是一组并行的导线,能携带地址、数据和控制信号。

图6-6展示了一个示例计算机系统的配置。主要部件是CPU芯片、I/O桥的芯片组(其中包括存储控制器),以及组成主存的DRAM存储器模块。这些部件是由一堆总线连接起来,系统总线连接CPU和I/O桥,存储器总线连接I/O桥和主存。

当CPU执行一个下面这样的加载操作时会发生什么:

movl A, %eax

这里,地址A的内容被加载到寄存器%eax。首先,CPU将地址A放到系统总线上。I/O桥将信号传递到存储器总线。其次,主存从存储器总线读地址,从DRAM取出数据字,并将数据写到存储器总线。I/O桥将存储器总线信号翻译成系统总线信号,然后沿着系统总线传递。最后,CPU从总线上读数据,并将数据拷贝到寄存器%eax。

3.磁盘存储

当操作系统要执行一个I/O操作时,例如读一个磁盘扇区的数据到主存,操作系统会发送一个命令到磁盘控制器,让它读某个逻辑块号。控制器上的固件执行一个快速表查找,将一个逻辑块号翻译成一个(盘面,磁道,扇区)的三元组,这个三元组唯一的标识了对应的物理扇区,控制器上的硬件解释这个三元组,将读/写头移动到适当的柱面,等到扇区移动到读/写头下,将读/写头感知到的位放到控制器上的一个小缓冲区中,然后将它们拷贝到主存中。

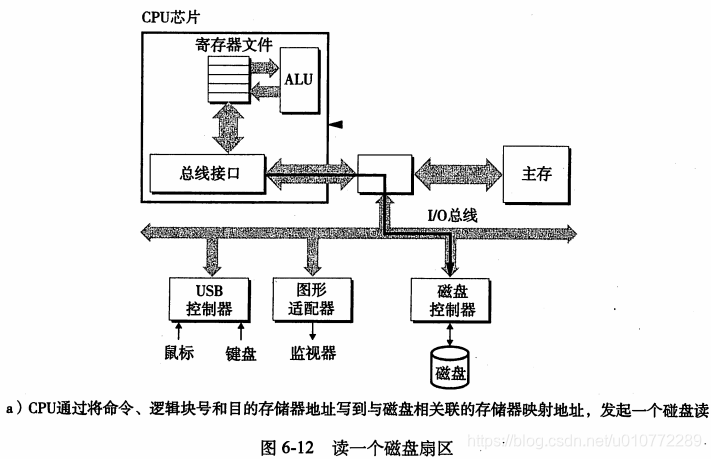

4.访问磁盘

CPU使用存储器映射I/O技术来向I/O设备发出命令。在使用存储器映射I/O的系统中,地址空间中有一块地址是为与I/O设备通信保留的。每个这样的地址称为一个I/O端口。当一个设备映射到总线时,它与一个或多个端口相关联(或它被映射到一个或多个端口)。

简单举例,假设磁盘控制器被映射到端口0xa0。

- CPU可能通过三个对地址0xa0的存储指令,发起磁盘读。

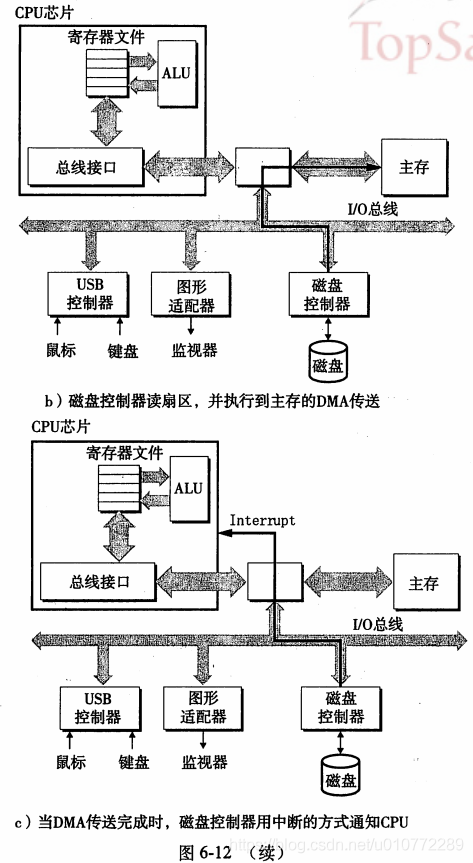

- 在磁盘控制器收到来自CPU的读命令后,它将逻辑块号翻译成一个扇区地址,读该扇区的内容,然后将这些内容直接传送到主存,不需要CPU的干涉(见图6-12b)。这种传送称为DMA传送。

- DMA传送完成,磁盘扇区的内容被安全地存储在主存中之后,磁盘控制器给CPU发送一个中断信号来通知CPU。(该进程在读取期间是被阻塞的,读完成后,磁盘控制器的中断使进程上下文切换,该进程继续运行)

6.2 局部性

一个编写良好的计算机程序常常具有良好的局部性,也就是它们倾向于引用临近于其他最近引用过的数据项的数据项,或者最近引用过的数据项本身。这种倾向性,称为局部性原理。

局部性通常有两种不同的形式: 时间局部性和空间局部性。在一个具有良好时间局部性的程序中,被引用过一次的存储器位置很可能在不远的将来再被多次引用。在一个具有良好空间局部性的程序中,如果一个存储器位置被引用了一次,那么程序很可能在不远的将来引用附近的一个存储器位置。

有良好局部性的程序比局部性差的程序运行的更快。局部性原理允许计算机通过高速缓存存储器来保存最近被引用的指令和数据项,从而提高对主存的访问速度。

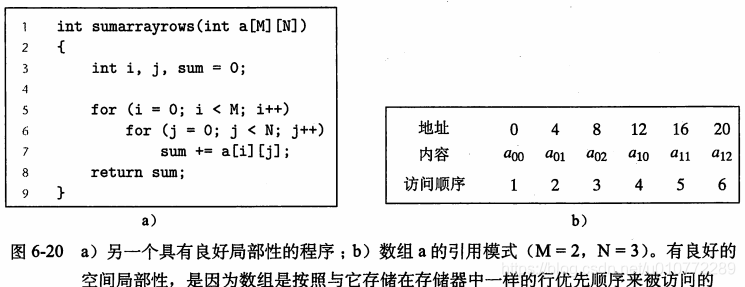

函数sumarrayrows具有良

4000

好的空间局部性,因为它按照数组被存储的行优先顺序来访问这个数组。但其时间局部性较差,因每个元素只被访问一次。

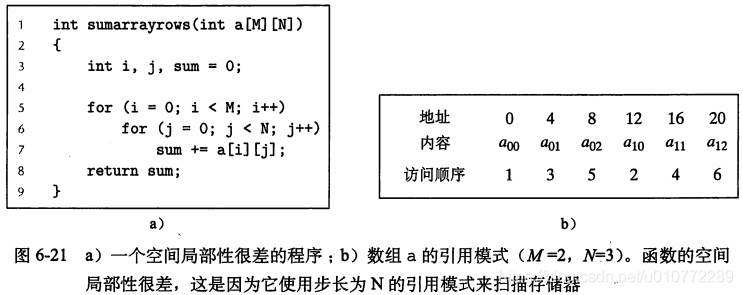

函数sumarraycols的空间局部性很差,因为它按照列顺序来扫描数组,而不是按照行顺序。因为C数组在存储器中是按照行顺序来存放的。

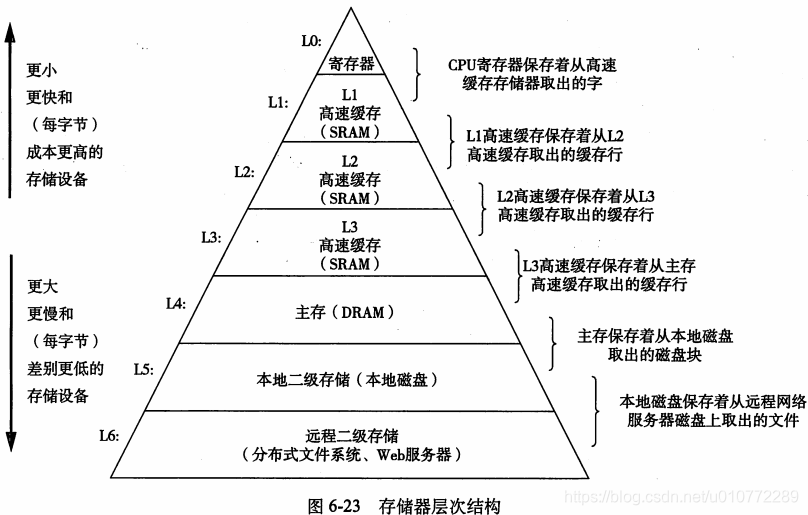

6.3 存储器层次结构

- 深入理解计算机系统(1)—— 系统硬件组成与存储器层次结构

- 深入理解计算机系统——存储器层次结构

- 9、深入理解计算机系统笔记:存储器层次结构,高速缓存存储器(1)

- 深入理解计算机系统第六章--存储器层次结构与性能

- 7、深入理解计算机系统笔记:存储器层次结构,存储技术(2)

- 10、深入理解计算机系统笔记:存储器层次结构,高速缓存存储器(2)

- 深入理解计算机系统--存储器层次结构

- 11、深入理解计算机系统笔记:存储器层次结构,利用局部性

- 深入理解计算机系统——第06章——存储器层次结构

- 深入理解计算机系统之存储器层次结构

- 深入理解计算机系统:存储器层次结构

- 6、深入理解计算机系统笔记:存储器层次结构,存储技术(1)

- 8、深入理解计算机系统笔记:存储器层次结构,局部性

- 深入理解计算机系统 1.6 存储设备形成层次结构

- 计算机系统:第6章(存储器层次结构)

- 深入理解计算机系统结构——并发编程

- 深入理解计算机系统(3.8)---数组、异质结构以及指针的详解(十分重要)(难度较高)【呕心沥血版】

- 深入理解计算机系统(第二版)----之一:(一:程序的结构和执行)计算机系统漫游

- 深入理解计算机系统(3.8)---数组、异质结构以及指针的详解(十分重要)(难度较高)【呕心沥血版】

- 你真的深入理解计算机系统了吗之篇章三:程序的结构