关于quartus和modelsim联合仿真中预编译库文件,减少仿真时间的方法

2016-01-19 11:35

891 查看

关于quartus和modelsim联合仿真中预编译库文件,减少仿真时间的方法

2016年1月19日

9:55

一、首先存在的问题:

使用quartus调用modelsim进行功能仿真或时序仿真时,是先执行altera../simulation/modelsim/中的.do文件,.do文件不能具备“只读”属性,否则无法打开modelsim软件。也就是说,调用打开modelsim后,默认通过执行.do文件,将quartus中的源文件进行编译并建立波形文件。

然而,自动生成的.do每次执行(修改)前,会产生.Bak备份文件,因此不论怎样修改.do中的内容,每次联合调用执行modelsim时,.do中被修改的部分都会恢复原状,以保证.do中的代码不被篡改。

而.do文件中对库文件的执行包括两大部分:

(1)创建、映射、编译生成8个库文件,如下

altera_lnsim_ver、 altera_mf_ver、

altera_ver、 cyclonev_hssi_ver、 cyclonev_pcie_hip_ver、

cyclonev_ver、 lpm_ver、sgate_ver

(2) 创建、映射、编译设计的源文件,本例(我的工程文件)中如下wptr_full.v、rptr_empty.v、tbfifo.v、fifo_asyn.v、fifomen.v、syne_w2r.v、sync_r2w.v

其中最耗费时间的是 (1)部分,极大部分时间发生在对 (1) 的编译上,而且在第一次调用modelsim编译库文件后。第二次再调用时,仍然会重复上一次的步骤,重复创建、编译并覆盖第一次的库文件。所以每次都会浪费很多时间。

二、解决方案:

针对发现的问题,解决方案其实就是在绕过执行默认的FIFO.do文件,同时,将所需的8个库文件预先编译好,并将映射路径添加到modelsim.ini配置文件中。

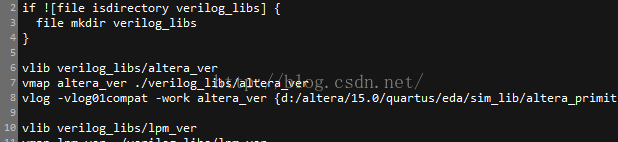

创建、映射、编译所需的8个库文件

以altera_ver为例

(1) 在modeltech64_10.1c根目录下,创建altera文件夹,后面有用。

(2) 去掉modeltech64_10.1c根目录下的modelsim.ini的只读属性。

(3) 在modelsim中,依次点击File-Change

Directory,选择根目录modeltech64_10.1c-altera(刚创建的),点击确定。

(4)依次点击File-New-Library,选中a

new library and a logical mapping to it,Liberay Name和Liberay

Physical Name都填写altera_ver

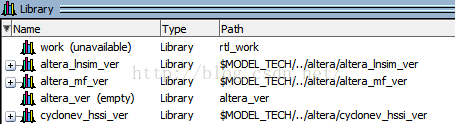

此时,altera_ver还是空的(empty)

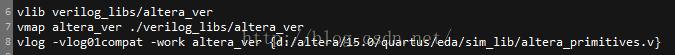

(5) 点击Compile-Compile…,在弹出的Complie

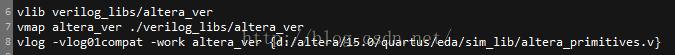

sources file的Library中选择altera_ver,查找范围选d:/altera/15.0/quartus/eda/sim_lib/选择altera_primitives.v,需要编译的文件在FIFO.do文件中有对应。

(读者可自行下载 UltraEdit软件打开FIFO.do文件查看)在下面的文件类型中,如果你的设计采用的是verilog,则选择verilog

file;如果是Vhdl,则采用VHDL File。点击compile,完成后点击Done。

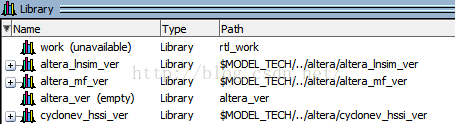

修改modelsim.ini文件

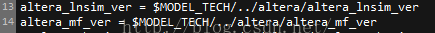

(1) 用UltraEdit打开modeltech64_10.1c目录下的modelsim.ini文件,用Ctrl+F查找altera_ver,会找到altera_ver

= altera_ver,

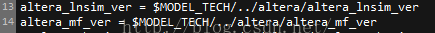

按照图中的格式改写为altera_ver= $MODEL_TECH/../altera/altera_ver,保存退出

(2) 将modelsim.ini文件修改为“只读”属性

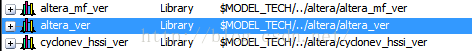

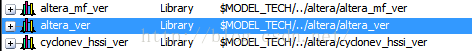

(3) 重新打开modelsim软件后,会看到

这样,以后不管将Change Directory修改到哪里,都能从modelsim.ini中找到编译好的

altera_ver库

说明添加库部分已经完成了。

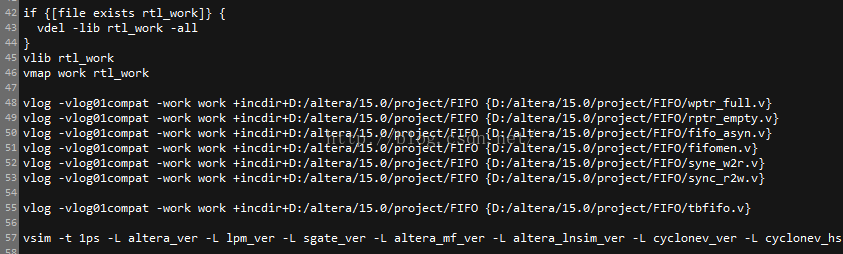

修改.do文件

(1) 用UltraEdit打开你在quartus中建立工程下的.do文件,以我的为例:\FIFO\simulation\modelsim下的FIFO_run_msim_rtl_verilog.do,FIFO是工程所在的文件夹。

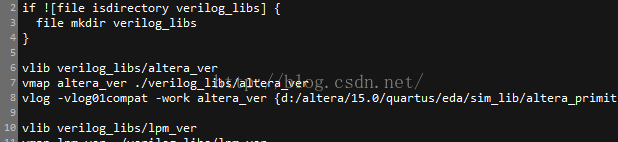

(2) 新建一个文件,将首句transcript on复制进新文件中,中间编译8个库的部分不管

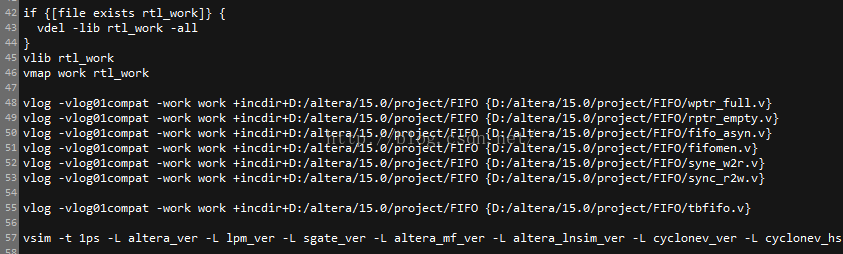

再将下面的部分,复制到新的文件中

一直到最后的部分,因为这部分是对你设计的代码的编译,文件另存为sim.do文件。注意保存在和FIFO_run_msim_rtl_verilog.do的同一级目录下。

验证部分

每次需要仿真时,不用quartus调用modelsim,而是直接打开modelsim,修改File-Change

Directory 到\FIFO\simulation\modelsim,在transcript中使用命令do

sim.do就会进行仿真了。

时间非常快,因为此时只编译你设计的代码!

方案存在的缺点:

(1) 有时候,你会发现几即便Library中没有那8个库文件,直接执行sim.do,仿真依然能进行,波形也正确。这是因为你的verilog代码中没有调用到altera的IP核。

(2) 当你以后需要仿真新的工程时,需要先用quartus调用modelsim软件,这个过程会自动产生.do文件,然后再执行步骤3,创建sim.do文件,执行步骤四修改默认工作文件夹。

三、其他解决方案:

我一师兄使用modelsimaltera仿真软件,就没那么多烦恼,库文件在第一调用仿真后,后面再次调用modelsimaltera时,就不会重复编译库文件,而是直接编译你的设计代码,时间非常快。

2016年1月19日

9:55

一、首先存在的问题:

使用quartus调用modelsim进行功能仿真或时序仿真时,是先执行altera../simulation/modelsim/中的.do文件,.do文件不能具备“只读”属性,否则无法打开modelsim软件。也就是说,调用打开modelsim后,默认通过执行.do文件,将quartus中的源文件进行编译并建立波形文件。

然而,自动生成的.do每次执行(修改)前,会产生.Bak备份文件,因此不论怎样修改.do中的内容,每次联合调用执行modelsim时,.do中被修改的部分都会恢复原状,以保证.do中的代码不被篡改。

而.do文件中对库文件的执行包括两大部分:

(1)创建、映射、编译生成8个库文件,如下

altera_lnsim_ver、 altera_mf_ver、

altera_ver、 cyclonev_hssi_ver、 cyclonev_pcie_hip_ver、

cyclonev_ver、 lpm_ver、sgate_ver

(2) 创建、映射、编译设计的源文件,本例(我的工程文件)中如下wptr_full.v、rptr_empty.v、tbfifo.v、fifo_asyn.v、fifomen.v、syne_w2r.v、sync_r2w.v

其中最耗费时间的是 (1)部分,极大部分时间发生在对 (1) 的编译上,而且在第一次调用modelsim编译库文件后。第二次再调用时,仍然会重复上一次的步骤,重复创建、编译并覆盖第一次的库文件。所以每次都会浪费很多时间。

二、解决方案:

针对发现的问题,解决方案其实就是在绕过执行默认的FIFO.do文件,同时,将所需的8个库文件预先编译好,并将映射路径添加到modelsim.ini配置文件中。

创建、映射、编译所需的8个库文件

以altera_ver为例

(1) 在modeltech64_10.1c根目录下,创建altera文件夹,后面有用。

(2) 去掉modeltech64_10.1c根目录下的modelsim.ini的只读属性。

(3) 在modelsim中,依次点击File-Change

Directory,选择根目录modeltech64_10.1c-altera(刚创建的),点击确定。

(4)依次点击File-New-Library,选中a

new library and a logical mapping to it,Liberay Name和Liberay

Physical Name都填写altera_ver

此时,altera_ver还是空的(empty)

(5) 点击Compile-Compile…,在弹出的Complie

sources file的Library中选择altera_ver,查找范围选d:/altera/15.0/quartus/eda/sim_lib/选择altera_primitives.v,需要编译的文件在FIFO.do文件中有对应。

(读者可自行下载 UltraEdit软件打开FIFO.do文件查看)在下面的文件类型中,如果你的设计采用的是verilog,则选择verilog

file;如果是Vhdl,则采用VHDL File。点击compile,完成后点击Done。

修改modelsim.ini文件

(1) 用UltraEdit打开modeltech64_10.1c目录下的modelsim.ini文件,用Ctrl+F查找altera_ver,会找到altera_ver

= altera_ver,

按照图中的格式改写为altera_ver= $MODEL_TECH/../altera/altera_ver,保存退出

(2) 将modelsim.ini文件修改为“只读”属性

(3) 重新打开modelsim软件后,会看到

这样,以后不管将Change Directory修改到哪里,都能从modelsim.ini中找到编译好的

altera_ver库

说明添加库部分已经完成了。

修改.do文件

(1) 用UltraEdit打开你在quartus中建立工程下的.do文件,以我的为例:\FIFO\simulation\modelsim下的FIFO_run_msim_rtl_verilog.do,FIFO是工程所在的文件夹。

(2) 新建一个文件,将首句transcript on复制进新文件中,中间编译8个库的部分不管

再将下面的部分,复制到新的文件中

一直到最后的部分,因为这部分是对你设计的代码的编译,文件另存为sim.do文件。注意保存在和FIFO_run_msim_rtl_verilog.do的同一级目录下。

验证部分

每次需要仿真时,不用quartus调用modelsim,而是直接打开modelsim,修改File-Change

Directory 到\FIFO\simulation\modelsim,在transcript中使用命令do

sim.do就会进行仿真了。

时间非常快,因为此时只编译你设计的代码!

方案存在的缺点:

(1) 有时候,你会发现几即便Library中没有那8个库文件,直接执行sim.do,仿真依然能进行,波形也正确。这是因为你的verilog代码中没有调用到altera的IP核。

(2) 当你以后需要仿真新的工程时,需要先用quartus调用modelsim软件,这个过程会自动产生.do文件,然后再执行步骤3,创建sim.do文件,执行步骤四修改默认工作文件夹。

三、其他解决方案:

我一师兄使用modelsimaltera仿真软件,就没那么多烦恼,库文件在第一调用仿真后,后面再次调用modelsimaltera时,就不会重复编译库文件,而是直接编译你的设计代码,时间非常快。

相关文章推荐

- ThreadLocal可能引起的内存泄露

- BaseAnimation是基于开源的APP,致力于收集各种动画效果(最新版本1.3)

- iOS app界面设计规范

- 2015年阿里工作与生活回顾

- count group by 组合用法

- hadoop1.2.1伪分布模式配置

- LIB和DLL的区别与使用

- Objectness 理解,整理及总结

- 【Akka】Akka中actor的生命周期与DeathWatch监控

- 【C语言天天练(十五)】字符串输入函数fgets、gets和scanf

- android学习笔记

- WEB应用中的SESSION知多少?

- bean之间赋值

- linux下gcc编译conio.h问题

- 实现不同交换机相同VLAN通信(TRUNK)

- array_diff的参数前后循序的区别

- FatMouse's Speed--hdu1160(dp+输出路径)

- 对IXP的一些思考

- iOS提交应用至APP Store流程

- FLV封装原理